NVMe控制器技术对于学者而言可能既困难又昂贵。现在,新的开源选项可以帮助EE学生为新的存储设备制作原型。

在7月的2020 USENIX年度技术会议(USENIX ATC)上,韩国高级科学技术研究院(KAIST)的电气工程师宣布了一种名为OpenExpress的可免费使用的新NVMe控制器技术。

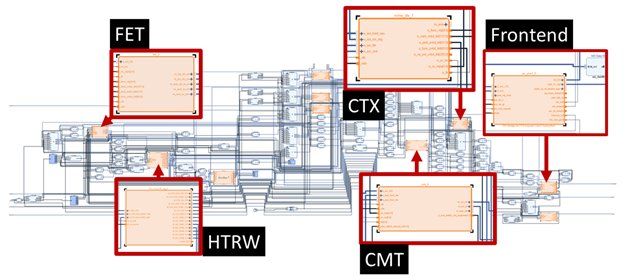

OpenExpress的主要硬件IP内核。图片由KAIST的Myoungsoo Jung教授提供

他们说,这项技术有潜力帮助学术研究人员开发更快的存储设备,而不会消耗他们的预算。KAIST团队解释说,这项技术为研究人员提供了一个开放源代码硬件框架来开发NVMe设备。

非易失性内存Express(NVMe)

研究称,NVMe被广泛的存储和非易失性存储器子系统用作快速I / O通信接口。

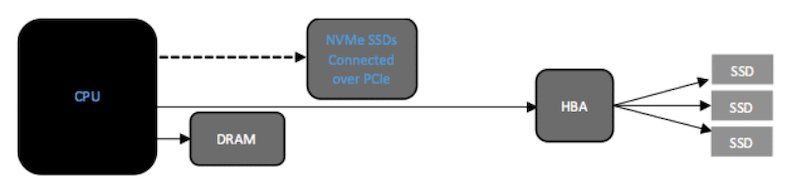

它是为基于外围组件互连-表达(PCI-E)接口的高性能存储设备而设计的,旨在替代串行AT附件(SATA)协议。SATA是为处理硬盘驱动器(HDD)上的数据而开发的,在固态驱动器(SSD)中的性能不足。

PCle接口连接CPU和SSD。图片由Western Digital提供

与使用SATA相比,固态硬盘中的数据处理速度几乎快六倍,因此NVMe迅速成为超高速和大容量数据处理的首选协议。它还用于各种基于闪存的信息存储设备中。

学术界对NVMe控制器的短缺

工业界通过为高速NVMe控制器保护自己的知识产权(IP)来利用它,并探索NVMe存储卡对软件堆栈的挑战。但是,对于学术界而言,NVMe控制器IP并不广泛,因为,也许可以理解,科技公司渴望保护它。

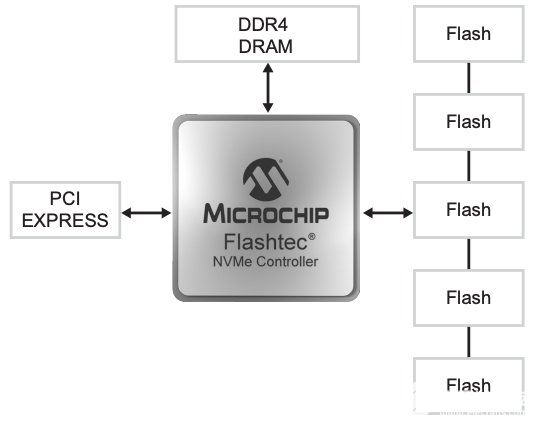

商用NVMe控制器的示例—在本例中为Microchip的16通道第4代PCIe闪存控制器。图片由Microchip提供

尽管研究界有充分的理由要求开放源代码硬件框架为NVMe设备构建新的控制器。尽管有少数公司确实提供访问权限,但是它的价格很高,可以很容易地扩展到每月六个数字。

适用于大学的开源NVMe控制器技术

为了解决这个问题,KAIST的研究团队开发了NVMe控制器技术,该技术以硬件自动化的形式实现了SSD的并行数据处理。

该控制器由一系列基本硬件IP和关键的NVMe IP内核组成。为了证明其性能,该团队使用OpenExpress(OE)构建了NVMe硬件控制器原型,并设计了OE提供的所有逻辑以使其在高频下运行。

新技术的原型板和OpenExpress平面图。图片由KAIST的Myoungsoo Jung教授提供

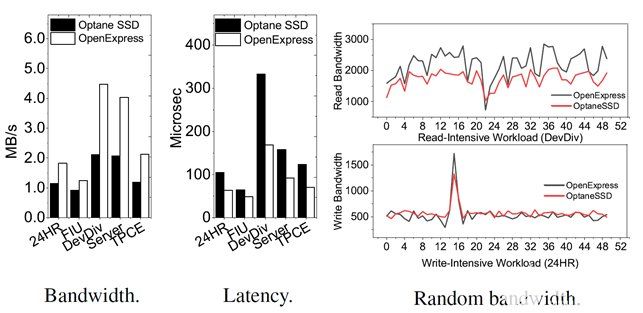

使用OE开发的现场可编程门阵列(FPGA)表现出更高的I / O数据处理能力,支持高达7 Gbps的带宽。研究人员声称,与英特尔的新型Optane SSD相比,FPGA还显示出76%的带宽增加和68%的I / O延迟降低。

与英特尔的Optane SSD相比,使用OpenExpress构建的FPGA的度量标准。图片由KAIST的Myoungsoo Jung教授提供

从理论上讲,这使其适合研究超高速和大容量存储设备。

根据OE开源最终用户协议,所有大学和研究机构均可免费使用和修改NVMe控制器以用于非商业用途。这对于研究与NVMe控制器兼容的下一代存储设备非常有用。

发布评论请先 登录

相关推荐

SSM框架的源码解析与理解

存储技术未来演进:NVMe over Fabrics (NVMeoF)

[译]OpenExpress:面向未来快速NVMe设备的开源研究框架

[译]OpenExpress:面向未来快速NVMe设备的开源研究框架

评论