AXI4交换机制

接口与互联

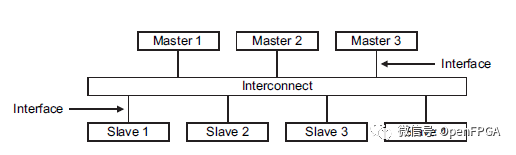

一个典型的系统主要是由一个主设备和从设备连接组成的,它们通过某种形式的互连组合在一起,如图4‑29所示。

图4‑29 接口和互联

AXI协议提供了一个单独的接口定义来描述接口:

l主设备和互连之间

l从设备和互联之间

l主设备和从设备之间。

上述接口定义使各种不同的互连易于表达。设备之间的互联,与其他具有对称的主端口和从端口设备一样,可以连接真正的主设备和从设备。

大多数系统采用如下三种互连的方式之一:

l共享地址和数据总线

l共享地址总线和多个数据总线

l拥有多个地址和数据总线的多层互联。

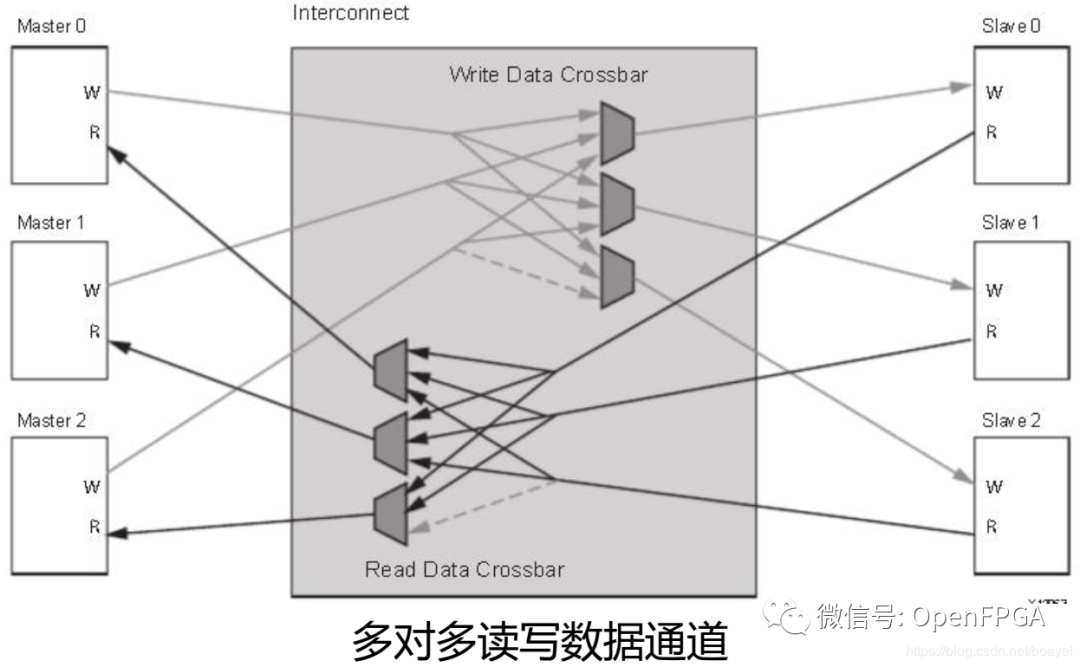

在大多数系统中,地址的通道的带宽需求明显小于数据通道带宽的需求。这种系统能在系统运行和复杂度之间实现良好平衡,而复杂度主要由于使用共享地址总线和多个数据总线互联方式去使能数据并行传输而导致的。

从上面可以看出,AXI 协议严格的讲是一个点对点的主从接口协议,当多个外设需要互相交互数据时,我们需要加入一个 AXI Interconnect 模块,也就是 AXI 互联矩阵,作用是提供将一个或多个 AXI 主设备连接到一个或多个 AXI 从设备的一种交换机制(有点类似于交换机里面的交换矩阵)。这个 AXI Interconnect IP 核最多可以支持 16 个主设备、 16 个从设备,如果需要更多的接口,可以多加入几个 IP 核。

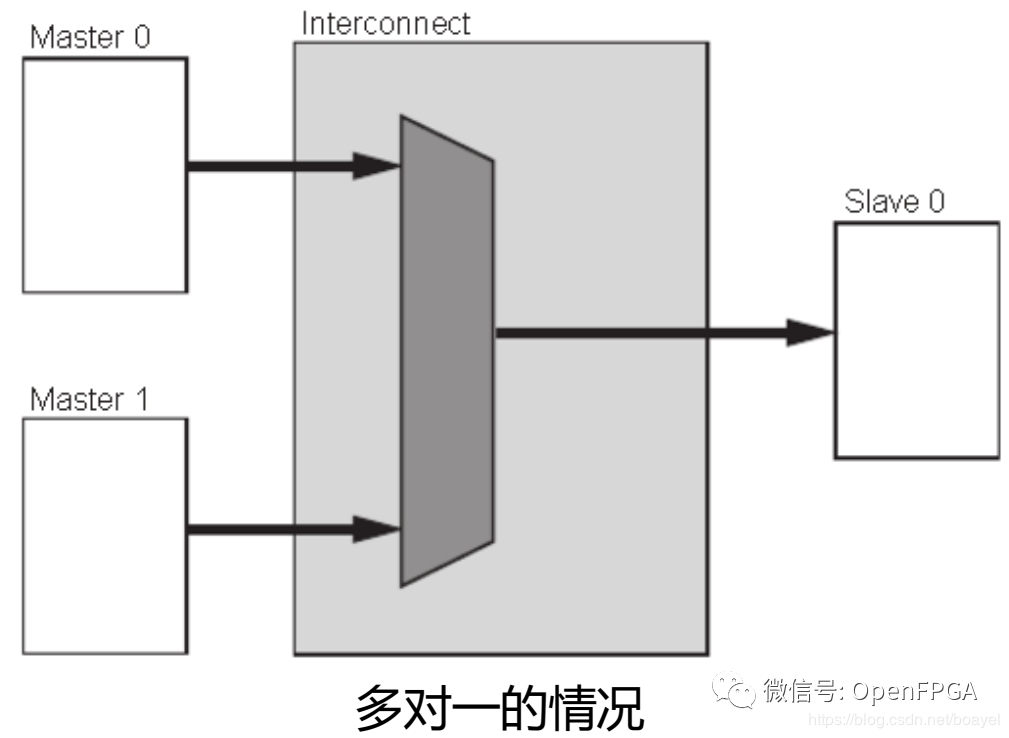

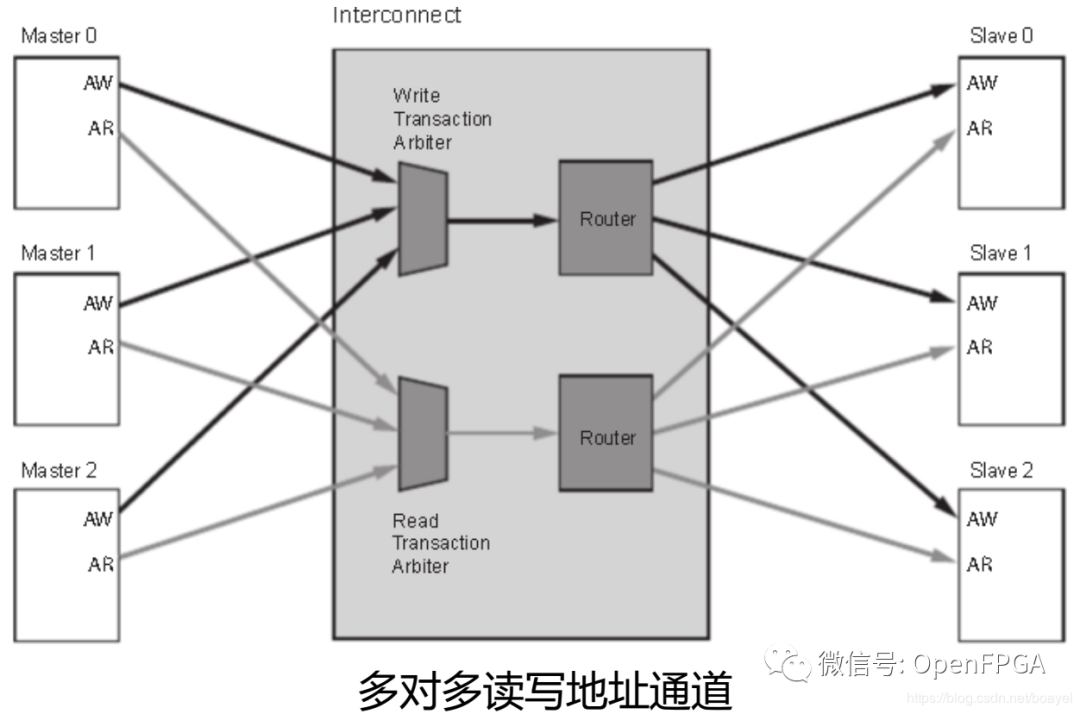

AXI Interconnect 基本连接模式有以下几种:

·N-to-1 Interconnect

·to-N Interconnect

·N-to-M Interconnect (Crossbar Mode)

·N-to-M Interconnect (Shared Access Mode)

图4‑30 多对一的情况

图4‑31 多对多读写地址通道

图4‑32 多对多读写数据通道

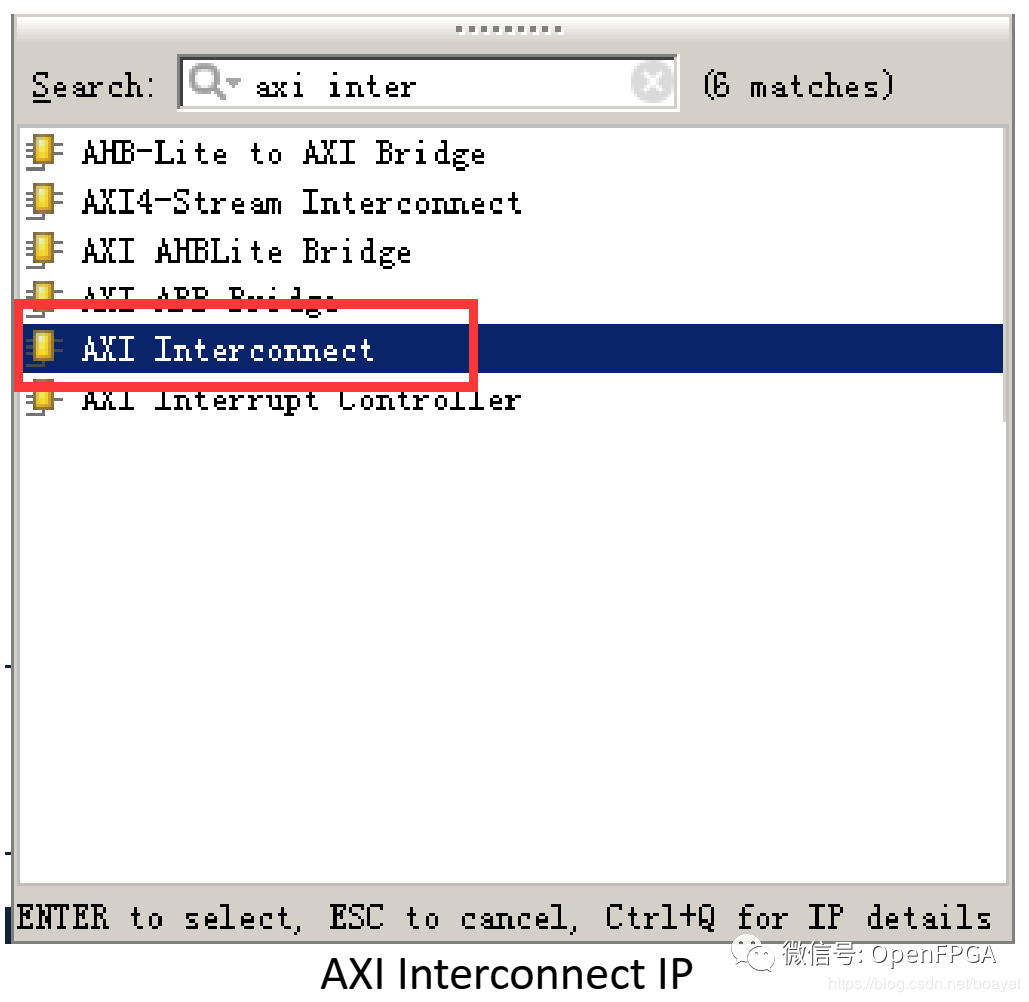

ZYNQ 内部的 AXI 接口设备就是通过互联矩阵的的方式互联起来的,既保证了传输数据的高效性,又保证了连接的灵活性。Xilinx 在 Vivado 里我们提供了实现这种互联矩阵的 IP 核axi_interconnect,我们只要调用就可以。

图4‑33 Vivado中IP核

AXI 协议支持乱序交易。通过接口的每次交易,协议都会分配一个ID 标签。协议要求相同ID 的交易按顺序完成,而对不同ID的交易没有顺序限制,可以乱序完成。

乱序交易可以在两个方面提高系统的性能:

互连设备在与具有快速响应能力的从设备和速度相对慢的从设备进行交易时,前者的交易优先后者完成。

复杂的从设备返回读到的数据,此时的数据可能是乱序的。例如,较晚获得的数据由于它被存放在内部缓冲器中,数据访问要优先于早期获得的数据。

如果一个主设备要求以交易开始时顺序一样的方式完成交易, 则那些交易要使用相同的ID 标签。但是若主设备不要求按顺序完成交易,则可以为不同的交易分配不同的ID,可以按任何顺序完成交易。

在一个多主设备的系统中,互连设备负责给 ID 添加额外信息,以保证所有从主设备那里传来的ID 标签是唯一的。ID 就像一个主设备号码,但通过扩展可以使得每个主设备可以实现多个虚拟主设备,在相同端口通过提供ID,指示虚拟主设备号码。

虽然复杂的装置可以利用乱序,但是简单的装置不要求使用。简单的主设备可以为每个交易分配相同的ID,简单的从设备可以按序响应交易,不用管ID。

-

AXI4

+关注

关注

0文章

20浏览量

8887 -

AXI4总线

+关注

关注

0文章

8浏览量

1381

原文标题:AXI总线详解-AXI4交换机制

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AMBA AXI4接口协议概述

工业交换机的安全机制

如何使用反射内存交换机

反射内存交换机与普通交换机的区别

网管型交换机和非网管型交换机的区别

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍

广域网交换机与局域网交换机的区别

POE交换机是什么?POE交换机的特点

交换机的作用与功能 交换机的基本配置

汇聚交换机和核心交换机区别

漫谈AMBA总线-AXI4协议的基本介绍

万兆铜缆交换机与万兆光纤交换机有什么区别?该如何选择?

管理型交换机 vs. 非管理型交换机

AXI4交换机制是什么

AXI4交换机制是什么

评论