在多时钟设计中可能需要进行时钟的切换。由于时钟之间可能存在相位、频率等差异,直接切换时钟可能导致产生glitch。

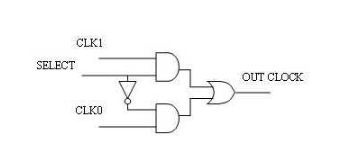

2|0组合逻辑实现时钟切换:

2|1HDL代码:

2|2电路图:

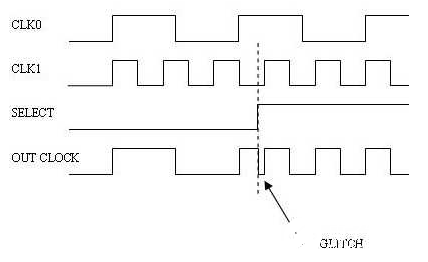

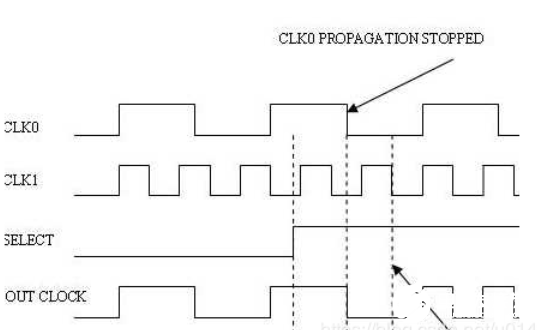

2|3波形图:

2|4问题:

使用上述电路进行时钟切换会导致在控制信号sel附近出现glitch。其原因在于控制信号可以在任意时刻进行时钟切换,切换信号相对于两个时钟都是异步信号。

2|5解决方法:

使用寄存器使得控制信号仅在时钟边沿作用,避免在任何时钟都为高电平是进行时钟切换。

3|0适用于倍频时钟切换的时序逻辑电路

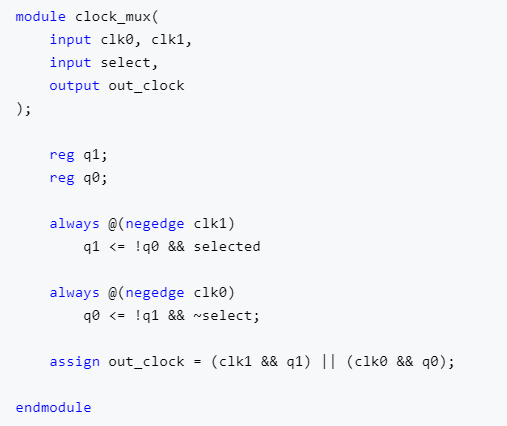

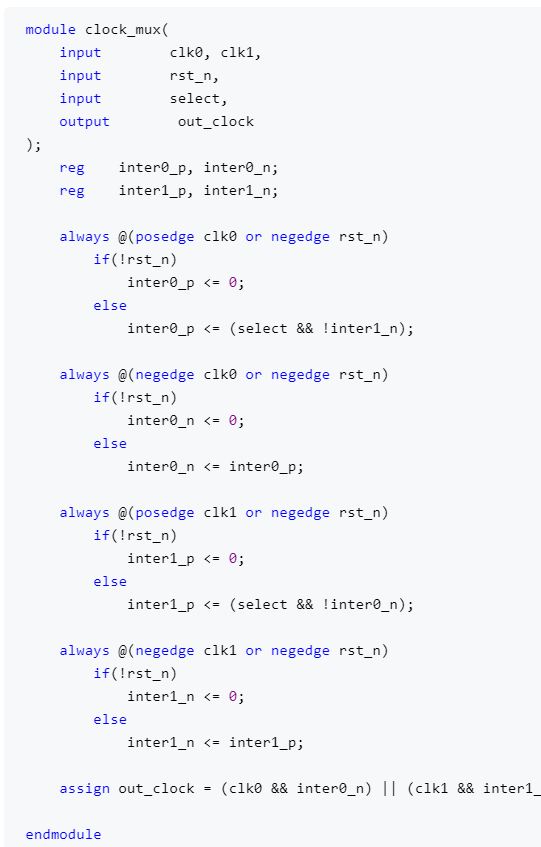

3|1HDL代码:

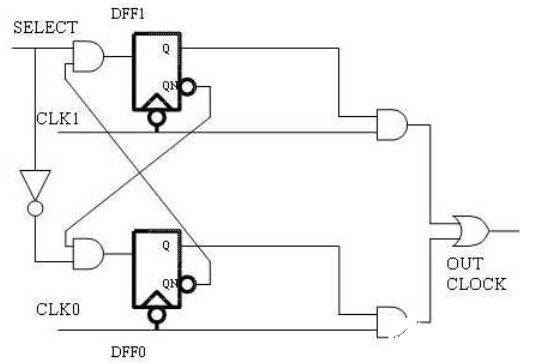

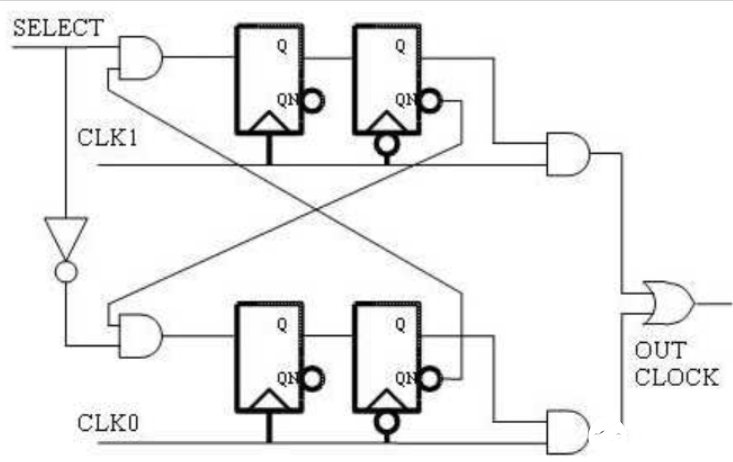

3|2电路图:

3|3波形图:

3|4功能:

当切换的时钟存在倍频关系时,分别插入一个下降沿触发的触发器以确保控制信号仅在时钟低电平时起作用。

3|5问题:

当DFF1输入的变化非常接近CLK1的下降沿时,可能会导致DFF1的亚稳态问题;DFF0同理。

为什么可以用于倍频时钟之间的切换?

4|0异步时钟切换的时序电路

4|1HDL代码:

4|2电路图:

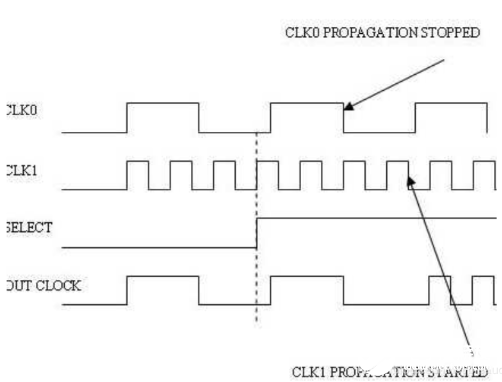

4|3波形图:

4|4功能:

通过为每个时钟源添加一个额外级的正边沿触发触发器来提供针对亚稳态性的保护,CLK0的上升沿采样到信号到下降沿传递至CLK1的正边沿触发器,并在CLK0下降沿后CLK1第一个上升沿之后的下降沿输出。(不是很理解)

-

时钟

+关注

关注

11文章

1757浏览量

132179 -

触发器

+关注

关注

14文章

2024浏览量

61488 -

时序逻辑电路

+关注

关注

2文章

94浏览量

16633 -

时钟设计

+关注

关注

0文章

27浏览量

10949 -

HDL代码

+关注

关注

0文章

5浏览量

2121

发布评论请先 登录

相关推荐

集成电路设计中静态时序分析介绍

时钟缓冲器工作原理及常见时钟缓冲器的国产替代情况

RTC时钟芯片+电池的应用案例(一)

时序约束一主时钟与生成时钟

北斗卫星时钟系统——ZREXT2000卫星时钟扩展分机

LMK04828-EP参考时钟自动切换的问题求解答

视频时钟合成芯片怎么用

时钟信号的驱动是什么

如何处理时钟电路的常见故障

PLL1705/PLL1706双通道PLL多时钟发生器数据表

时钟抖动和时钟偏移的区别

简述时钟抖动的产生原因

FPGA的时钟电路结构原理

多时钟设计中时钟切换电路设计案例

多时钟设计中时钟切换电路设计案例

评论