目前,电视节目的拍摄、制作、传输到播出正在实现数字化。MPEG视频音频编码标准的出现,解决了电视信号数字化后信息量过大而信道带宽有限的问题,加上数字视频硬件方面的产品不断进步,促进了各种数字视频产品的推出,这一切都预示着电视广播全面步入数字化的时代。数字电视产品的开发不仅能给观众带来高品质画面和音响效果的享受,而且MPEG-II视频音频压缩的ATM网接入技术的开发为VOD(视频点播)的时代铺平了道路。

目前世界上的数字电视系统标准有欧洲的DVB系统和美国的ATSC系统。这两种系统在视频压缩上都采用MPEG-II标准,在声音上DVB系统采用MPEG-II的音频压缩标准,ATSC系统则采用杜比AC-3压缩技术。本文介绍C-Cube公司MPEG-II编码器芯片DVxpert-II,它可用于欧洲DVB标准常规数字电视的前端系统的产品开发中。

1 芯片简介

C-Cube公司开发的视频处理单芯片DVxpert-II是在该公司DVx的MPEG-II单芯片编/解码结构的基础上提高了性能的处理器。它可以产生高品质的4:2:0和4:2:2 MPEG-II图像,同时压缩率也有所提高。该芯片能实现视频编码(video encoding)、解码(decoding)和编/解码(codec)三种功能,可实现运动补偿、分块/离散余弦变换压缩算法。

DVxpert-II处理器的核心是32位Micro SPACR RISC Core处理器,工作频率为100mhZ。该处理器内有一个16K字节指令的高速缓冲存储器(I-Cache)和一个8K字节的数据存储器(Data Memory)接口,这是一种可编程可升级的结构。芯片采用数据存储器而不是数据缓冲器,目的是使软件能更多地控制存储器,并允许重复进行DMA传输。此外,DVxpert-II处理器还有两个协处理器:DSP协处理器和运动估计协处理器(Motion Estimator),减轻了RISC处理器运算的负担,它们共同完成视频压缩编码算法,提高了编码速度。DSP协处理器每秒钟可执行大约16亿个算术操作指令(1600MOPS),执行向量从存储器到存储器的指令,这能提高从RISC到DSP流量操作速度。其8K字节存储器有两个缓冲区(两个块),可允许DMA和DSP同时操作。

DSP协处理器能完成以下功能:①解电视电影模式;②活动测量;③运动补偿;④自适应暂时滤波;⑤线性滤波和筛选;⑥DCT变换和逆DCT变换(12位);⑦量化和逆量化;⑧变长的Huffman编码和解码。

可编程运动估计协处理器(运动估计器ME)支持所有的块匹配和运动估计类型,它从RISC处理的CPU中取得运动估计的命令并返回结果。每次运动估计完成后会产生一个中断。

很多公司都有自己所开发的单芯片MPEG-II编码的LSI。进行DCT及运动补偿等演算所需的电路结构各不相同,C-Cube公司开发的DVxpert-II等芯片为大部分处理工作由RISC处理器及DSP等完成的“处理器型”芯片,与之配套的还有C-Cube公司开发的软件,即微码(.ux)文件。该文件包括进行视频压缩的代码以及初始化DVxpert-II处理器的存储器和下面要介绍的处理器外挂的SDRAM。因为它的可编程性能好,只要改换输入到处理器的微码,就可以变更压缩算法或修正软件的差错。

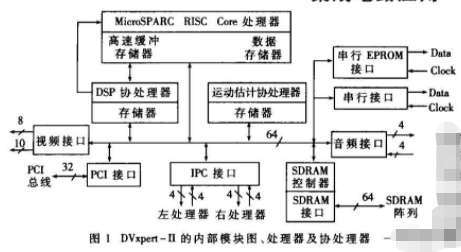

DVxpert-II的内部模块框图如图1所示。

由图中可见,DVxpert-II处理器是利用PCI总线接口与主机等设备相通信的,主机必须用PCI总线驱动处理器,控制编码过程;压缩好的视频比特流也必须经PCI总线存储到主机内,PCI接口由主机时钟(33MHz)驱动。

DVxpert-II处理器还有与串行ROM的接口,开发人员可选择利用串行EPROM装载部分初始化程序。在本开发系统中,为了使硬件电路简化,所有全部初始化过程都由驱动程序经PCI总线接口完成(可省去串行EPROM)。

该芯片还可外挂64bit同步动态RAM(SDRAM),实际电路采用4片16M比特的SDRAM实现8M字节外部存储器,存储C-Cube公司的微码和数据,并可由开发人员分配存储空间。当处理器进行MPEG-II视频编码时,SDRAM所含具体内容如下:①应用程序微码;②视频帧捕获缓冲区;③运动估计取样视频缓冲区;④预测的重构帧缓冲区;⑤参考帧;⑥速率缓冲区;⑦用于编码算法的本地表和其他数据。

处理器有视频接口,可输入/输出未压缩的数字视频流;还有音频接口,可输入/输出未压缩的数字音频(为获得与视频同步的信息)。DVxpert-II处理器只能进行视频编码,而未压缩的音频数据只能经PCI总线送到主机存储器,在DVxpert-II处理器外进行软件压缩。

本开发系统进行4:2:0Main Level @ Main Profile 的视频编码,仅用一片DVxpert-II处理器,因此可不用其和另一处理器相连的IPC的接口。

2 驱动程序的开发

虚拟设备驱动程序可包含对设备进行操作的设备专用代码,任务具有可设操作模式,需保存数据的硬件设备都需要有虚拟设备驱动程序。虚拟设备保持了每个应用程序的设备状态轨迹,并能保证当应用程序继续执行时设备处于正确状态。编码器将DVxpert-II集成于即插即用的PCI插卡,因此要开发该PCI设备的虚拟设备驱动程序(VxD)以支持编码器芯片的正常工作,该软件采用Microsoft VC 6.0开发,在WIN98操作系统下运行。WIN98操作系统的基本系统体系结构分成Ring0层和Ring3层,它们能提供不同级别的系统保护。Ring3层通过Intel处理器体系所提供的保护服务与其他的运行进程隔开,以达到保护的目的。Ring0层由虚拟机管理器(VMM)等构成。VxD是一个管理硬件设备或者已安装软件等系统资源的32位可执行程序,运行在Ring0层,处理系统或外设中断及DMA操作等,它使基于Windows的应用程序可有效地实现多任务。WIN95/98的VxD对即插即用提供支持,因此当DVxpert-II处理器电路设计成即插即用PCI扩展卡时,起动后可由操作系统自动检测到它。VxD的软件开发可利用美国Vireo.Software公司推出的VtoolsD for Win95开发工具包进行,该VxD被开发成可动态加载/卸载的驱动程序,以保护模式驻留在扩展内存中。VtoolsD中的Quick VxD程序可提供一些选项来快速生成VxD代码框架。编码器的VxD应包括:设备的初始化,处理中断信号,以及与运行在Ring3层进行通信。

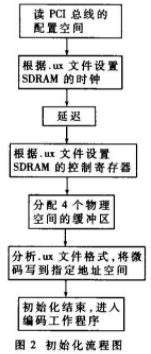

设备的初始化流程图如图2所示。

微码数据经PCI总线可以两种模式(从模式和主模式)传输到编码器设备上。从模式一次只能传一个32位的双字,速度慢,主模式以DMA方式猝发,可高速传大量数据。微码中写入处理器控制总线寄存器的部分只能采用从模式方式;微码中写入SDRAM中的数据根据.ux文件要采用DMA方式,这要通过设置处理器的一些寄存器实现。

WIN95/98的内存为平滑线性内存模式,线性编址模式简化了应用软件的开发过程,提供了存取虚拟地址空间的功能,使用户可存取的内存地址达4GB,2GB给应用软件,2GB给操作系统本身,因此VxD能申请4个BUFFER,用于存放DMA方式传输编码时所用的命令和消息,该BUFFER表示物理地址连续的空间,同时还可映射为相应的线性地址空间。

虚拟设备驱动程序可处理编码器工作时发来的中断,其服务过程如下:

①首先清除中断;②ISR把BUFFER中的消息存放到消息队列;③ISR检查当前消息的序列号:如果有错,转到处理错误的函数,若无错,ISR把命令队列中的下一个命令移到Ring0层的BUFFER内;④分析消息队列内的新消息,并且写相应的新命令。

在WIN95/98中,Win32API提供设备输入输出控制(DeviceIoControl)来支持Ring3到Ring0的直接调用,它通常用于调用动态加载的VxD;Ring0层则可通过OnW32DeviceIoControl(PEOCTLPARAMSpDIOCParams)中的pDIOCParams->dioc_OutBuf向Ring3层传递数据。

DVxpert-II提供的PCI接口和编程接口使其可方便地集成到PC插卡上,而且可由驱动程序对其进行较灵活的控制。目前该VxD已在使用之中,编码器设备工作良好。

责任编辑:gt

-

处理器

+关注

关注

68文章

19169浏览量

229172 -

芯片

+关注

关注

454文章

50432浏览量

421900 -

存储器

+关注

关注

38文章

7453浏览量

163610

发布评论请先 登录

相关推荐

基于Nios II和eCos的串口通信程序开发

基于ARM的MPEG 4视频编码器

MPEG-4 ASP视频编码器的软件优化设计

MPEG-2系列编码器

WinCE下光电编码器的驱动程序设计

NIOS II的特性及开发设计流程

基于Arria II GX FPGA的开发方案

MPEG-2压缩编码器原理

基于MPEG-4的视频DCT编码器的实现

uC/OS-II 应用程序基本结构及重要的API介绍

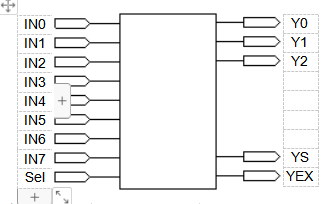

8线3线优先编码器的设计使用资料说明

MPEG-II编码器芯片DVxpert-II的功能特点及应用程序的开发

MPEG-II编码器芯片DVxpert-II的功能特点及应用程序的开发

评论