通过之前的博文,我们已经学会了如何使用 Report QoR Assessment (RQA) 和 Report QoR Suggestions (RQS) 来改进总体设计分析以及设计的时序收敛体验。

本篇博文将通过一个具体设计示例来演示如何在实现流程中将 RQA 与 RQS 结合使用。

RQA 能为设计提供评估得分,并提供有关后续步骤的指导信息,而 RQS 则可提供适用的改进措施的建议和策略。

RQA 和 RQS 都要求设计已完成综合或实现,才能对其进行分析。这两者会在设计中寻找故障点,然后评估设计是否有可能满足其设计目标。

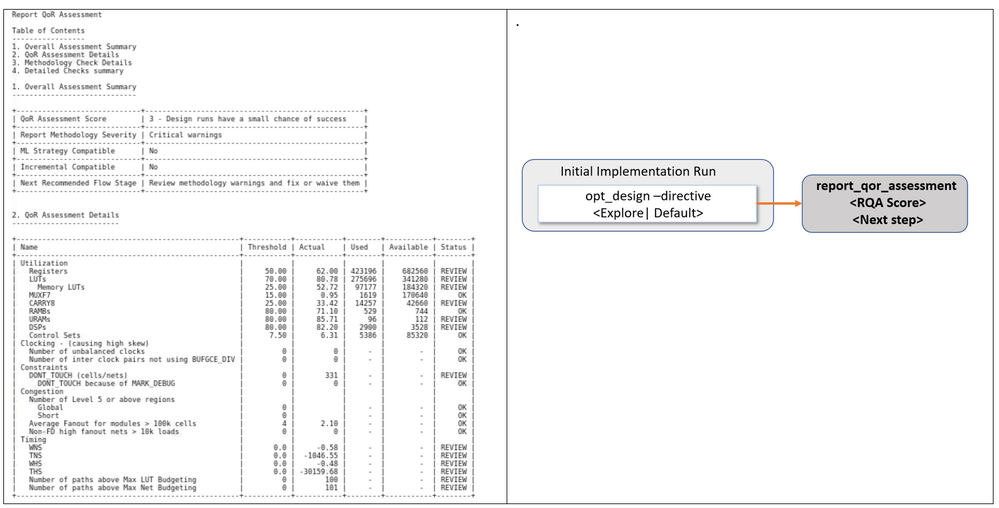

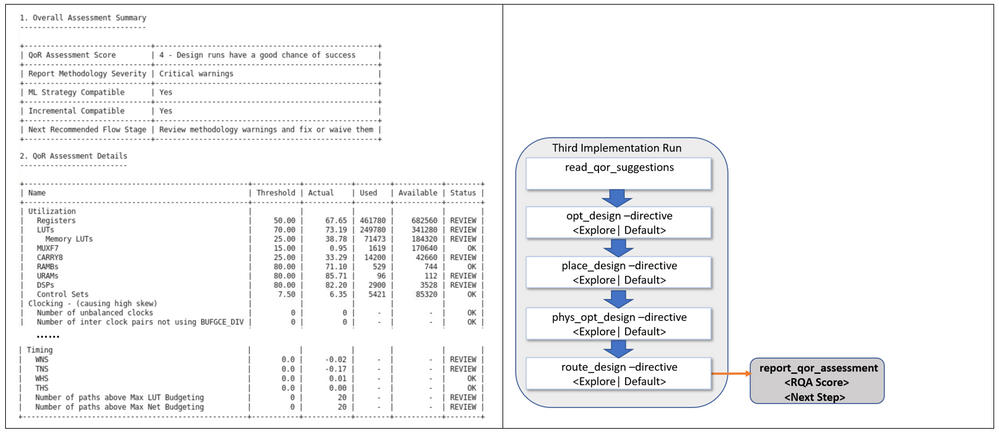

作为演示,我们选择了一项设计,并在为其运行初始 opt_design 后运行 RQA。RQA 报告如下所示:

让我们来看看评估得分汇总表(流程指南),了解其中每个部分的意义,然后直接查看评估详情。

此设计的初始评估得分为 3,即其成功可能性较小。通常,得分不低于 3 分表示 RQS 应该能够对设计进行改进,因此,我们将继续执行后续步骤。

如果得分为 1 或 2,则表示设计满足要求并完成实现步骤的可能性极低。在此情况下,建议是先返回并修复问题区域。

继续来看“方法论严重性”部分,汇总信息中显示存在一些严重警告。我们可以选择解决这些警告或者将其豁免。

对于本篇博文,我们选择将其豁免。请注意,您还可以使用报告方法论 (Report Methodology) 来运行完整方法检查,并修复所有警告,然后再继续后续步骤。

接下来的段落提供了 ML 策略合规性和增量编译合规性方面的信息。ML 策略仅限在 PnR 完成后才可用。增量流程也应在 PnR 完成后使用,并且通常建议在以下前提下执行:设计不存在关键问题并且设计处于时序收敛的最终阶段。即使 Vivado 工具未提供相关建议,我们也可以继续运行 ML 策略和增量合规性。

最后一段提供了“建议流程”阶段的相关信息。这一段为我们提供了有关继续执行后续步骤之前需要完成的操作的信息。在此情况下,我们会看到“复查方法论”警告,可以选择将其修复或者豁免。如上文所述,我们先暂时将其豁免。

如果在建议流程阶段并未提供具体指南,那么您始终可以继续通过运行 RQS 来提升 RQA 得分。

QoR 评估详情:

正如报告中所示,该表提供了有关 WNS 的信息以及许多其它使用情况指标。

此设计的初始 WNS 为 -0.580 ns。

状态列能帮助我们简单了解需要复查和修复的问题。阈值应被视为指导性数值,并非必须遵守的硬性规则。只要您留意这些数值,就可以看到虽然其中标记了许多需要复查的区域,但“内存 LUT (Memory LUT)”的值达到了阈值的 2 倍以上。

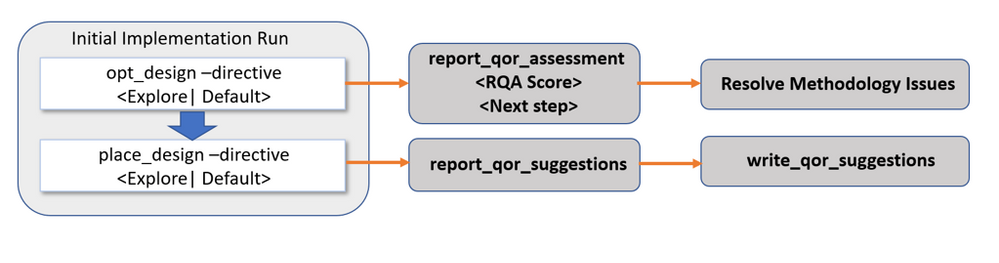

得到初始 RQA 评分后,就可以在任何阶段运行 report_qor_suggestions 并手动或自动应用这些建议来改进设计。

我们建议在完成 place_design 之后再执行 RQS 的初始运行,因为在此阶段,时钟 (clocking) 建议和偏差数值是准确的。并且,在 place_design 完成后还会提供拥塞建议。

假设我们继续执行实现流程,运行 opt_design 和 place_design,然后运行 report_qor_suggestions。

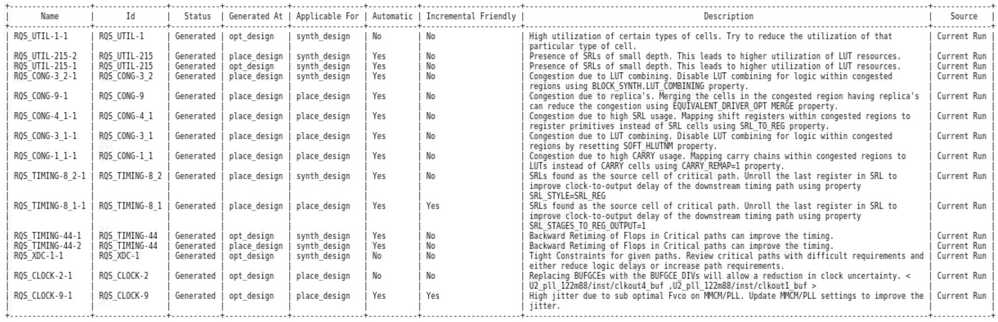

这样即可得到如下所示建议报告汇总:

在此报告中可以看到,有多项有关利用率、时钟、时序和拥塞的建议,该表还提到了生成和适用这些建议的阶段。

您还会注意到,这些建议可分为自动(即当您重新运行此流程后,会自动选取并应用这些建议)建议或手动(即这些建议将需要人工干预)建议。

请注意,表中建议的组织方式为按其对设计的 RQA 得分的影响从高到低排列。

在此阶段,我们必须运行 place_design 并运行这些建议,以便使改进生效。请注意 RQS 建议表,其中部分建议适用于 synth_design。 其中许多综合建议与 place_design 建议重叠,因此您可任选其中之一运行。

如果您运行的是 place_design 建议而不是综合建议,此流程可选择执行相应的建议。(例如,RQS_CONG-3_2-1 和 RQS_CONG3_1-1)在此情况下,如果您已运行 place_design,就无需再运行综合建议。

上表中显示的自动建议将在适用的阶段中实施,随后我们可以重新运行 RQA 来检查评分。

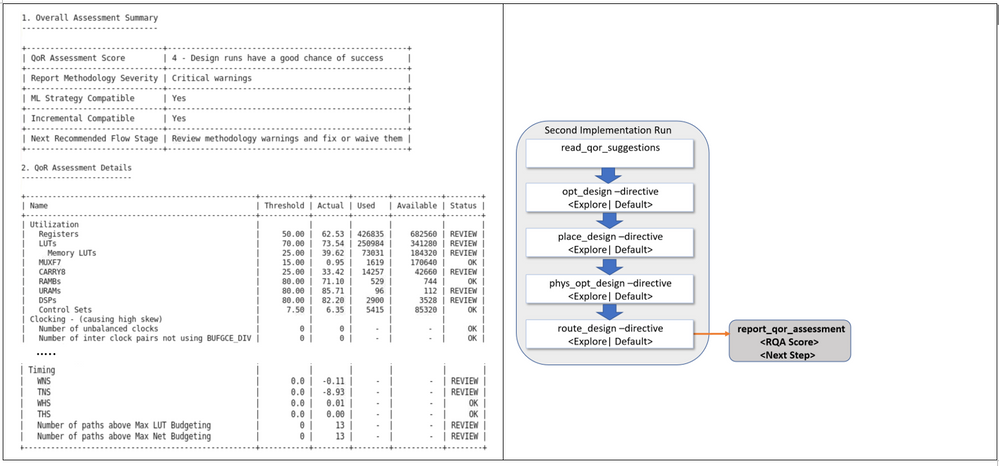

执行 opt_design 和 place_design 并应用建议后,RQA 得分仍为 3,如下表所示。

但请注意,应用建议后,WNS 得分已提升至 -0.21 ns。

由于评估表较为简洁,您可将该表与前表进行比对,查看设计参数中的改进。此外,请注意,在此用例中,流程指南建议您运行 report_qor_suggestions。

可以看到,设计布线后阶段的 RQA 得分为 4。WNS 现已提升到 -0.11 ns,相比第一份报告,内存 LUT 已显著降低。

应用 RQS 建议并继续执行实现步骤后,得分从 opt_design 阶段的 3 分提高到 route_design 阶段的 4 分。

如果您重复此过程,添加更多建议,那么 QoR 参数将能继续提高。

请注意,RQA 得分的细化程度并不足以显示拥塞、时序、利用率和时钟方面的所有改进成果。

例如,下表显示 RQA 得分为 4,但 WNS 数值已从 -0.11 ns 提高到 -0.02 ns。

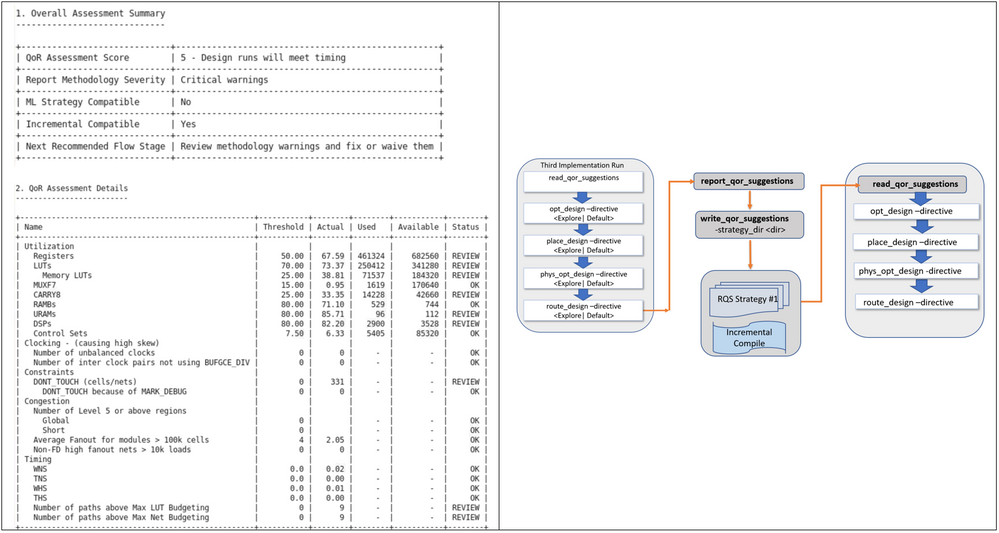

以上汇总表显示设计现已符合 ML 策略和增量编译的要求。仅当 PnR 已完成、所有关键设计修改均已完成并且设计运行时所有 Directive 均设置为 default 或 explore 后,ML 策略才可用。

如果设计非常接近时序收敛并且 RQA 得分为 4 或 5,那么您就可以利用 RQS 建议来启用增量流程。在我们的示例中,当前设计的 RQA 得分为 4,并且符合增量编译和 ML 策略的要求。在此类情况下,工具将为您提供最佳选项建议。

应用 ML 策略后的最终 RQA 得分为 5,评估得分如下所示:

请观察 RQA 与 RQS 的结合作用,它帮助我们改进了 QoR,并且将 RQA 得分从 3 提升到 4,最后,在时序收敛的最后冲刺阶段,它引入了 ML 策略和增量合规性,以实现设计收敛。

总结

通过本设计示例,我们学习了如何将 RQS 与 RQA 结合使用,以帮助我们清理设计中的时钟、拥塞和时序问题。

随后,当我们非常接近设计收敛时,通过运行基于 ML 的策略和增量编译,即可帮助我们完成最后一步。

编辑:hfy

-

时钟

+关注

关注

10文章

1712浏览量

131260 -

时序

+关注

关注

5文章

384浏览量

37244 -

Vivado

+关注

关注

19文章

803浏览量

66198

发布评论请先 登录

相关推荐

如何在KEIL软件中将变量定义在特定的RAM空间中

如何在 TIDK 器件和客户产品 HS 器件中完成安全流程

如何在FX3SMassStorage和GpifToStorage示例中连接SD卡?

如何在PyTorch中实现LeNet-5网络

如何在RTOS SDK中将FRC1计时器附加到NMI的信息?

使用TSIP驱动程序(Azure RTOS)的TLS实现示例

如何在实现流程中将RQA与RQS结合使用的设计示例

如何在实现流程中将RQA与RQS结合使用的设计示例

评论