1 xilinx FFT IP介绍

Xilinx快速傅立叶变换(FFT IP)内核实现了Cooley-Tukey FFT算法,这是一种计算有效的方法,用于计算离散傅立叶变换(DFT)。

1)正向和反向复数FFT,运行时间可配置。

2)变换大小N = 2m,m = 3 – 16

3)数据采样精度bx = 8 – 34

4)相位系数精度bw = 8 – 34

5)算术类型:

- °无标度(全精度)定点

- °定标定点

- °浮点数

6)定点或浮点接口

7)蝴蝶后舍入或截断

8)Block RAM或分布式RAM,用于数据和相位因子存储

9)可选的运行时可配置转换点大小

10)可扩展的定点核心的运行时可配置扩展时间表

11)位/数字反转或自然输出顺序

12)用于数字通信系统的可选循环前缀插入

13)四种架构在内核大小和转换时间之间进行权衡

14)位精确的C模型和用于系统建模的MEX功能可供下载

15)有四种运算架构可供选择

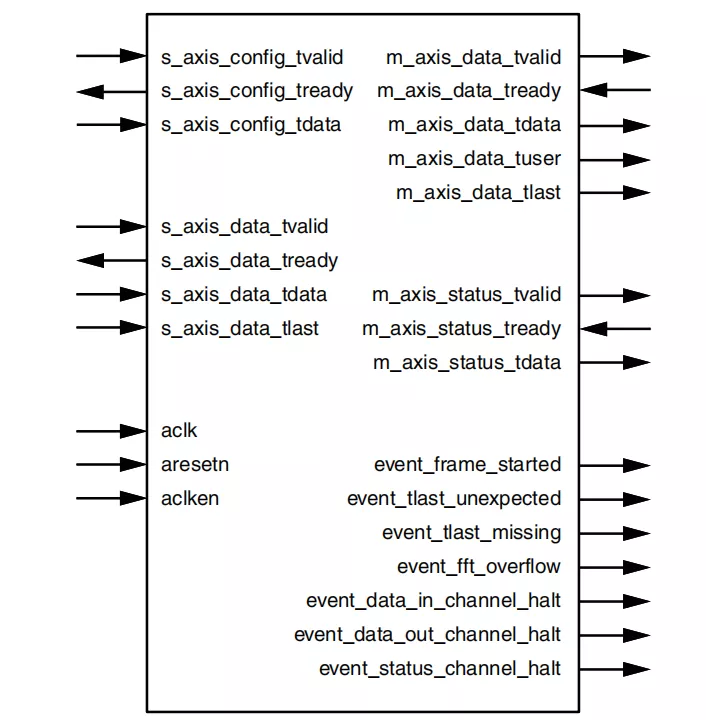

2 FFT IP接口介绍

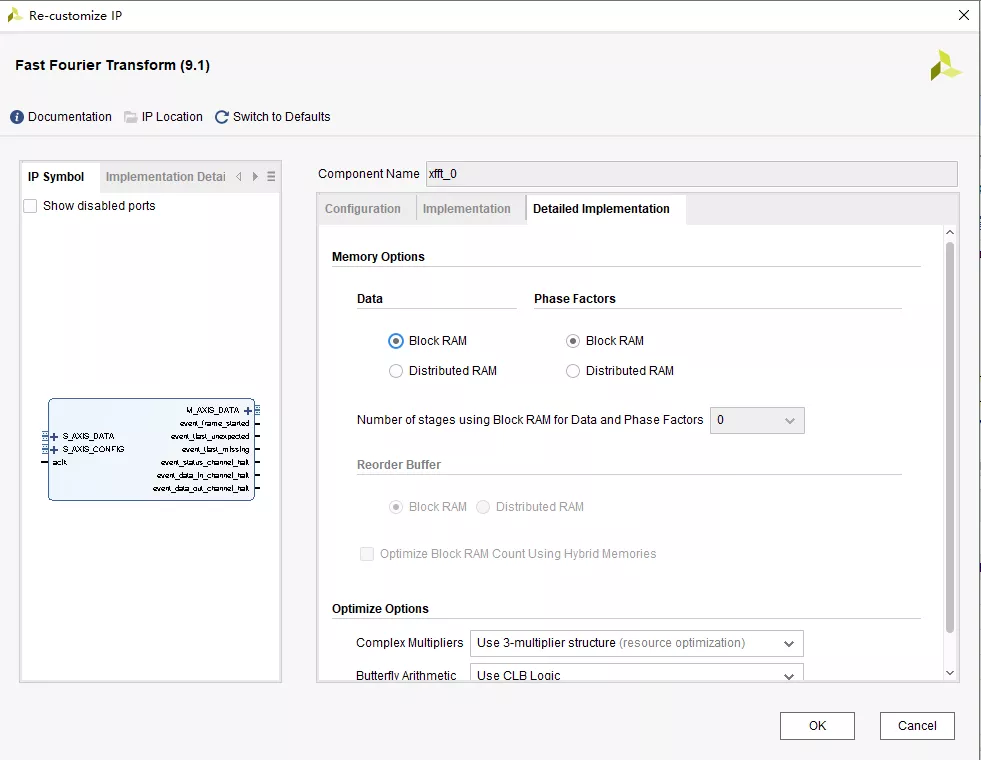

图1 xilinx FFT IP

1)AXI4-Stream 介绍

AXI4-Stream接口带来了标准化,并增强了Xilinx IP LogiCORE解决方案的互操作性。除了诸如aclk,acclken和aresetn之类的常规控制信号以及事件信号之外,到内核的所有输入和输出都通过AXI4-Stream通道进行传输。通道始终由TVALID和TDATA以及必填字段和可选字段(如TREADY,TUSER和TLAST)组成。TVALID和TREADY一起执行握手以传输消息,其中有效负载为TDATA,TUSER和TLAST。内核对包含在TDATA字段中的操作数进行运算,并将结果输出到输出通道的TDATA字段中。

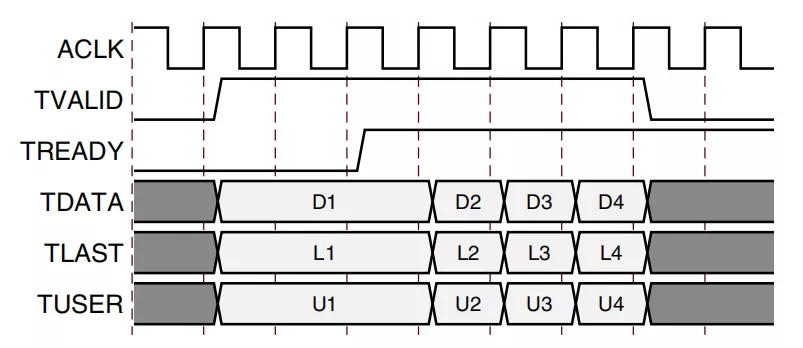

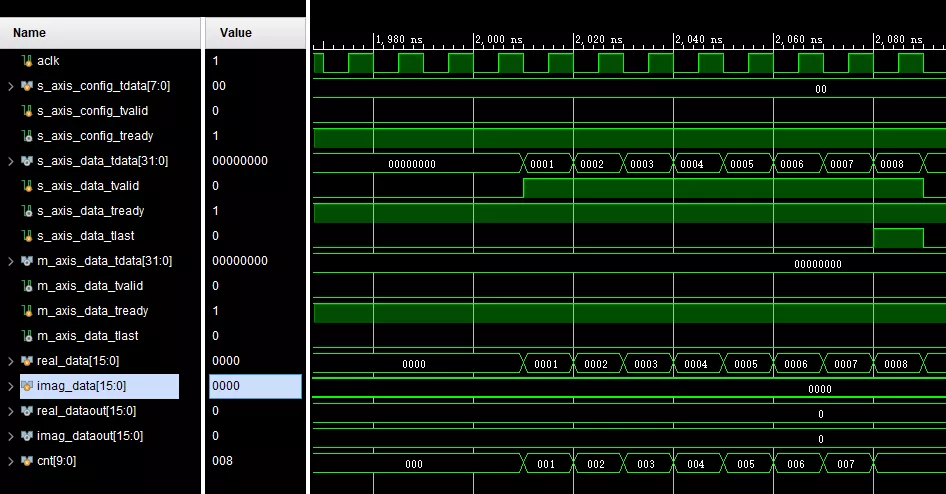

图2 AXI4-Stream时序图

图2显示了在AXI4-Stream通道中的数据传输。TVALID由通道的源(主)端驱动,而TREADY由接收器(从属)驱动。TVALID指示有效负载字段(TDATA,TUSER和TLAST)中的值有效。TREADY表示从机已准备好接收数据。当一个周期中的TVALID和TREADY均为TRUE时,将发生传输。主机和从机分别为下一次传输分别设置TVALID和TREADY。

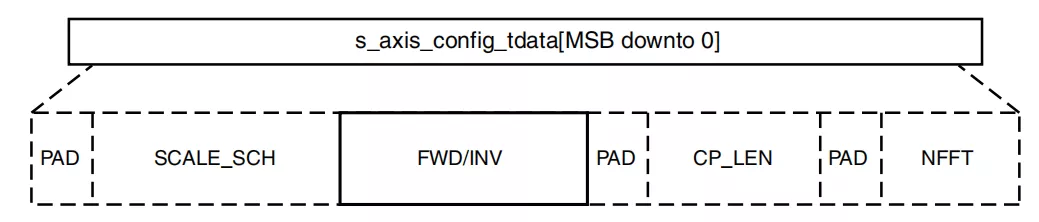

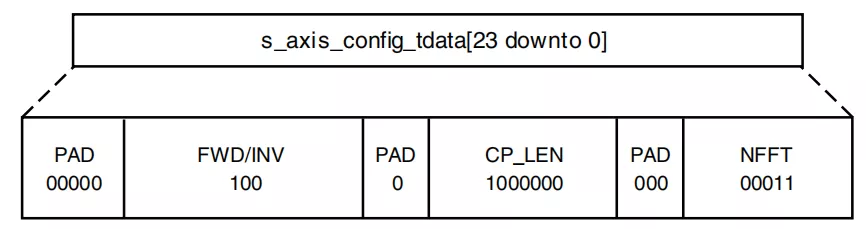

2)s_axis_config_tdata接口介绍

s_axis_config_tdata接口携带配置信息CP_LEN,FWD / INV,NFFT和SCALE_SCH。

NFFT(变换的点大小):NFFT可以是最大变换的大小或任何较小的点大小。例如,1024点FFT可以计算点大小1024、512、256等。NFFT的值为log2(点大小)。该字段仅在运行时可配置的转换点大小时出现。

CP_LEN(循环前缀长度):从转换结束起,在输出整个转换之前,最初作为循环前缀输出的样本数。CP_LEN可以是小于点大小的从零到一的任何数字。该字段仅在循环前缀插入时出现。

FWD_INV:指示是执行前向FFT变换还是逆向FFT变换(IFFT)。当FWD_INV = 1时,将计算前向变换。如果FWD_INV = 0,则计算逆变换。

SCALE_SCH伸缩时间表:对于突发I / O架构,伸缩时间表由每个阶段的两位指定,第一阶段的伸缩由两个LSB给出。缩放比例可以指定为3、2、1或0,代表要移位的位数。N = 1024,Radix-4 Burst I / O的示例缩放计划是[1 0 2 3 2](从最后阶段到第一阶段排序)。对于N = 128,Radix-2 Burst I / O或Radix-2 Lite Burst I / O,一个可能的扩展时间表是[1 1 1 1 0 1 2](从最后阶段到第一阶段排序)。对于流水线I / O架构,从两个LSB开始,每两对Radix-2级用两位指定扩展时间表。例如,N = 256的缩放时间表可以是[2 2 2 3]。当N不是4的幂时,最后一级的最大位增长为一位。例如,对于N = 512,[0 2 2 2 2]或[1 2 2 2 2]是有效的缩放时间表,但是[2 2 2 2 2]无效。对于此变换长度,SCALE_SCH的两个MSB只能为00或01。此字段仅可用于缩放算法(非缩放,块浮点或单精度浮点)。

s_axis_config_tdata接口格式:

1.(可选)NFFT加填充

2.(可选)CP_LEN加填充

3.前转/后转

4.(可选)SCALE_SCH

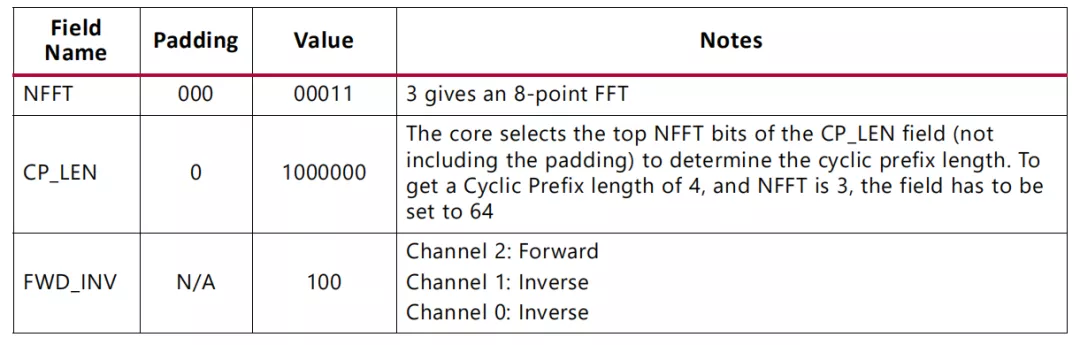

举例:

内核具有可配置的转换大小,最大大小为128点,具有循环前缀插入和3个FFT通道。内核需要配置为执行8点变换,并在通道0和1上执行逆变换,并在通道2上执行前向变换。需要4点循环前缀。这些字段采用表中的值。

这给出了19位的向量长度。由于所有AXI通道必须与字节边界对齐,因此需要5个填充位,从而s_axis_config_tdata的长度为24位。

3)相关标志信号

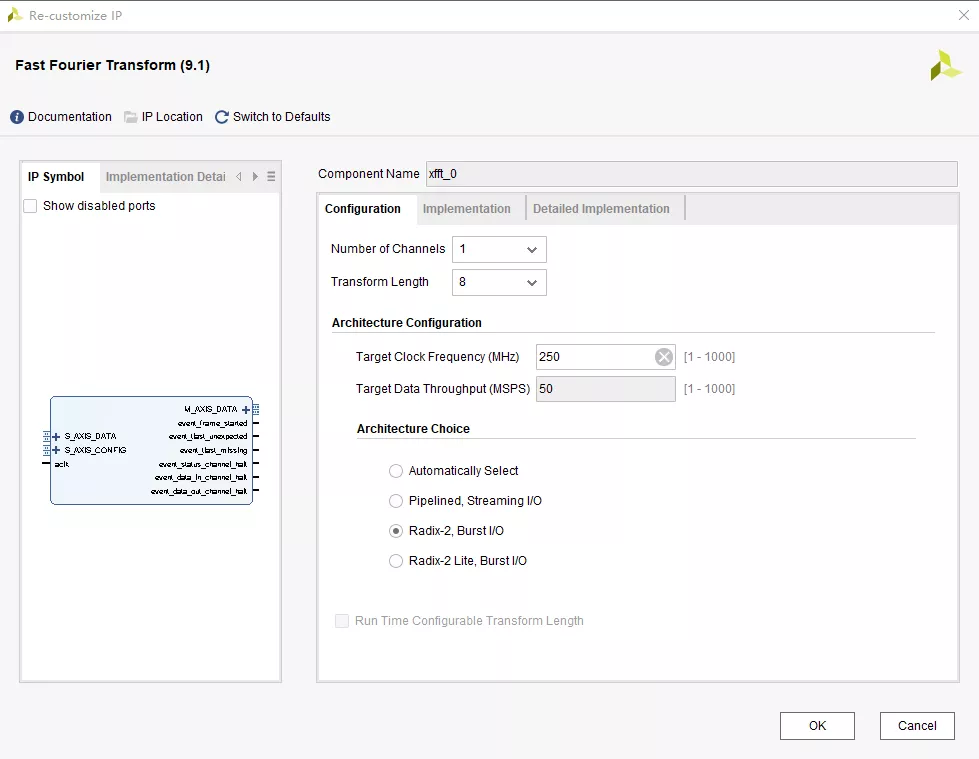

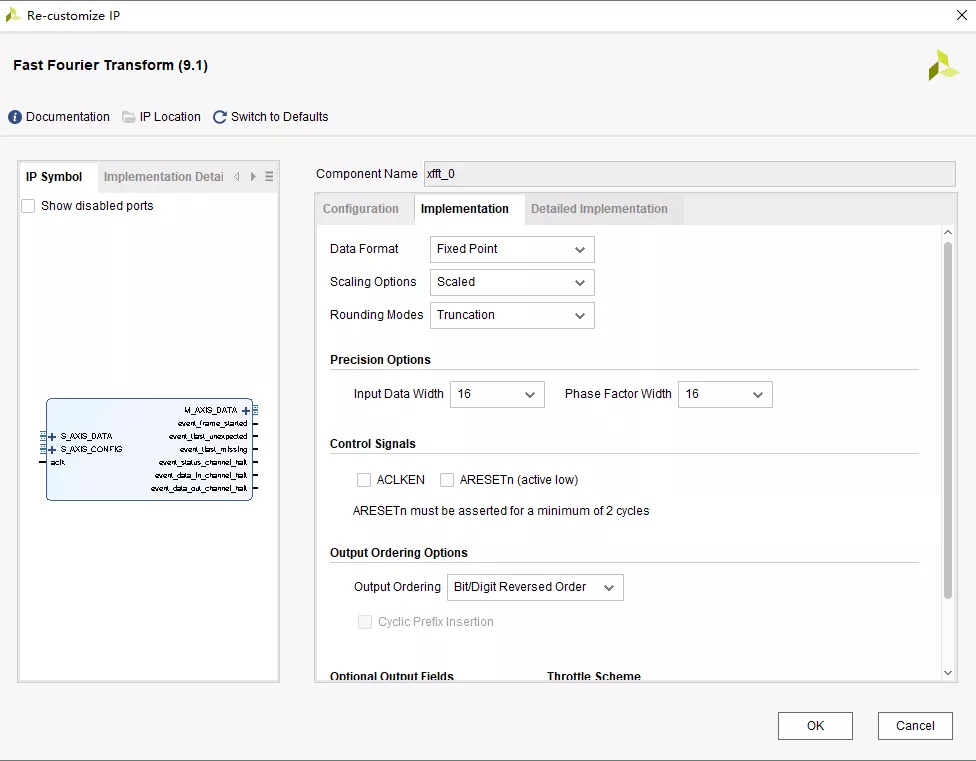

3 xilinx FFT IP的仿真测试

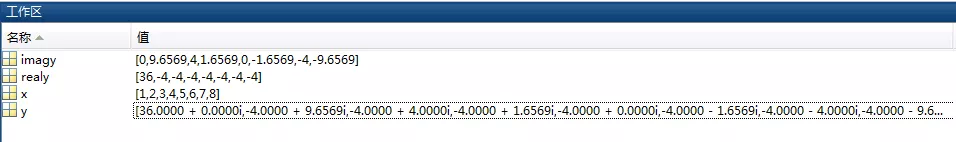

FFT的长度选择8点,x输入序列为x=[1,2,3,4,5,6,7,8];

Matlab验证:

clear all close all clc x = [1,2,3,4,5,6,7,8]; y =fft(x,8); realy=real(y); imagy=imag(y);

Y的实部输出为realy=[36,-4,-4,-4,-4,-4,-4,-4];

Y的虚部输出为imagy=[0,9.6569,4,1.6569,0,-1.6569,-4,-9.6569];

FPGA仿真验证:

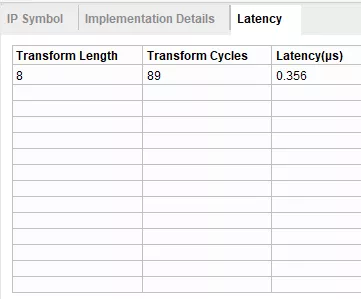

1)IP的设置

2)仿真顶层

`timescale 1ns / 1ps module tb_fft_top( ); reg aclk; reg [7 : 0] s_axis_config_tdata; reg s_axis_config_tvalid; wire s_axis_config_tready; wire [31 : 0] s_axis_data_tdata; reg s_axis_data_tvalid; wire s_axis_data_tready; reg s_axis_data_tlast; wire [31 : 0] m_axis_data_tdata; wire m_axis_data_tvalid; reg m_axis_data_tready; wire m_axis_data_tlast; reg [15:0] real_data; reg [15:0] imag_data; wire [15:0] real_dataout; wire [15:0] imag_dataout; reg [9:0] cnt; assign s_axis_data_tdata={real_data,imag_data}; assign real_dataout = m_axis_data_tdata[31:16]; assign imag_dataout = m_axis_data_tdata[15:0]; initial begin aclk = 0; s_axis_config_tdata=8'b0; s_axis_config_tvalid=1'b0; s_axis_data_tvalid=1'b0; s_axis_data_tlast=1'b0; real_data=16'd0; imag_data=16'd0; cnt = 0; m_axis_data_tready=1'b1; #1000; s_axis_config_tdata=8'b0000_0001; s_axis_config_tvalid=1'b1; #10; s_axis_config_tdata=8'b0000_0000; s_axis_config_tvalid=1'b0; #1000; repeat(8)begin s_axis_data_tvalid=1'b1; real_data=real_data+16'd1; cnt=cnt+1; if(cnt==8) s_axis_data_tlast=1'b1; #10; end s_axis_data_tvalid=1'b0; s_axis_data_tlast=1'b0; real_data=16'd0; #1000; $stop; end always #(5) aclk= ~aclk; fft_top Ufft_top( .aclk(aclk), // input wire aclk .s_axis_config_tdata(s_axis_config_tdata), // input wire [7 : 0] s_axis_config_tdata .s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid .s_axis_config_tready(s_axis_config_tready), // output wire s_axis_config_tready .s_axis_data_tdata(s_axis_data_tdata), // input wire [31 : 0] s_axis_data_tdata .s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid .s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready .s_axis_data_tlast(s_axis_data_tlast), // input wire s_axis_data_tlast .m_axis_data_tdata(m_axis_data_tdata), // output wire [31 : 0] m_axis_data_tdata .m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid .m_axis_data_tready(m_axis_data_tready), // input wire m_axis_data_tready .m_axis_data_tlast(m_axis_data_tlast) // output wire m_axis_data_tlast ); endmodule

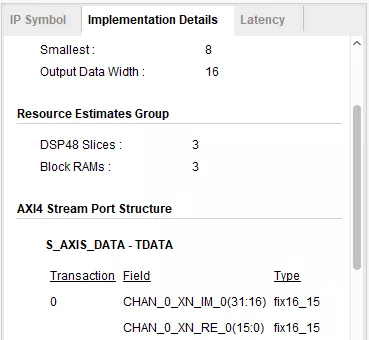

3)仿真结果

Vivado最终的仿真结果为

Real=[36,-4,-4,-4,-4,-4,-4,-4];

Imag=[0,-10,-4,-2,0,1,4,9];

与matlab的计算结果相比实部一样,除虚部因为数据位的取舍问题以外,正数和负数部分顺序相反。

编辑:hfy

-

Xilinx

+关注

关注

71文章

2172浏览量

122346 -

仿真

+关注

关注

50文章

4134浏览量

134126 -

快速傅立叶变换

+关注

关注

0文章

3浏览量

1482

发布评论请先 登录

相关推荐

傅立叶变换在机器学习中的应用 常见傅立叶变换的误区解析

傅立叶变换与时域信号的关系 傅立叶变换在音频信号处理中的应用

傅立叶变换在图像处理中的作用

傅立叶变换与拉普拉斯变换的区别

傅立叶变换的基本概念 傅立叶变换在信号处理中的应用

经典傅里叶变换与快速傅里叶变换的区别

EasyGo实时仿真丨PCS储能变流器控制仿真应用

EasyGo实时仿真丨三相永磁同步电机开环实验仿真应用

EasyGo实时仿真丨三相永磁同步电机开环实验仿真应用

Xilinx快速傅立叶变换接口及仿真测试实验设计

Xilinx快速傅立叶变换接口及仿真测试实验设计

评论