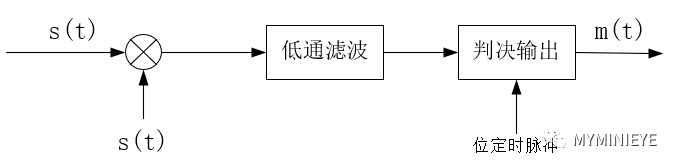

ASK相干解调原理

由图可知,输入信号和相干载波在乘法器中相乘,然后由低通滤波滤除所需要的基带波形,然后通过判决输出解调后的基带数据,判断输出需要位定时脉冲(位同步脉冲)。

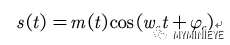

假设输入信号为:

相干载波为:

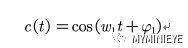

乘法器的输出为:

滤除高频成分,相干条件满足,即,则相干检测器的输出为:

其中Kc为低通滤波器增益,采用相干解调时,接收端需要提供一个与ASK信号载波同频同相的相干载波,否则会造成解调后波形的失真。相干载波的提取会极大的增加设备复杂性,实际中多采用更加简单的包络检波来实现ASK信号的解调。

(2)非相干解调

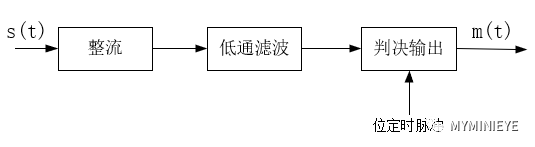

包络检波不需要提取相干载波,因此是一种非相干解调法,包络检波原理如下:

ASK非相干解调原理

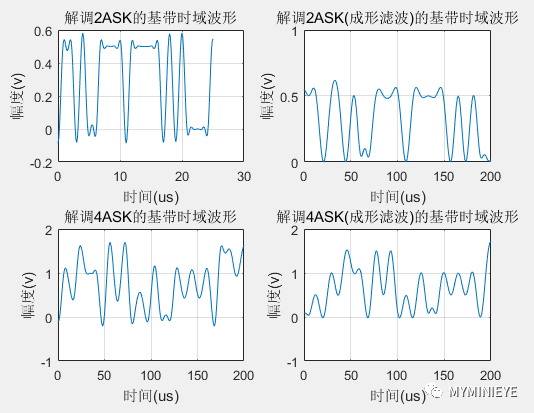

相干解调需要提供与输入同频同相的载波信号,通常需要采用锁相环技术实现载波信号的提取,较为复杂,这里采用非相干解调的方法实现ASK解调,只需要将输入信号经过整流滤波即可得到基带信号。

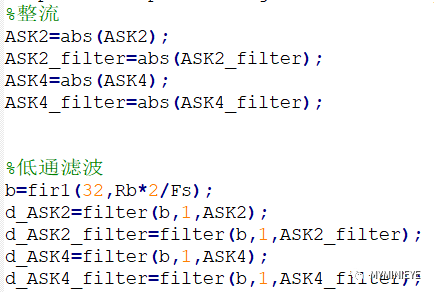

matlab主要代码如下:

3.ASK解调技术的FPGA实现

完整的ASK解调电路包括基带解调及位同步时钟的提取,对于数字解调系统来讲,我们需要在接收端获得与发送端相同的数据信息,最终输出的结果是数据流,以及与数据流同步的位同步时钟信号。

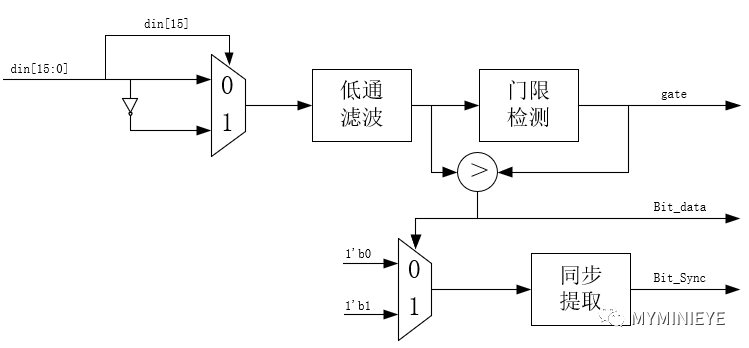

ASK的解调可以分为基带波形的获取,判决门限获取,位同步时钟提取三个模块,在FPGA中的设计如下:

滤波和门限检测相对简单,这里主要介绍位同步时钟的提取。

3.1位同步时钟介绍

位同步也称定时同步、符号同步、码元同步,是数字系统特有的一种同步。

(1)如果基带信号中已含有显著的时钟频率(或时钟导频分量),可以使用窄带滤波或者锁相环提取,这种方法称为插入导频法。

(2)当传输随机比特流信号中不含有离散的时钟频率及谐波时,同步信息包含在基带数据初始相位中。不能直接提取,一般有两种方法,非线性变换滤波和特殊鉴相器的锁相法。

(3)基于Gardner的位定时同步算法,采用产值滤波的原理来实现位定时同步及最佳抽样判决。

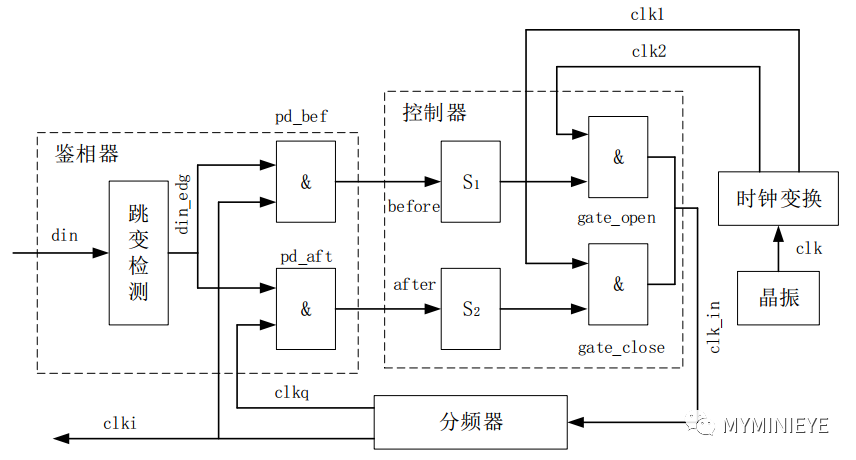

这里使用锁相位同步法来实现同步时钟的提取,但是这种方法只是用二进制单bit调制信号,对于多bit信号,通过简单的门限判决无法获得由码元00跳变到11的初始相位,对于二进制来言。0和1之间不存在其他的码元,数据判决只有一个门限,多进制的位同步技术可以使用Gardner算法来实现。数字锁相位同步环的原理如下:

如上图所示,数字锁相位同步环主要由鉴相器、控制器、分频及时钟变换电路组成。输入信号din是单bit信号,跳变检测用于检测输入信号的跳变沿,当检测到一个跳变沿的时候产生一个时钟周期的高电平信号,提取出位同步信息,用于检测同步信息的时钟与时钟变换电路的输入时钟信号是否相同。仿真结果如下:

当同步时钟滞后输入的时候,会产生一个滞后脉冲(pd_aft),然后滞后门 (pd_after) 打开,可以看到在1中gate_close门会打开,clk_in会多加一个脉冲,使得下一个时钟提前1个调整周期。这里数据采样速率为码元的8倍,每次相位调整步进为一个数据采样周期,相当于1/8个码元周期。当同步时钟超前输入数据的时候会产生一个超前脉冲(pd_bef),然后超前门(pd_before)打开,clk_in会扣除一个脉冲,使得下一个时钟滞后一个调整周期。无论加还是减脉冲,相位校正总是阶跃式的,稳态相位不会为零,而是围绕零点左右摆动。

3.2仿真结果

通过上述的分析和设计,得到最终的仿真结果,其中data为调制的二进制bit信号,abs_din是整流输出,din为滤波器的输出,mean为判决门限,decode_data为判决输出,从下图中可以看出解调后的数据decode_data能够与输入的2ASK信号对应,但是最后同步输出bit_data与调制的数据对应不上。

4.总结分析

4.1 从波形上看判决输出基本与输入一致,最终同步的数据不对,首先定位到位同步时钟的提取,重新梳理了位同步的原理,以及时序波形,发现了一个问题,如下所示:

过门限检测之后的数据高低电平长短不一,位同步时钟存在漏检和误检的情况,在连0和连1出现次数较多的情况下尤为严重。于是我把过门限检测之后的数据经过D出发器处理成等长度的二进制数据,并更换调制信号为1和0交替的信号。

可以看到,结果是正确的,把解调后的数据和调制数据对比也是正确的。在连1不是很多的情况下,依然能够正确解调出正确数据,如下所示:

256点门限长度

4.2猜测可能和门限检测的长度有关系,即对滤波之后的调制信号求平均的点数。因此改变门限检测长度,测试了32,64,128,256点的门限长度,可以发现门限的平滑度不同,但是结果都是正确的。

32点门限长度

4.3最后我把数据改成最初的调制数据,得到结果如下:

通过matlab比对数据,发现只有前5个数据不一样,可能是由于一开始没有足够的数据点数计算正确的判决门限,导致初始的解调数据是错误的,后续数据比对完全一致。

最终确定原因,数据比对不上是由于过门限检测之后的数据高低电平长短不一导致的,下图是我在仿真中找到的一个比较明显的地方,decode_data为1010101,但是同步输出全为1。

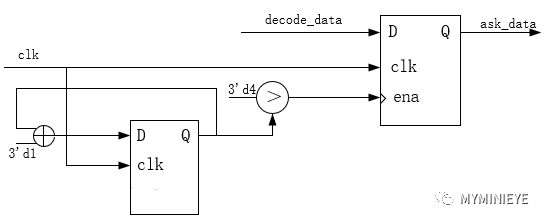

过门限检测之后的数据不能直接给位同步时钟提取模块,需要做以下调整才能得到正确的解调。为什么选取4作为计数器判别,采样频率为码元速率的8倍,一个码元采样8个点,首先同步decode_data脉冲边沿,计数器从0~8,在门限检测的时候,认为超过4个点为1,结果为1,超过4个点为0,结果就为0。

-

FPGA

+关注

关注

1664文章

22545浏览量

640414 -

无线通信

+关注

关注

58文章

5194浏览量

147116 -

波形

+关注

关注

3文章

409浏览量

33243 -

ASK

+关注

关注

2文章

75浏览量

46999 -

时钟信号

+关注

关注

4文章

511浏览量

30157

发布评论请先 登录

如何使用FPGA实现基于802.11a协议的OFDM调制解调

ASK信号的解调原理 ASK解调技术的FPGA实现

ASK信号的解调原理 ASK解调技术的FPGA实现

评论