1. 初识XILINX

初识XILINX,是PYNQ-Z2。当时刚学完学校的数字电路课程,对FPGA并不了解,学校课程也仅仅是用VHDL验证了一些基础的FPGA实验,例如生成一个n进位序列码。并不知道FPGA有这么广阔的应用。在一次王伟博士的培训上,我第一次接触到了PYNQ。在讲座中,我运行了一个PYNQ的demo。通过USB摄像头检测边缘处理。如下图:

当时给了我很大的震撼,瞬间对FPGA非常感兴趣。王博士指点我,想学好FPGA,光会一点VHDL的皮毛并不够,要对工业上最流行的VERILOG非常熟悉才行。虽然我们学校并没有开设关于VERILOG的课程,但我在图书馆借阅了相关的书籍首先进行自学,并在实际操作中补充自己。这一步也为之后全国FPGA大赛的个人能力测试建立了基础。随后,王博士开展面向全系的VERILOG普及培训,我非常有幸作为助教参与其中,给低年级学弟学妹开展VERILOG基础语法的讲解。

随后,XILINX公司推出ULTRA96板卡的试用申请。这对我来说既是机遇,也是挑战。不负一番努力,我通过了板卡的申请。收到板卡后,困难一直伴随着我。因为对LINUX系统并不熟悉,第一次让设备连接网络就花费了我很长时间。当时网上并没有现在对它的明确资料,靠着类似的设备树莓派的经验去一步步试着去配置,最后总结出多种联网方法并和实验室同学分享。在此期间,我意识到要学好嵌入式技术,必须对LINUX做到很熟悉。

2. 参加FPGA大赛

完成基础的培训后,我报名参加了2019年的FPGA全国大学生竞赛。我们的项目是制作一台基于STM32平台的智能小车,可以通过车载摄像头设识别障碍和到路线。利用ULTRA96强大的计算性能,运行裁剪过的YOLO/SSD模型。实现识别的速度和精度的双向赢。期间,训练模型对我来说在初期也是一个很大的挑战,从第一次接触Tensorflow到训练模型,遇到很多的问题也得到了很多老师同学的帮助。

解决重重问题后,我完成了我们比赛的所有准备,来到南京答辩。因为板卡属于自选题目组,所以在比赛的房间内都是来自一些名校的研究生组合,无形中给了我很大压力。在评委组验收的时候,暴露出识别帧数低下的问题,评委也给出一些解决的建议。不负众望,最终我取得了不错的二等奖,对我来说也是非常的不容易。其实,得到评委的肯定的评价比得知获奖更为开心。

我比赛中的作品

3. 假期DNNDK SSD

在假期中,寻找到了当时大赛时对障碍物识别帧数低的原因,通过对设备的调整,实现SSD模型15-20帧的识别速度。如下图。

4. 参加XDF

因为对XILINX非常感兴趣,我自费报名参加了XILINX的2019年XDF全球开发者大会。参加本次大会让我受到了很多启发。我们向XILINX工程师询问了ULTRA96无法发挥完全性能可能的原因并进行了探讨,对之后解决这个问题有了非常大的帮助。

在XDF的现场实验室,我们通过做官方VITIS例程,体会到了XILINX新一代集成工具VITIS的强大整合能力。因为大赛的原因,我对小车的相关技术非常感兴趣。在AVANT的展台上,

我发现了了AVANT的工程师用ULTRA96作为ROS(Robot Operating System)作为载体运行激光雷达的运行。

5. SLAM实时建模

这给我非常大的启发,依托ROS强大的外设库支持、仿真能力和FPGA强大的运算性能,可以实现更高性能的机器人底盘系统。下图是我利用ROS对REALSENSE多摄像头传感器的仿真,实现SLAM实时建模我房间的一角。

6. PETALINUX镜像

最近,认识到要真正用好ZYNQ,必须掌握PETALINUX去定制所需要的系统。在这个过程中遇到了很多问题。或许是计算机编译的速度慢、或许是资源需要连接外网导致网速很慢,最终让整个编译过程无限变长。为了解决这些问题,付出了很多时间作为代价。连续2周的连续从早到晚的编译,因为我的操作不当,没有把计算机放在通风良好的地方。计算机的主板南桥因为长时间过热烧毁了,不过一切苦难克服之后都是值得的。通过大量的尝试,不断的成功和失败。让我越来越清楚PETALLINUX的运行规则。最后,实现带有DPU功能的定制镜像的制作,如下图:

图像处理流程:

1.读取图像

2.将读取的图像数据格式转换为AXI格式

3.将AXI格式的图像转换为OPENCV可以处理的Mat格式

4.通过HLS_OPENCV处理库对图像进行处理

5.将处理完的图像数据从Mat格式转换为传输的AXI格式

6.将图像的AXI转换为图像格式

7.将图像进行输出

用到的HLS_OPENCV函数详细参考官方指南UG902

展示一个简单的图像处理结果:

8. VIVADO VITIS ULTRASCALE+MPSOC IP FPGA设计

VIVADO是FPGA设计最基础的一环。它是一个功能强大的集成开发环境,包含了综合和实现的环境。VIVADO可以实现自动管理运行数据,并可以方法运行。可以对多种硬件描述语言进行综合。VIVADO的出现,提高了我们对FPGA的设计效率,简化了设计流程。

VIVADO项目设计流程:

1. 加入对应板卡信息

2. 打开VIVADO并新建工程

3. 选择板卡并完成建立

4. Create Block Design

5. 添加PS、Pl核心及组件接口并连线

6. Create HDL Wrapper

7. 综合并生存比特流

8. 输出硬件描述文件

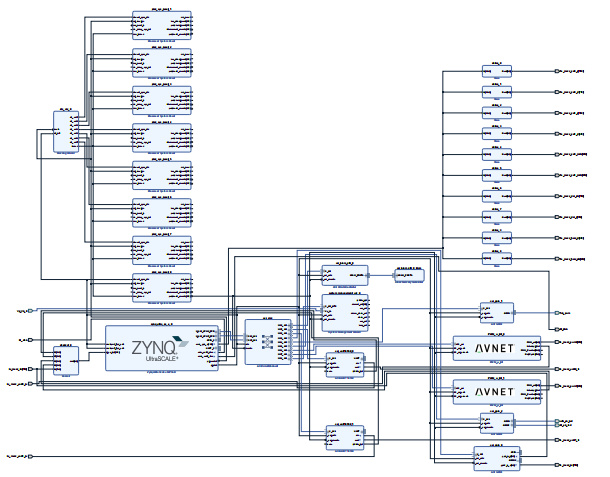

如下图是Ultra96的板卡设计图

VITIS是XILINX公司最新推出的统一软件平台,它可以为边远、云和混合计算应用加速提供统一编程模型。利用与高层次框架的结合和完整的加速库,可以加快我们的设计效率。

下面是利用VITIS实现的一个终端FPGA串口输出的仿真

VITIS流程:

1. 创建平台项目

2. 输入硬件描述文件并完成创建

3. 修改我们要用到的串口

4. 保存并重新BULID

5. 创建一个应用项目

6. 选择一个串口输出模板并修改主函数

7. 保存并重建项目

8. 通过硬件仿真

下面分别为设备平台和仿真结果:

-

FPGA

+关注

关注

1635文章

21837浏览量

608318 -

赛灵思

+关注

关注

32文章

1794浏览量

131733 -

激光雷达

+关注

关注

970文章

4064浏览量

190918

发布评论请先 登录

相关推荐

FPGA图像处理基础----实现缓存卷积窗口

使用IP核和开源库减少FPGA设计周期

FPGA 实时信号处理应用 FPGA在图像处理中的优势

芯驿电子 ALINX 推出全新 IP 核产品线,覆盖 TCP/UDP/NVMe AXI IP 核

基于FPGA的HLS图像处理IP核设计

基于FPGA的HLS图像处理IP核设计

评论