Overlay 简介

RISC-V-On-PYNQ Overlay实现了在PYNQ-Z2板上的RISC-V处理器及工具链集成,并提供了完整的RISC-V源码与设计流程,得益于PYNQ软件框架,其支持在Jupyter Notebook对RISC-V进行编译、调试与验证,即可以在Jupyter Notebook上编写一段C/C++/RISC-V汇编程序,将编译后的二进制文件放到picoRV32上运行。

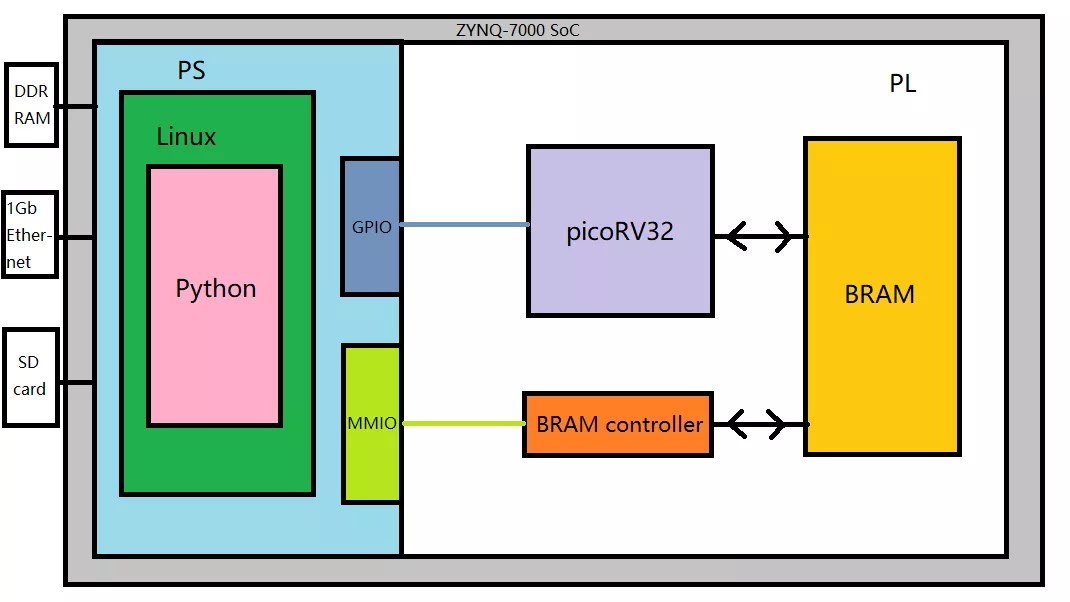

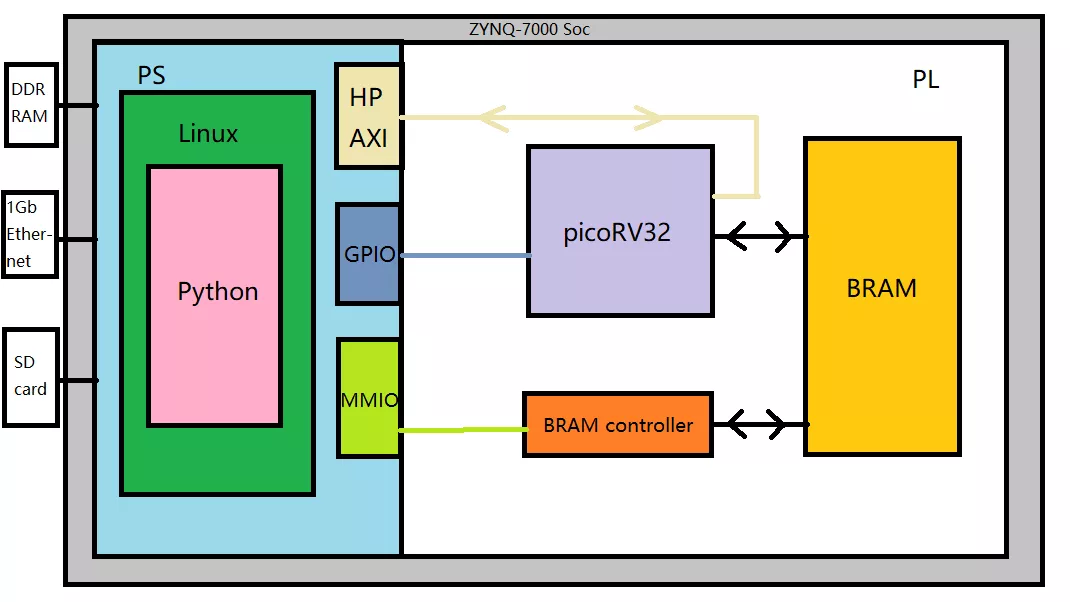

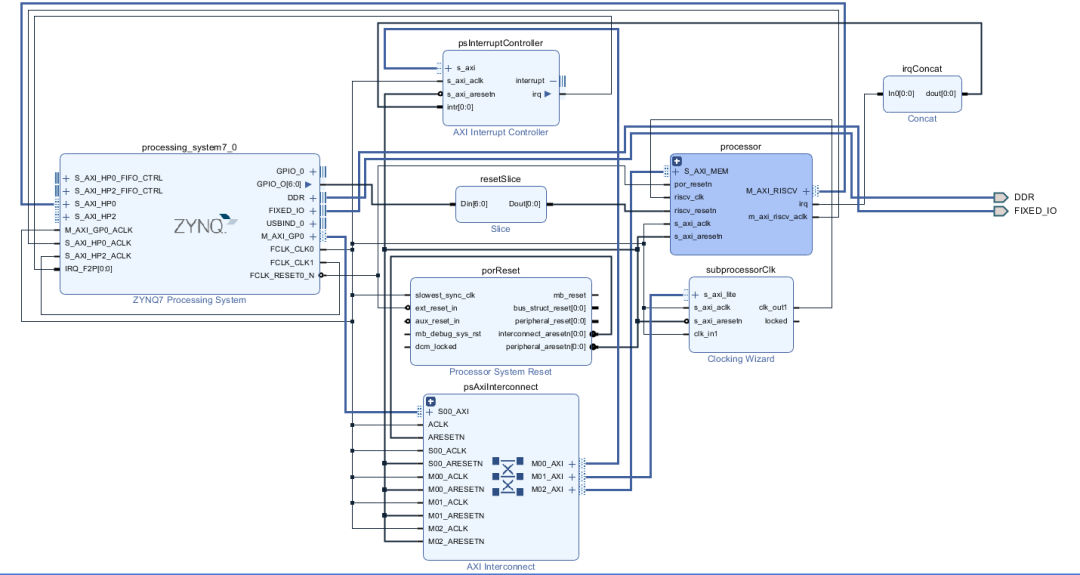

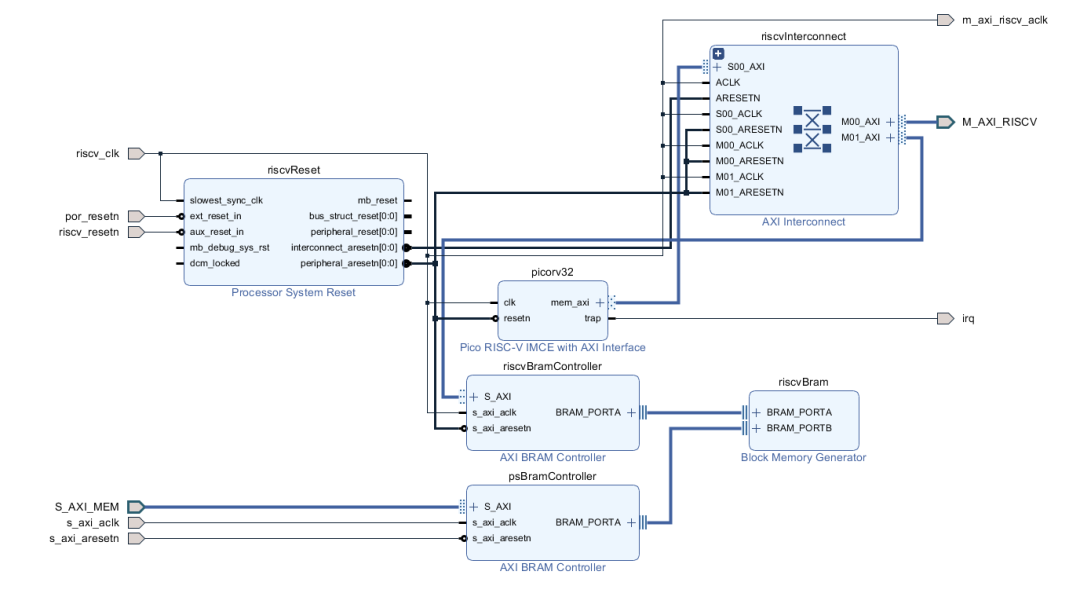

以下两张图是本Overlay的系统框图,其中picoRV32是一个开源的RISC-V核,它具有占用资源少的特点,并且它自带AXI接口,可以方便地使用Xilinx提供的各种基于AXI总线的IP。本项目有两个工程,它们的区别主要是picoRV32接的RAM:上图只使用BRAM,而下图同时使用到了BRAM和外部DRAM。

快速开始

- 环境需求PYNQ V2.4。

- 在PS端,我们需要编译安装RISC-V工具链和对应的库。

Github内的项目文件Clone到本地。

git clone

https://github.com/Siudya/RISC-V-On-PYNQ.git /home/xilinx/ RISC-V-On-PYNQ

在RISC-V-On-PYNQ/notebooks/tutorial中有5个Notebook,包含了Overlay完整的部署流程。

鉴于从零开始部署的时间会较长,所以我们也提供了完整的镜像文件,直接烧录到SD卡就可以运行(注:提供的ext4分区剩余容量较小,请用户根据需要自行调整)。

在OpenHW的远程PYNQ实验平台上也已经为大家安装好了环境,可以直接使用。

示例Notebook

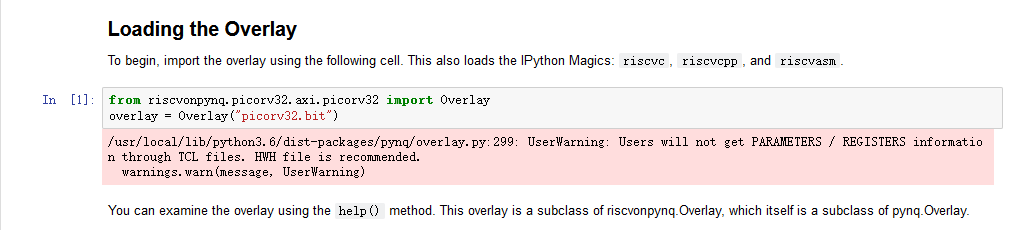

装好Overlay后,打开RISC-V-Examples/PicoRV32 Processor Mixed-Memory Processor Demo.ipynb,这是使用DRAM和BRAM混合储存器的示例工程。实际上代码与使用只BRAM的工程类似,只不过使用了不同的bit文件。

开始时下载bit文件,在这个过程中所有驱动都会注册完成。

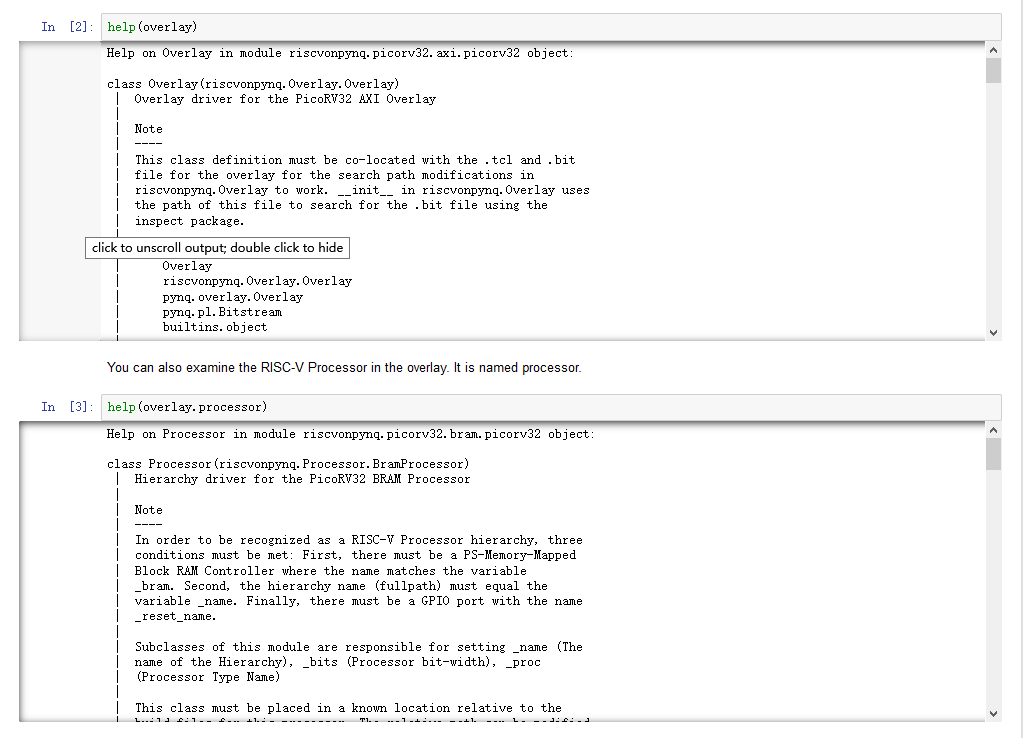

可以用help函数查看Overlay和processor的有关信息,可以看到,这里的Overlay和processor使用了本项目设计的驱动,这说明驱动注册成功了。

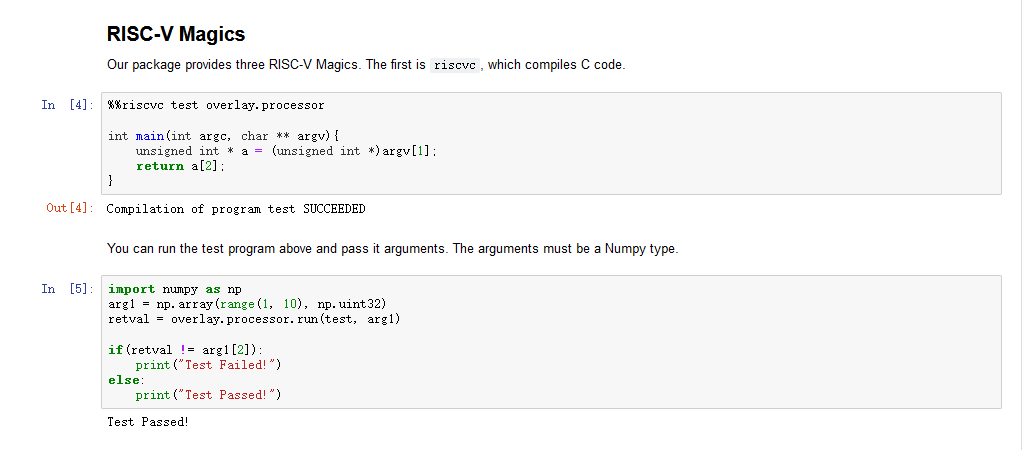

在Notebook中包含了一段C程序,作用是返回一个数组的第二个元素。可以看到我们使用了python magics来声明并编译一段C程序,这和PYNQ本身对Microblaze核的编程方法类似。然后调用processor的run方法将程序装载进RAM中来运行picoRV32。

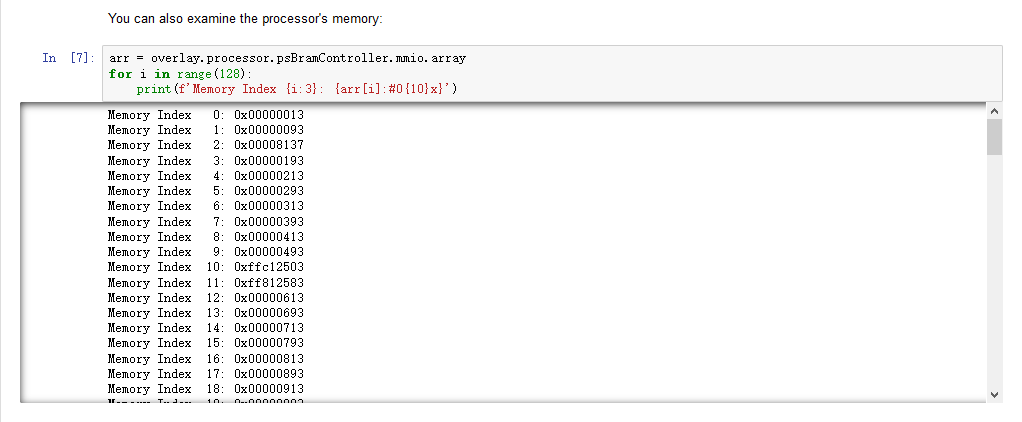

我们也可以调用BRAM controller的mmio来看看内存的情况。在这之后也有使用C++和汇编程序的例子,这里不作赘述,读者通过执行Jupyter Notebook中的代码来体验。

Overlay详解

- PS与PL功能划分

PS部分主要是用Python通过PYNQ框架控制PL中各IP的运行。

PL部分则例化一个pcioRV32核和和BRAM。

- Vivado工程block design介绍

具体硬件设计是这样的:

上图是项目的总体布局,下图是processor展开后的内容。

其中BRAM是一个双口RAM,它两端连接的是PS和picoRV32。另外,可以看到PS的GPIO连接的是processor的复位端,当二进制程序装入BRAM后,复位picoRV32,使它运行程序。picoRV32运行结束后,会触发一个中断。利用这个设计,可以例化许多RISC-V核心,并让其运行独立的程序,实现一个灵活可配置的众核处理器,事实上已经有用这种方法实现了例化超过一千个RISC-V核的项目。

在Processor内部,picoRV32通过AXI总线来访问其他IP,可以使用AXI总线来给它增加各种各样不同的外设。在这里,本项目只是添加了另一个内存(通过PS的HP AXI 0接口访问内存控制器)。

另外,这里的picoRV32核心的运行频率可以通过利用AXI总线配置时钟资源来调整。

注意:RISC-V核的hierarchy名字必须为processor,并且processor中的复位模块必须为rscvReset。如果改动这些名字,必须修改对应的驱动源文件,否则不能正确加载驱动。

Overlay API介绍

在此工程中,通过riscvc、riscvcpp和riscvasm这三个python magics来编译一段程序。例如:%%riscvcpp test_cpp overlay.processor。其中test_cpp是程序的名字,overlay.processor是想要写入的RISCV核hierarchy的名字。然后在本cell中编写代码,运行后将调用前面安装的RISC-V的工具链编译。

编译成功后,利用processor的run方法运行程序。例如:overlay.processor.run(test_cpp, test_cpp_arg)。其中test_cpp是程序名字,test_cpp_arg是参数数组,它兼容numpy的类型。

对于更详细的解释,可以参看前面的tutorial中5个notebook和项目中的.py源文件。

编辑:hfy

-

Xilinx

+关注

关注

71文章

2164浏览量

121013 -

AXI

+关注

关注

1文章

127浏览量

16598 -

内存控制器

+关注

关注

0文章

39浏览量

8878 -

RISC-V

+关注

关注

44文章

2229浏览量

46034

发布评论请先 登录

相关推荐

RISC-V和arm指令集的对比分析

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

risc-v的发展历史

rIsc-v的缺的是什么?

RISC-V有哪些优点和缺点

RISC-V有哪些优缺点?是坚持ARM方向还是投入risc-V的怀抱?

解锁RISC-V技术力量丨曹英杰:RISC-V与大模型探索

什么是RISC-V?RISC-V的关键技术

Imagination:RISC-V CPU的重要力量

自制RISC-V源码与设计流程案例分析

自制RISC-V源码与设计流程案例分析

评论