某些应用程序小,可以全部放在Zynq-7000的256KB OCM上运行。这时,修改FSBL,可以把APP和FSBL编译成一个可执行文件,FSBL初始化硬件后,就直接运行应用程序。

这种情况下,单板没有DDR。

1. DDR

缺省的FSBL,使用宏XPAR_PS7_DDR_0_S_AXI_BASEADDR屏蔽了很多代码,不会初始化存储设备,比如QSPI Flash,也不会加载FPGA。

对于只使用OCM上运行程序的场景,需要减少宏XPAR_PS7_DDR_0_S_AXI_BASEADDR屏蔽的代码,也就是只屏蔽DDRInitCheck()的定义和调用就可以了。

下面屏蔽DDRInitCheck()的调用

int main(void)

{

... ...

#ifdef XPAR_PS7_DDR_0_S_AXI_BASEADDR

/*

* DDR Read/write test

*/

Status = DDRInitCheck();

if (Status == XST_FAILURE) {

fsbl_printf(DEBUG_GENERAL,"DDR_INIT_FAIL /r/n");

/* Error Handling here */

OutputStatus(DDR_INIT_FAIL);

/*

* Calling FsblHookFallback instead of Fallback

* since, devcfg driver is not yet initialized

*/

FsblHookFallback();

}

#endif // XPAR_PS7_DDR_0_S_AXI_BASEADDR

... ...

}

下面屏蔽DDRInitCheck()的定义

#ifdef XPAR_PS7_DDR_0_S_AXI_BASEADDR

u32 DDRInitCheck(void)

{

... ...

}

#endif // XPAR_PS7_DDR_0_S_AXI_BASEADDR

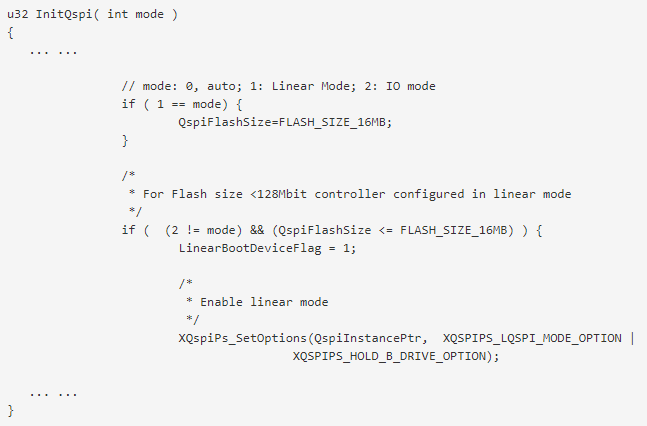

2. 初始化QSPI

QSPI Flash大于16MB时,超出了线性模式的寻址范围。FSBL会把QSPI初始化为IO模式。

如果没有DDR,会导致不能加载FPGA。为了解决这个问题,在加载FPGA前,强行把QSPI Flash设置成16MB大小,初始化为线性模式。加载FPGA后,再按正常模式初始化QSPI Flash。因此,FPGA的bit文件,必须放在QSPI Flash的前16MB里。

在第一次初始化QSPI Flash时,强行把QSPI Flash初始化为线性模式,可以正常加载FPGA。

int main(void)

{

... ...

if (BootModeRegister == QSPI_MODE) {

fsbl_printf(DEBUG_GENERAL,"Boot mode is QSPI/n/r");

InitQspi(1);

MoveImage = QspiAccess;

fsbl_printf(DEBUG_INFO,"QSPI Init Done /r/n");

}

... ...

}

3. 运行应用程序

在FsblHandoff()里,关闭看门狗后,执行应程序。执行应用程序前,按原来的模式初始化QSPI Flash,也就是小于等于16MB时,初始化为线性模式;大于16MB时,初始化为IO模式。

void FsblHandoff(u32 FsblStartAddr)

{

... ...

/*

* FSBL user hook call before handoff to the application

*/

Status = FsblHookBeforeHandoff();

if (Status != XST_SUCCESS) {

fsbl_printf(DEBUG_GENERAL,"FSBL_HANDOFF_HOOK_FAIL/r/n");

OutputStatus(FSBL_HANDOFF_HOOK_FAIL);

FsblFallback();

}

#ifdef XPAR_XWDTPS_0_BASEADDR

XWdtPs_Stop(&Watchdog);

#endif

// Hank: Add customer's application code here

// We can access FPGA register here.

int main_app();

InitQspi( 0 );

main_app();

/*

* Clear our mark in reboot status register

*/

ClearFSBLIn();

... ...

}

4. 进一步优化

还可以根据单板情况,进一步优化。比如,可以屏蔽NOR Flash的代码,PCW_SILICON_VERSION_1和PCW_SILICON_VERSION_2的数据和代码。FSBL的初始化代码和数据,只在上电时被使用,也可以释放出来更应用程序使用。

-

FPGA

+关注

关注

1630文章

21796浏览量

605527 -

FlaSh

+关注

关注

10文章

1642浏览量

148530 -

DDR

+关注

关注

11文章

715浏览量

65476

发布评论请先 登录

相关推荐

【Z-turn Board试用体验】+Zynq7000启动流程介绍

Zynq-7000 SoC提供 FPGA 资源

如何为Zynq-7000 soc寻找USB主机驱动程序?

Zynq-7000设置数字是什么意思?

Xilinx Zynq-7000特性参数

Zynq-7000系列特征概述

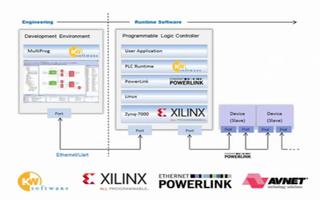

基于Zynq-7000平台运行SoftPLC的解决方案

Zynq-7000的256KB OCM应用程序运行

Zynq-7000的256KB OCM应用程序运行

评论