周丽娜(Ally Zhou)女士拥有十多年 FPGA 设计、EDA 工具和多年客户支持的经验。Ally 曾先后在同济大学,芬兰米凯利理工学院和复旦大学求学,获得工学硕士学位。加入赛灵思公司之前,曾在 Synopsys 工作,主要负责 FPGA 综合和 ASIC 原型验证方案的支持。

赛灵思技术市场专家周丽娜(Ally Zhou)

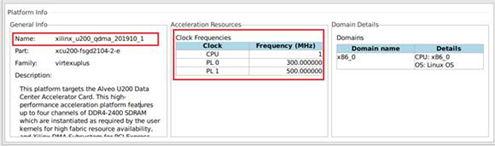

在本篇文章中,我们将介绍如何使用 Vitis 在 Alveo 板卡上开发和部署硬件加速应用。包括可用资源及文档,如何安装所需的开发工具和软件包,以及如何使用赛灵思 Github 加速用例。视频演示部分会向大家详细展示如何使用 Vitis 图形化界面和命令行流程在 Alveo U200 板卡上进行加速用例的开发和部署。

开始前的准备工作

了解和安装 Alveo 板卡

您可以在赛灵思官网主页下载产品选型手册,适用的加速应用,上手指南,支持的工具等文档。在开始之前请先查阅上图所示 UG1301 文档正确安装 Alveo 板卡。

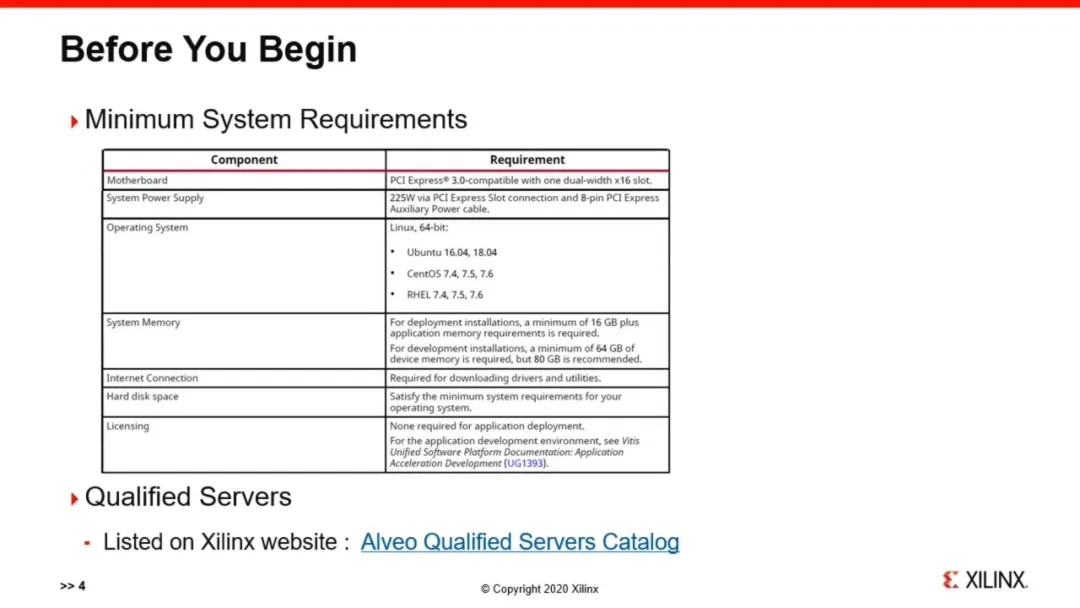

系统配置很重要

赛灵思提供了关于系统配置的详细信息,包括认证的服务器,支持的操作系统,最低系统配置要求等等,在开始安装 Alveo 板卡前,请务必保证你的系统满足了文档列明的最低要求。

开始您的设计

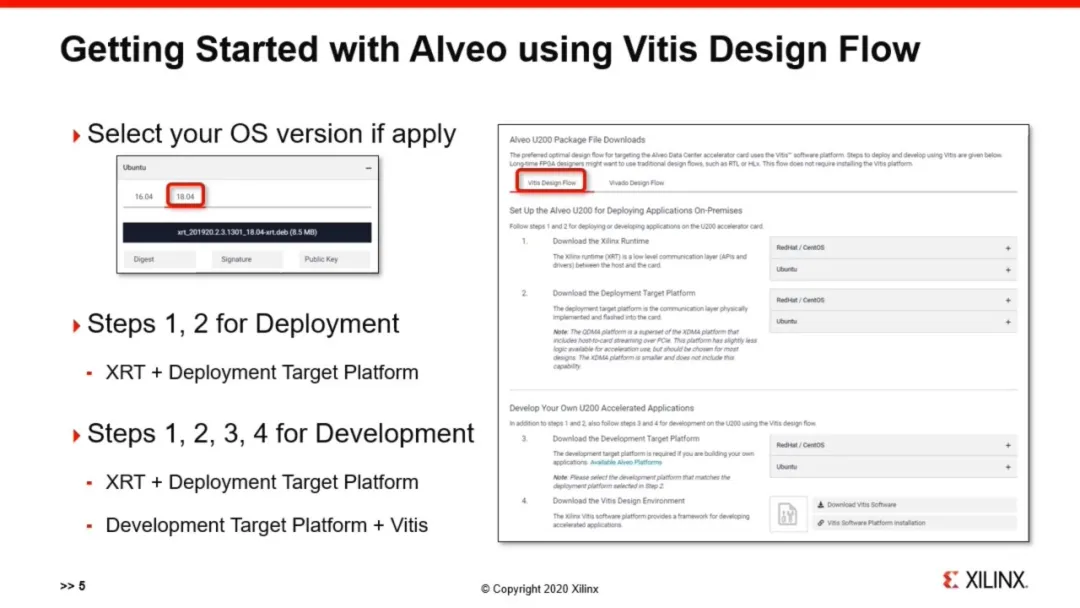

在 Alveo 的主页(链接见前文)上,选择了你想要使用的 Alveo 板卡后,点开“Getting Started” 标签,就可以发现安装这块板卡所需的步骤和相应的软件包。step by step, so easy.

软硬件环境就绪

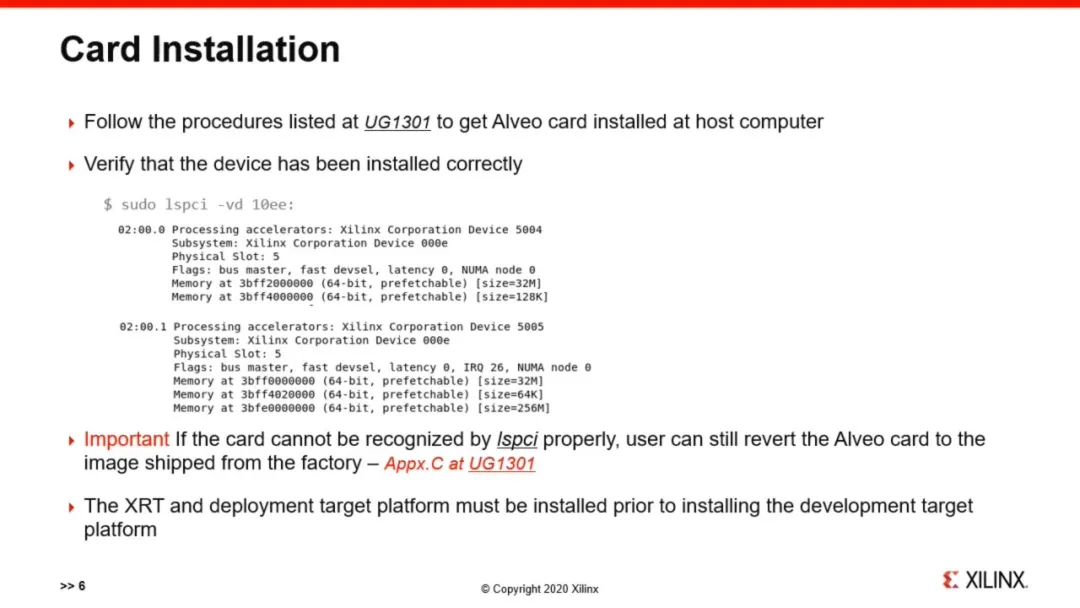

一旦板卡已经被成功安装,并装好了所需软件,你可以看到类似屏幕显示的信息。再次强调,必须严格按照文档或网页列明的步骤来安装你的板卡。

编辑:hfy

-

FPGA

+关注

关注

1630文章

21759浏览量

604373 -

asic

+关注

关注

34文章

1204浏览量

120565 -

赛灵思

+关注

关注

32文章

1794浏览量

131346 -

Vitis

+关注

关注

0文章

147浏览量

7461

发布评论请先 登录

相关推荐

【米尔FZ3深度学习计算卡试用体验】搭建Vitis Ai系统平台并测试

Vitis 统一软件平台简介 可实现最高的AI推断性能

如何在Vitis中封装加速平台?

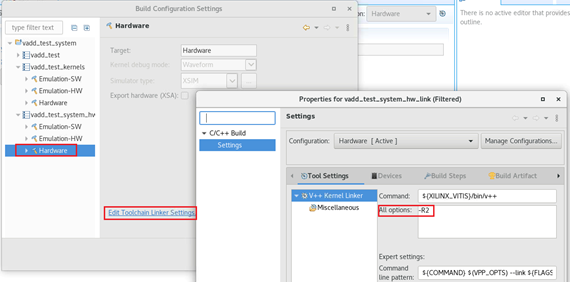

怎么在Vitis中设定Kernel的频率?

怎么在Vitis加速设计中为Kernel创建面积约束

基于Vitis HLS的加速图像处理

基于软件的Vitis AI 2.0加速解决方案

如何在Vitis中设定Kernel的频率

基于vitis的模型编译器在FPGA上加速投产进程

在赛灵思FPGA SoC平台上使用VITIS AI加速人工智能应用

浅谈Vitis AI 3.5发布亮点

Vitis 统一软件平台文档:应用加速开发

Vitis AI RNN用户指南

Vitis在Alveo 板卡上加速应用案例

Vitis在Alveo 板卡上加速应用案例

评论