从 2019.2 版开始,赛灵思 SDK 开发环境已统一整合到全功能一体化的Vitis™ 统一软件平台中。

马上开始将工程从赛灵思 SDK 移植到 Vitis 吧。

Vivado 工程升级

工程必须先备份,然后才能移植。

请打开旧版本的 Vivado 工程,选择执行升级,如下图所示。

浏览到“Reports -> Report IP Status”

浏览到“IP status”窗口,检查状态,然后升级 IP

生成比特流,然后浏览到“File -> Export -> Export Hardware”以导出比特流和 XSA

将 SDK 工程导入 Vitis 工作空间

启动 Vitis IDE。

浏览到“file -> Import”,导入旧版本的赛灵思 SDK 工程

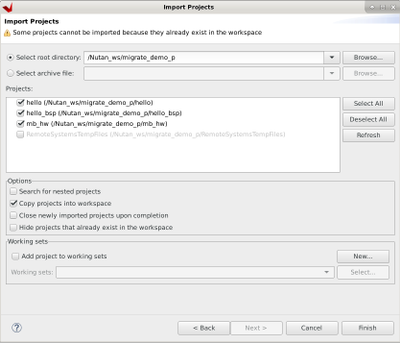

在下一个窗口中选择根目录和要导入的工程。

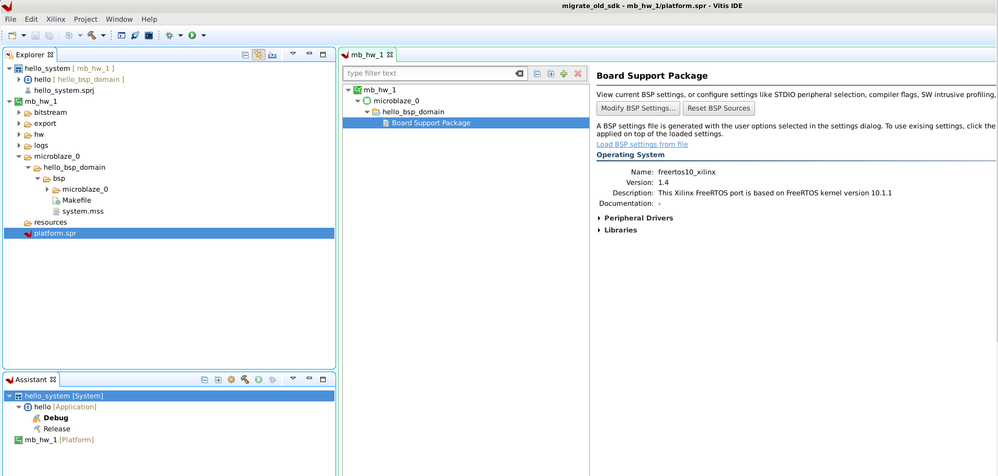

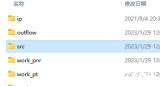

导入成功后,用户即可看到导入的应用工程和平台工程,如下图所示。

导入的板级支持包现已存在于平台工程内,如下图所示。

选择从 Vivado 导出的 XSA 文件,然后单击“OK”。

右键单击平台工程,然后选择“Build Project”。

重新构建应用工程。

编辑:hfy

-

赛灵思

+关注

关注

32文章

1794浏览量

131287 -

SDK

+关注

关注

3文章

1037浏览量

45967

发布评论请先 登录

相关推荐

易灵思FPGA产品的主要特点

Passion!赛思时钟服务器助力多项国家特高压工程实现电力“闪送”

赛思快讯 | 发展新质生产力问道赛思?赛思如何下好“创新棋”?

SDK 1.0移植到eclipse失败,如何修改makefile文件呢?

把0.9.3的sdk的程序移植到1.0的sdk上,重启后一直挂机的原因?

将应用程序从NoOS SDK移植到RTOS SDK遇到异常怎么解决?

JoyLink移植到esp8266当中,esp8266使用的是RTOS_SDK还是NON_RTOS_SDK?

NucleiStudio_IDE下调试一直报all ones错误怎么解决?

易灵思RAM使用--Update5

易灵思RAM使用--Update4

如何把赛灵思SDK工程移植到Vitis

如何把赛灵思SDK工程移植到Vitis

评论