由于XDC约束是按顺序应用的,并且基于明确的优先级规则进行优先级排序,因此必须仔细检查约束的顺序。

如果多个物理约束发生冲突,则最新约束将获胜。 例如,如果通过多个XDC文件为I / O端口分配了不同的位置(LOC),则分配给该端口的最新位置优先。

Vivado IDE可全面了解您的设计。 要逐步验证您的约束:

1.运行相应的报告命令。

2.查看Tcl控制台或“消息”窗口中的消息。

推荐的约束顺序

建议:无论是为设计使用一个还是多个XDC文件,都按以下顺序组织约束。

## Timing Assertions Section # Primary clocks # Virtual clocks # Generated clocks # Clock Groups # Bus Skew constraints # Input and output delay constraints ## Timing Exceptions Section # False Paths # Max Delay / Min Delay # Multicycle Paths # Case Analysis # Disable Timing ## Physical Constraints Section # located anywhere in the file, preferably before or after the timing constraints # or stored in a separate constraint file

从时钟定义开始。 必须先创建时钟,然后才能将它们用于任何后续约束。 声明之前对时钟的任何引用都会导致错误,并忽略相应的约束。 在单个约束文件中以及设计中的所有XDC文件(或Tcl脚本)中都是如此。

约束文件的顺序很重要。 您必须确保每个文件中的约束不依赖于另一个文件的约束。 如果是这种情况,则必须最后读取包含约束依赖项的文件。 如果两个约束文件具有相互依赖关系,则必须将它们手动合并到一个包含正确序列的文件中,或者将文件分成几个单独的文件并正确排序。

编辑约束顺序

Vivado IDE约束管理器将任何已编辑的约束保存回XDC文件中的原始位置,但不会保存在Tcl脚本中。 任何新约束都保存在标记为目标的XDC文件的末尾。 在许多情况下,当约束集包含多个XDC文件时,目标约束文件不是列表中的最后一个文件,并且在打开或重新加载设计时不会最后加载。 因此,保存在磁盘上的约束序列可能与之前在内存中的约束序列不同。

重要信息:您必须验证存储在约束文件中的最终序列是否仍按预期工作。 如果必须修改序列,则必须通过直接编辑约束文件来修改它。 这对时序约束尤为重要。

约束文件顺序

在没有任何IP的项目流程中,所有约束都位于约束集中。 默认情况下,Vivado IDE中显示的XDC文件(或Tcl脚本)的顺序定义了将elaborated design或synthesized design加载到内存时工具使用的读取顺序。 首先读取列表顶部的文件,最后读取底部的文件。 您只需在IDE中选择文件并将其移动到列表中的所需位置即可更改顺序。

例如,在图1中,使用拖放操作将文件wave_gen_pin.xdc移动到文件wave_gen_timing.xdc之前。

The equivalent Tcl command is:

reorder_files -fileset constrs_1 -before [get_files wave_gen_timing.xdc] [get_files wave_gen_pins.xdc]

在非项目模式下,read_xdc调用的顺序决定了约束文件的计算顺序。

Constraint Files Order with IP Cores

许多IP内核随附一个或多个XDC文件。 在RTL项目中生成此类IP内核时,还会在各种设计编译步骤中使用其XDC文件。

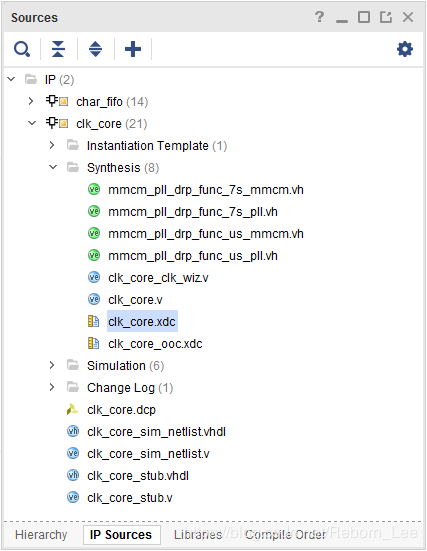

例如,图2显示项目中的一个IP核带有一个XDC文件。

默认情况下,在用户XDC文件之前读入IP XDC文件。 以这种方式处理它允许IP创建可在XDC中引用的时钟对象。 它还允许您覆盖由IP内核设置的物理约束,因为在IP之后评估用户约束。 对于依赖于由用户或其他IP创建的时钟对象的IP核,此顺序有一个例外(例如,get_clocks -of_objects [get_ports clka])。 在这种情况下,在用户文件之后读取IP XDC。

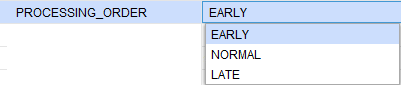

此行为由PROCESSING_ORDER属性控制,为每个XDC文件设置:

•EARLY:必须先读取的文件

•NORMAL:默认

•LATE:必须最后读取的文件

IP XDC将其PROCESSING_ORDER属性设置为EARLY或LATE。 没有哪个IP提供属于NORMAL约束组的XDC文件。 对于属于同 一PROCESSING_ORDER组的用户XDC(或Tcl)文件,Vivado IDE中显示的相对顺序决定了它们的读取顺序。 可以通过移动Vivado IDE约束集中的文件或使用reorder_files命令来修改组中的顺序。

对于属于同一PROCESSING_ORDER组的IP XDC文件,顺序由IP内核的导入或创建顺序确定。 创建项目后,无法更改此顺序。

最后,用户组和IP XDC PROCESSING_ORDER组之间的相对顺序如下:

1.标记为EARLY的用户约束

2.标记为EARLY的IP约束(默认)

3.标记为NORMAL的用户约束

4.标记为LATE的IP约束(包含时钟依赖性)

5.标记为LATE的用户约束

注意:将其PROCESSING_ORDER设置为LATE(以便在用户约束后进行处理)的IP XDC文件命名为

下图显示了如何设置PROCESSING_ORDER属性的示例:

The equivalent Tcl command is:

set_property PROCESSING_ORDER EARLY [get_files wave_gen_pins.xdc]

建议:使用Tcl控制台中的report_compile_order -constraints命令报告由工具根据上述属性确定的XDC文件读取顺序,包括IS_ENABLED,USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION。

Changing Read Order

要在约束集中更改XDC文件或非托管Tcl脚本的读取顺序,请执行以下操作:

1. 在“源”窗口中,选择要移动的XDC文件或Tcl脚本。

2. 将文件拖放到约束集中的所需位置。

对于图1中所示的示例,等效的Tcl命令是:

reorder_files -fileset constrs_1 -before [get_files wave_gen_timing.xdc] [get_files wave_gen_pins.xdc]

在非项目模式下,read_xdc或source命令的顺序决定了约束文件的读取顺序。

如果使用带有约束的IP内核,则会自动处理两组约束,如下所示:

•不依赖于时钟的约束被分组到XDC文件中,PROCESSING_ORDER设置为EARLY,

•依赖于时钟的约束在PROCESSING_ORDER设置为LATE的XDC文件中分组。

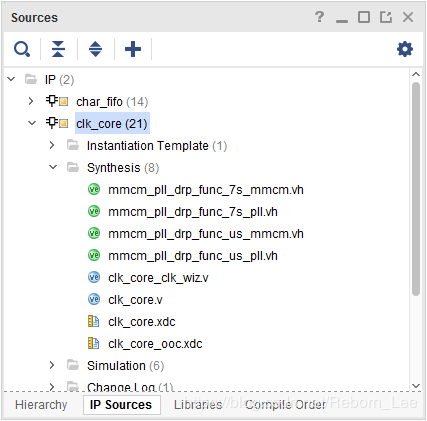

默认情况下,用户XDC文件属于PROCESSING_ORDER NORMAL组。 它们在EARLY XDC文件之后和LATE XDC文件之前加载。 对于每个PROCESSING_ORDER组,IP XDC文件的加载顺序与IP Sources窗口中IP核的列表顺序相同。 例如,下图显示了XDC文件附带的项目IP内核之一。

打开设计时,日志文件显示最后加载了IP XDC文件:

Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/clk_core/clk_core.xdc] for cell 'clk_gen_i0/clk_core_i0/inst' Finished Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/clk_core/clk_core.xdc] for cell 'clk_gen_i0/clk_core_i0/inst' Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo.xdc] for cell 'char_fifo_i0/U0' Finished Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo.xdc] for cell 'char_fifo_i0/U0' Parsing XDC File [C:/project_wave_gen_hdl.srcs/constrs_1/imports/verilog/wave_gen_timing.xdc] Finished Parsing XDC File [C:/project_wave_gen_hdl.srcs/constrs_1/imports/verilog/wave_gen_timing.xdc] Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo_clocks.xdc ] for cell 'char_fifo_i0/U0' Finished Parsing XDC File [C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo_clocks.xdc ] for cell 'char_fifo_i0/U0' Completed Processing XDC Constraints

与用户XDC文件不同,您无法直接更改属于同一PROCESSING_ORDER组的IP XDC文件的读取顺序。 如果必须修改订单,请执行以下操作:

1. 禁用相应的IP XDC文件(IS_ENABLED设置为false)。

2. 复制他们的内容。

3. 将内容粘贴到约束集中包含的一个XDC文件中。

4. 在需要的地方使用完整的分层网表对象路径名更新复制的IP XDC命令。 这样做是必需的,因为IP XDC约束以这样的方式编写,即它们可以作用于IP实例。

5. 查看以特殊方式处理范围约束的get_ports查询。

编辑:hfy

-

Vivado

+关注

关注

19文章

808浏览量

66319 -

xdc

+关注

关注

1文章

24浏览量

5916

发布评论请先 登录

相关推荐

无法在XDC文件中设置maxdelay约束

Vivado忽略了约束文件

在使用Vivado GUI实现和分配引脚信息后xdc约束文件中看不到结果

关于XDC约束文件,你需要知道的几点

ISE约束导入vivado总共分几步

Vivado IDE全面了解XDC文件的约束顺序

Vivado IDE全面了解XDC文件的约束顺序

评论