作者:猫叔

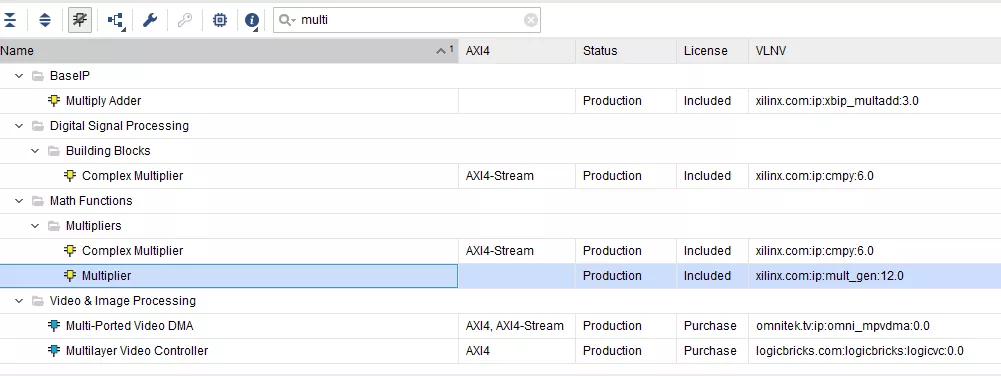

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

当然,我们也可以直接使用*符合来进行乘法,对于无符号的乘法

reg [7:0] ubyte_a; reg [7:0] ubyte_b; (* use_dsp48="yes" *) output reg[15:0] u_res; always @ ( posedge clk ) begin if(rst) u_res <= 'b0; else u_res <= ubyte_a * ubyte_b; end

有符号乘法可以在Verilog中使用signed来标注。

reg signed [7:0] byte_a;

reg signed [7:0] byte_b;

(* use_dsp48="yes" *)

reg signed [15:0] res;

always @ ( posedge clk ) begin

if(rst)

res <= 'b0;

else

res <= byte_a * byte_b;

end

当然我们也要理解有符号数乘法的原理,其实就是扩位乘法,把高位都补充为符号位。

有符号数乘法:

reg [7:0] ubyte_a;

reg [7:0] ubyte_b;

(* use_dsp48="yes" *)

reg [15:0] res_manul;

always @ ( posedge clk ) begin

if(rst)

res_manul <= 'b0;

else

res_manul <= {{8{byte_a[7]}},ubyte_a} * {{8{ubyte_b[7]}},ubyte_b};

end

关于乘法输出的位宽,我们知道,两个8bits的无符号数乘法,结果的位宽是16bits,但对于两个8bits有符号数的乘法,只要两个数不同时为-128,即二进制0b1000_0000,那么输出结果的高两位都是符号位,我们只需要取低15bits即可。因此,如果我们可以保证两个输入的乘数不会同时为有符号数所能表示的负数最小值,那么乘法结果的高两位都是符号位,只取其中一位即可。

编辑:hfy

-

dsp

+关注

关注

555文章

8124浏览量

354496 -

FPGA

+关注

关注

1643文章

21925浏览量

612555 -

乘法器

+关注

关注

9文章

211浏览量

37713

发布评论请先 登录

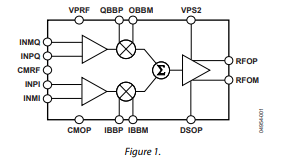

ADL5390 RF矢量乘法器技术手册

ADA-28F00WG乘法器Marki

求助,LMX2572LP参考时钟路径中的乘法器MULT的输入频率范围问题求解

请问如何用VCA810实现模拟乘法器?

CDCF5801A具有延迟控制和相位对准的时钟乘法器数据表

CDCS503带可选SSC的时钟缓冲器/时钟乘法器数据表

SN5497、SN7497同步6位二进制速率乘法器数据表

CMOSBCD速率乘法器CD4527B TYPES 数据表

CMOS二进制速率乘法器CD4089B TYPES 数据表

FPGA中乘法器的原理分析

FPGA中乘法器的原理分析

评论