Zynq中AXI4-Lite功能

AXI4-Lite接口是AXI4的子集,专用于和元器件内的控制寄存器进行通信。AXI-Lite允许构建简单的元件接口。这个接口规模较小,对设计和验证方面的要求更少。AXI4-Lite接口的特性如下:

1) 突发长度为1。

2) 所有访问数据的宽度和数据总线宽度相同。

3) 支持数据总线宽度为32位或64位。

4) 所有的访问相当于AWCACHE和ARCACHE等于b0000(非缓冲和非缓存)。

5) 不支持互斥性操作。

Zynq中AXI-Stream功能

AXI-Stream协议作为一个标准接口,用于连接数据交换元件。接口将产生数据的一个主设备和接收数据的一个从设备连接。当很多元件和从元件连接时,也能使用该协议。协议支持使用具有相同设置共享总线的多个数据流。该协议允许建立一个互联结构。

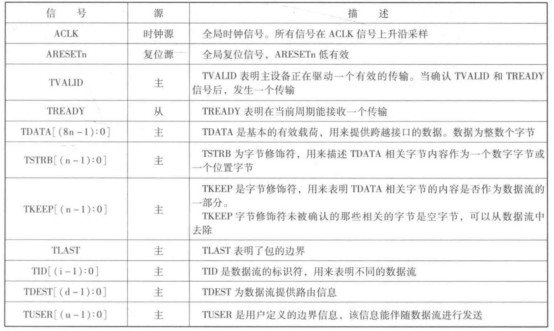

接口描述如下:

TVALID和TREADY握手信号用来确定跨接口数据的时间。双向的流控制机制使得主设备和从设备能够控制跨接口所发送的数据和控制信息的速度

一个主设备不允许在确认TVALID前,等待确认TREADY。一旦确认TVALID,必须一致保持这个状态,知道产生握手信号。

在确认相应的TREADY信号前,一个从设备允许等待确认TVALID。

如果从设备确认了TREADY,在TVALID信号确认前,允许不确认TREADY。

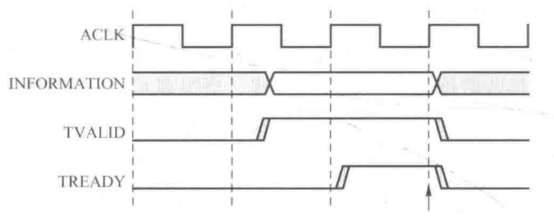

1. TVALID在TREADY前的握手信号

上图给出了TVALID在TREADY前的握手信号,从图中可以看出,主设备给出数据和控制信号,并且确认TVALID信号为高。一旦主设备确认了VALID,来自主设备的数据或从设备控制信息保持不变。这种状态一直保持到从设备驱动TREADY信号为高位置,它用来表示从设备可以接收数据和控制信号。在这种情况下,一旦从设备确认TREADY为高,则开始进行传输。

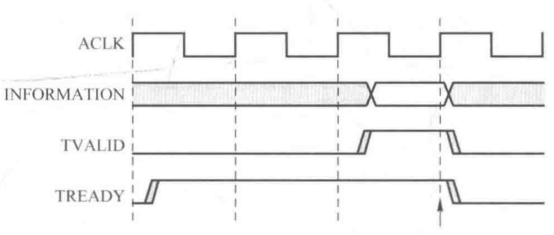

2. TREAD在TVALID之前的握手信号

上图给出了TREADY在TVALID前的握手信号,从图中可以看出,在数据和控制信息有效前,从设备驱动TREADY信号为高。这表示,从设备可以在一个ACLK周期内接收数据和控制信息。在这种情况下,一旦主机确认TVALID信号为高,则开始传输。

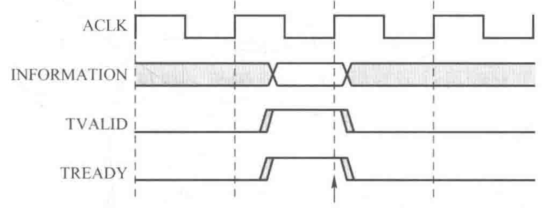

3. TVALID和TREADY握手

上图给出了TVALID和TREADY握手的图,在ACLK一个周期内,主设备确认TVALID为高,从设备确认TREADY为高,则开始传输。

本文转自: 瓜大三哥,作者:米果不回来

-

Zynq

+关注

关注

10文章

610浏览量

47187 -

AXI

+关注

关注

1文章

127浏览量

16631 -

AXI4

+关注

关注

0文章

20浏览量

8898 -

控制寄存器

+关注

关注

0文章

34浏览量

11491

发布评论请先 登录

相关推荐

Xilinx zynq AXI总线全面解读

请问可以使用AXI-Stream Broadcaster作为AXI开关吗?

AXI4-lite端口可以保持未连接状态吗?

AXI-stream数据传输过程

AXI-Stream代码

关于AXI4-Stream协议总结分享

AXI4 、 AXI4-Lite 、AXI4-Stream接口

如何在Vitis HLS中使用C语言代码创建AXI4-Lite接口

使用AXI4-Lite将Vitis HLS创建的IP连接到PS

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】

自定义AXI-Lite接口的IP及源码分析

Zynq中AXI4-Lite和AXI-Stream功能介绍

Zynq中AXI4-Lite和AXI-Stream功能介绍

评论