时序电路

首先来看两个问题:

1.为什么CPU要用时序电路,时序电路与普通逻辑电路有什么区别。

2.触发器、锁存器以及时钟脉冲对时序电路的作用是什么,它们是如何工作的。

带着这两个问题,我们从头了解一下逻辑电路。要了解逻辑电路,首先我们便要了解组成逻辑电路的基本单位:逻辑门。

逻辑门

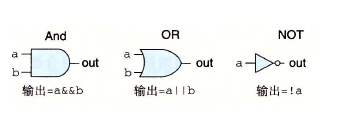

逻辑门是数字电路组成的基本单元,它们的输出是它们输入位值的布尔函数。最常用的逻辑门便是我们熟知的与、或、非。

对于与门,只有a、b输入都为1时,输出才为1。

对于或门,输入a、b只要有一个为1,输出便为1。

对于非门,若输入为1则输出为0,输入为0则输出为1。

以上三种是最基本的逻辑门,我们可以通过它们的组合来实现复杂的逻辑推演,最简单的比如与或、异或等。再复杂的逻辑,都可以用最基本的逻辑的特定组合实现出来,就像我们应用层工程师靠有限的语法可以创造出近乎无限的应用一样。

逻辑门总是活动的,一旦一个门的输入变化了,在很短的时间内,输出便会相应的变化。

使用很多的逻辑门构建成一张网,便得到了一个实现的复杂逻辑的计算块(computational Block),称为组合电路。组合电路的构成遵循以下原则:

1. 每个逻辑门的输入必须连接了一个系统的输入、某个存储单元的输出或某个逻辑门的输出(三选一)。

2. 两个或多个逻辑门的输出不能连接在一起,否则可能产生互相矛盾的信号造成错误或电路故障。

3. 这个网必须是无环的,也就是说不能有回路,否则会使网的计算逻辑有歧义。

了解了基本的逻辑门和组合电路的概念,我们再介绍一下电路中的控制信号是如何实现的。

控制信号

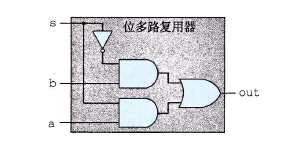

我们说过再复杂的逻辑也可以靠最基本的逻辑组合而成,输入输出的控制逻辑也不例外。为了更好的理解控制信号是如何工作的,我们介绍一种非常有用的组合电路:位多路复用器。

其中的 s 输入控制着两个与门。其中位于上方的与门的逻辑是 !s && b ,位于下方的与门的逻辑是 s && a 。

也就是说当 s 的输入为 1 时,b的输入是无法到达或门的, 0&&b 恒为零。此时 a 的输入便是整个电路的输出。

反之当 s 输入为 0 时,a 的输入是无法到达或门的 ,0&&a 恒为零。此时 b 的输入便是整个电路的输出。

可以看到 s 输入的电位高低直接决定着 a、b 中哪个输入有效,这便是控制信号工作的一个典型例子。

看到控制信号是如何工作的,我们来假想一下简单的寄存器是如何依赖一个时钟控制信号工作的。一个时钟信号周期的由低电平变为高电平再由高电平变为低电平。

以该信号作为寄存器的控制信号,寄存器内每一位输入位都与该信号进行与逻辑后再进入寄存器,那么可以想象,在时钟周期内的低电平部分,任何信号无法写入寄存器,等待时钟信号变为高电平时寄存器才变为可写入状态。这就是一个简单的触发器了,随着时钟信号周而复始的改变着自己的状态。

当然真正的触发器的实现比这复杂的多,这里只是方便理解举了最简单的例子。

明白了上述基本概念,我们看一下普通组合逻辑电路与时序电路的区别。

普通组合逻辑电路与时序电路的区别

1.毛刺容忍

组合逻辑电路从本质上讲,不存储任何信息。它们只是简单的响应输入信号,产生符合输入的某个逻辑表达式结果的输出。

而时钟电路是拥有自己的状态的,时序电路某一个状态除了依赖当前的输入外,还依赖电路的上一个状态。

而我们想要电路拥有自己的状态并可以基于这个状态进行计算,必须在组合逻辑电路中引入存储设备和控制存储设备的周期性变化的时钟信号。

引入存储设备是容易理解的,没有存储设备的电路当然是没有自己的状态的,因为它没有存储状态信息的载体,存储器就是存储电路状态信息的载体。

而时钟周期的作用相对就不是那么容易理解,我们举个例子来理解时钟信号的作用:

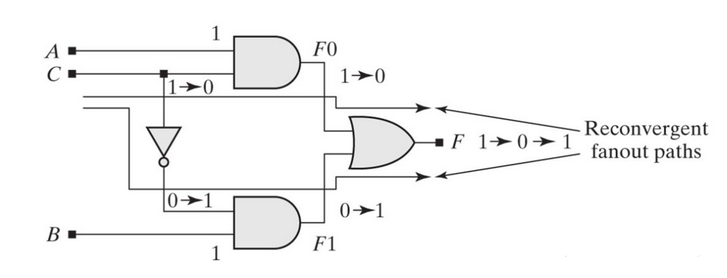

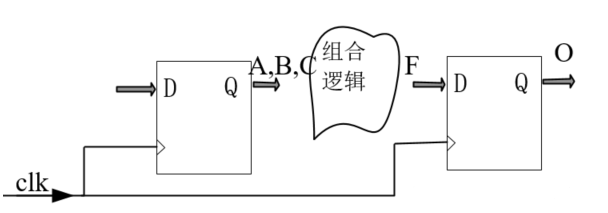

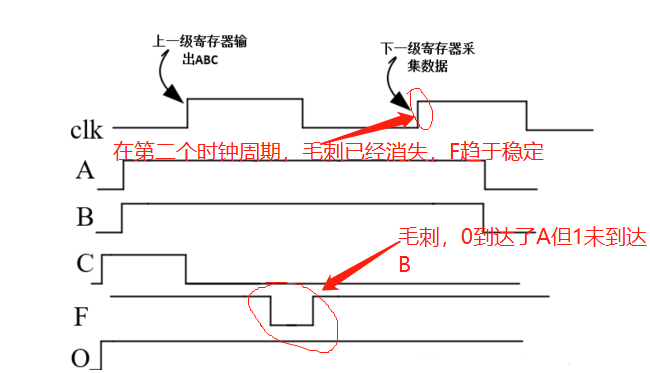

我们来看一个没有时钟信号的组合逻辑电路:

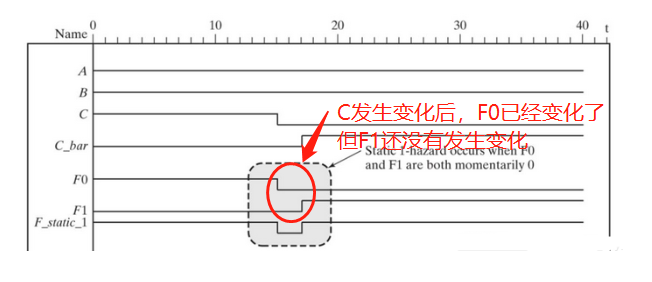

我们前面说过,逻辑门总是活动的,一旦一个逻辑门的输入改变,则输出会在很短的时间内发生改变。

但是需要注意的是,这个“很短时间内”的描述。由于元器件的质量/种类不同、路线的长度不同等物理因素的限制,不同的输入到达输出的时间是不同的。

比如图中,c 输入到达下方的与门与到达上方的与门的两条路线中,到达下方与门的路线多出了一个非门。那么 c 信号到达上方的与门自然要比到达下方的与门的速度快。

所以当 c 信号发生改变时,有一段时间内,F 端的输出是错误的,因为 A&&C 已经到达 F 端但 B&&!C 还没有到达,也就是说 F1 是比 F0 到达的慢的,存在延迟,如下图所示:

我们称这种情况为“毛刺”。

虽然毛刺出现的时间是很短暂的,但是对于一个电路系统的输出来说却是致命的。如果我们在发生毛刺的时间内将错误的输出写入存储器,接下来的逻辑会一错再错并让我们摸不到头脑。

而时序电路则不会出现上述问题,我们将A/B/C的输入到F的输出看作一个完整的动作,在一个时钟周期内完成。那么,A/B/C的输入将在时钟沿触发,F也将在时钟沿采集结果。而在采集结果时,F的输出已经跨越了毛刺处于稳定状态。当然,这样时一个钟周期内高电平持续的时间必须足够使 F 输出达到稳定状态。

这样,下一个动作(发生在下一个时钟周期)如果基于 F 输出,将得到正确的结果。这是时序电路与普通逻辑电路的区别之一:对毛刺的容忍。

可以看到,通过时钟周期,组合逻辑电路中输入的变化可以看作一个一个的动作。而在一个时钟周期内,电路完成一个最基本的动作,保证下个时钟周期的动作可以获取正确的电路状态。

如果无法理解电路按动作运转的意义,我们看一个非常简单的例子:

int a=0; int b=a;

我们需要将 a=0 执行完后,执行 b=a 才有意义。a=0没有执行完成或未执行时,b=a 的执行完全没有意义。这就是程序按指令运转的重要性,正如电路按动作运转的重要性。

时钟周期将一个一个的动作隔离开来,确保每个动作在执行时,上一个动作已经完全执行完成了。而存储器则记录电路的状态,每个动作的执行结果放在存储器中供下个动作使用。

这正是CPU所需要的,CPU执行一条一条的指令正可以看作一个一个的动作(当然这里并不是指的一条指令,CPU的基本动作是比指令更加细化的单位,尤其是在流水线的引入之后。指令正是由一个个基本的动作构成的,这些基本动作指的是取指令/指令译码/指令执行/访存/写回/PC增加等等)。

时钟周期像人类的心跳,CPU随着时钟节拍快速又有条不紊的运行。正如前面所说,一个时钟周期必须足够CPU完全完成耗时最长的基本动作,时钟周期对于不同的CPU来说并不是固定的,确定一个CPU的时钟周期也是一个非常复杂的任务。

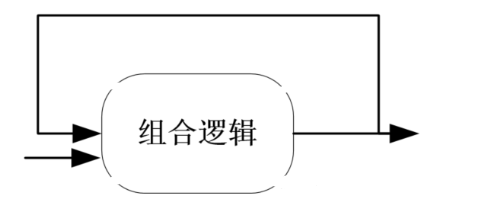

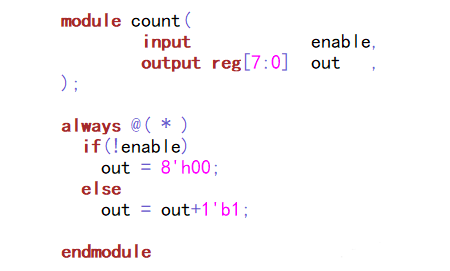

2.支持反馈逻辑

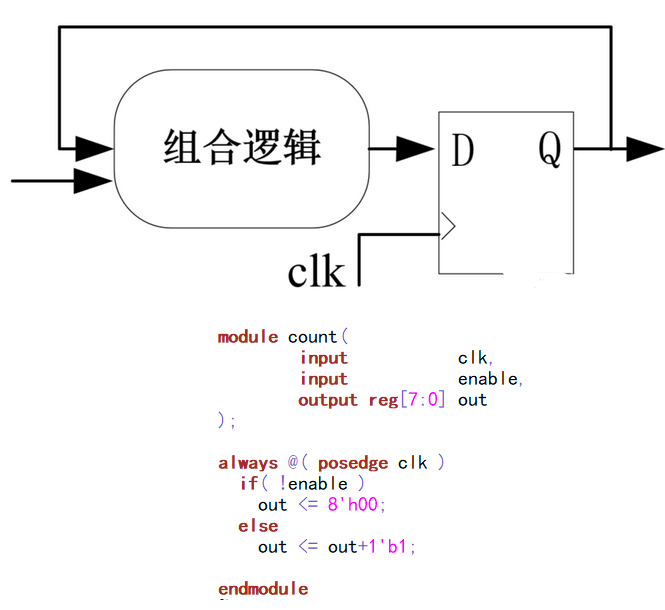

如果我们要实现一个计数器,如果用非时序电路实现是这样的:

上述电路是完全无法使用的,电路的下一个输出依赖电路现在时刻的状态,除了上一节所述的毛刺现象会造成结果的不可预计外,电路本身的逻辑存在死循环。

要支持反馈逻辑,必须使用寄存器将结果暂存起来,由时钟沿控制数据的反馈更新。

说完了时序电路的特性,我们看看时序电路如何组成处理器。

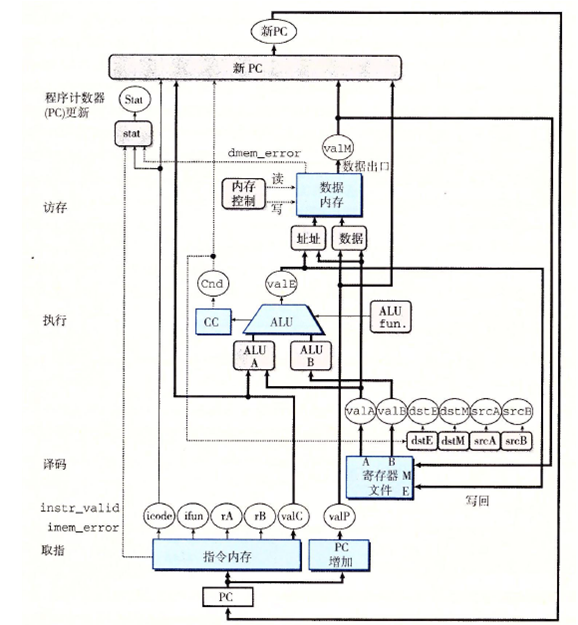

时序电路构成处理器

我们可以看到,一个最基本的处理器是这样一个电路:

1. 可以完成逻辑的运算。

2. 电路需要有自己的状态。

3. 每一个输出除了基于输入和处理逻辑外,还需要基于当前电路的状态。

时序电路可以很好的满足上述特性。对于时序电路来说,时钟脉冲便是电路的心跳,而寄存器是协同整个电路按心跳节拍运转的动脉瓣。

大多数时候,寄存器处于一种稳定状态,产生的输出等于它的当前状态。信号沿着寄存器前面的组合电路传播。这时产生一个新的寄存器输入,但当当前时钟脉冲处于低电位时,寄存器的输出仍保持不变。直到时钟脉冲变为高电位,输入信号便写入到寄存器中,成为下一个状态。直到下一个时钟上升沿,寄存器的状态和输出都不会发生改变。

电信号畅通无阻的在组合电路中传播,而寄存器就成为这种传播的屏障。只有在每个时钟的上升沿时,信号才可以通过寄存器进入下一个组合电路。

而一个个的组合电路执行着不同的动作,对于整个电路而言,时钟脉冲与寄存器的配合使得电路在每个动作执行完成后才会执行下一个动作。处理器在一个时钟周期内,执行完一个动作并把状态更新到寄存器。直到下一个时钟周期再执行下一个动作,此时上个动作已经完全执行完成了,而电路的最新状态也已经通过寄存器传播到了负责当前动作的电路中来。

换个角度,时钟周期保证了每个周期结束时,这个周期内的输入已经完整的转化为了输出。而这个输出保存在寄存器内供下个周期的动作使用。时钟周期和寄存器的配合将电路要执行的动作与动作之间隔离开来。每个动作的结尾会更新PC寄存器,而这也将成为下一个动作的开始。一个一个动作有条不紊的执行,周而复始。(这种描述仅适用于最简单的处理器模型,即一个时钟周期完成一条指令的执行的处理器。当引入流水线后,由于分支、控制指令等原因造成了流水线冒险,PC的更新有着更加完备的机制,而不是固定的在一条指令的最后更新)

上面便是一个最简单的处理器结构,左边标识了每部分电路对应的动作。

我们可以使一个时钟周期内执行完成整个指令执行(上述所有动作),这样下一个时钟周期执行下一条指令时可以保证上条指令可以执行完成。虽然这样时钟周期会长到让人难以接受,但它保证了指令流的正常流转。

我们可以想象,这样一个完整的过程是从读PC计数器数值并取指令开始的。PC计数器中的数值造成了后面一系列电路状态的变化,在PC不改变时,电路处于一个稳定的状态,也就是完整执行完一个指令的状态。

而当PC计数器一旦发生改变,将引起整个电路的新一轮的状态改变。指令执行的最后一个动作便是改变PC计数器,这样在下一个时钟周期,整个电路将执行新的指令。

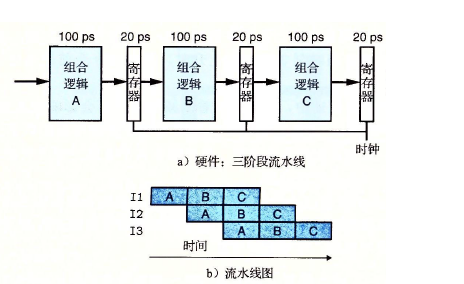

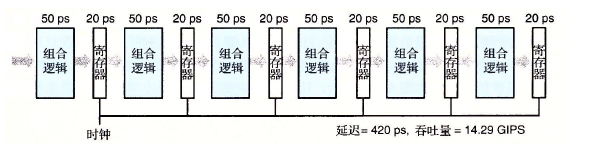

或者我们可以将负责各个动作的电路间用寄存器隔离开来,一个时钟周期内只执行一个动作而不是一条指令,这样可以大大加快电路的整体效率。事实上流水线便是这样做的,为了更高的效率,许多流水线的层级非常深,一个取指/译码/执行三个动作可能被拆分成十五个甚至更多个动作。这样一个时钟周期内,就可以处理多条指令(当然它们处于不同的动作阶段)。

典型的流水线简图如下:

我们用寄存器将负责每一个动作的模块隔离开来,然后将时钟周期设为每个模块刚好可以向本模块寄存器写入数据的时间(而不是信号从头传播到尾的时间)。这样一个时钟周期内,每个模块都执行一次完整的动作。在单个时钟周期内,每个模块在服务不同的指令,而不是所有模块服务同一个指令(如果这样则每个模块只在高电平持续时间的一小块时间内工作)。在单位时间内,整个逻辑电路服务的指令总数大大增加,也就是吞吐量得到了增加。

因为增加了电路的复杂性,对于一条指令而言,从头走到尾所需的时间变长了,但对整个电路而言,吞吐量增加了。这便是流水线机制的意义。

我们在试图理解流水线的动作时,不要将关注点放在逻辑电路上,而要将关注点放在寄存器值的变化上。因为组合逻辑电路不受时钟信号影响,仅负责信号的传播,真正依赖时钟信号的是寄存器的写入行为。我们的目标便是寄存器的值随着时钟周期发生正确的变化。当组合逻辑A前的输入(也就是PC寄存器值)发生变化后,每过一个时钟周期,该变化便依次传递到后面模块的寄存器中。

流水线听起来很完美,但也存在一些缺陷。比如我们很难将各个模块的延迟变为一致的,整个电路的速度将受限于最慢的模块。时钟周期必须大于最慢模块的整体计算时间,这就给其它模块带来了延迟。另外,流水线的层级也并非是越深越好。随着流水线层架的加深,寄存器的增多将导致整体电路延迟的增加,当层级到达一定深度时,该延迟占用总计算时间的比例增大,造成收益的减小。

指令如流水一样进入处理器,而不是一条指令执行完成后下一条指令才进入处理器。虽然将指令的执行拆分成多个小动作会带来许多麻烦,比如流水线冒险,但其带来的吞吐量及缩短时钟周期的收益是值得我们花费精力来解决这些麻烦的。

一个最基本的处理器的实现需要组合逻辑电路和两种存储设备:时钟寄存器(程序计数器和指令状态寄存器)和随机访问存储器(指令内存/数据内存和寄存器文件)。

组合逻辑不需要任何时序或控制,只要输入变化了,值就通过逻辑门网络传播。

那么我们还有四个硬件需要用时序控制:程序计数器/指令状态寄存器/数据内存和寄存器文件。因为时序控制的都是写入操作,而指令内存不需要写入操作,所以也不需要时序控制。

时钟脉冲控制着上述四个元器件的写入操作。时钟信号触发将值写入到指令状态寄存器和随机访问存储器。

处理器真的是一个非常宏大的话题,笔者能力极其有限,只能尽量的从非常宏观的角度上描述一下对处理器的认识(依然很吃力)。

混乱的战场上,两个士兵在黑暗的建筑里遇到。 不知道对方是否自己人,只能祈祷对方别冲动。 但如果听到了枪声,就已经没有了选择的余地。

编辑:hfy

-

寄存器

+关注

关注

31文章

5377浏览量

121394 -

计数器

+关注

关注

32文章

2276浏览量

95106 -

时序电路

+关注

关注

1文章

114浏览量

21751 -

多路复用器

+关注

关注

9文章

880浏览量

65381 -

控制信号

+关注

关注

0文章

169浏览量

12053

发布评论请先 登录

相关推荐

电路中的控制信号实现方案 时序电路如何组成处理器

电路中的控制信号实现方案 时序电路如何组成处理器

评论