引言

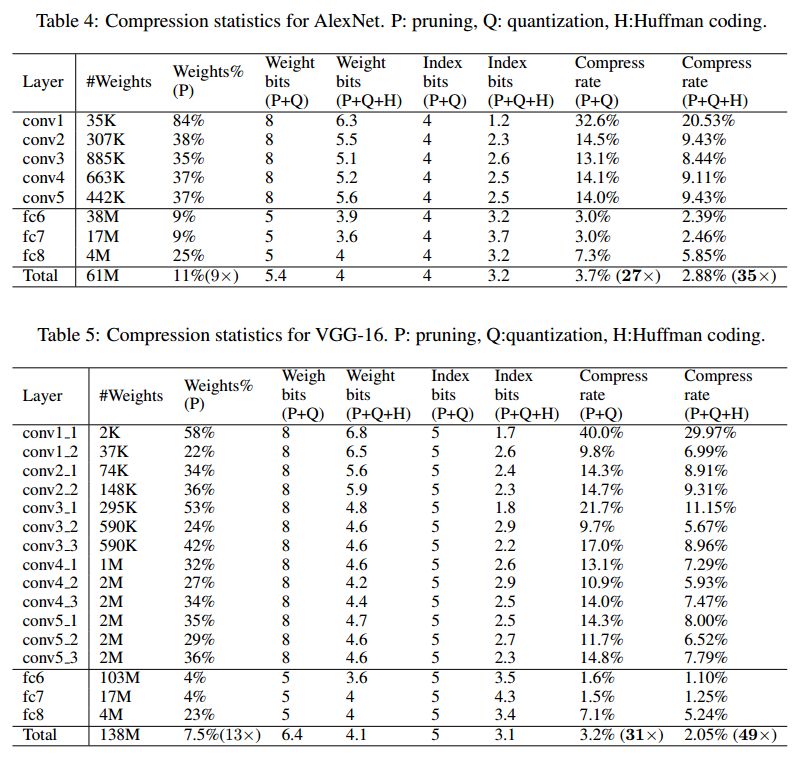

这篇论文来自文章也帮助深鉴科技在国内外获得了一定知名度。深度压缩首先通过剪枝减少了网络的连接,然后通过比特量化来降低权重量,最后通过无损压缩方式霍夫曼编码来缩小存储空间。作者分别对AlexNet和VGG-16进行了实验,获得了35倍和49倍的压缩量,而且精度几乎没有损失。

1. 原理

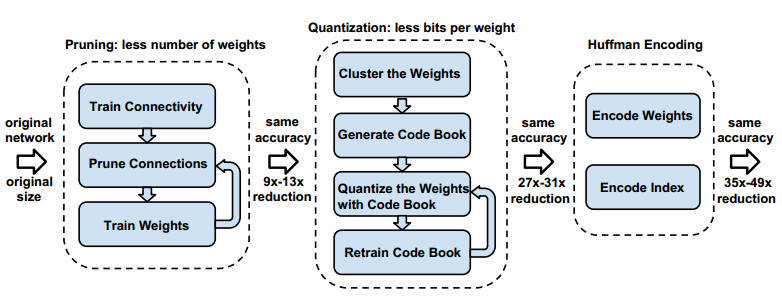

深度压缩之所以获得成功主要是结合了三种压缩方法:剪枝,量化和无损压缩霍夫曼编码,而且在大的数据集和深度神经网络中获得了较高压缩比以及精度未降。前两种方法不仅仅降低了权重数量,也提高了计算速率。而霍夫曼编码只是能够降低存储空间,在实际计算的时候还需要进行解码操作,实际上不会提高计算率。

以上三种方法用图来表示为三个过程:

这三个方法一次顺序进行,每个过程都单独进行。

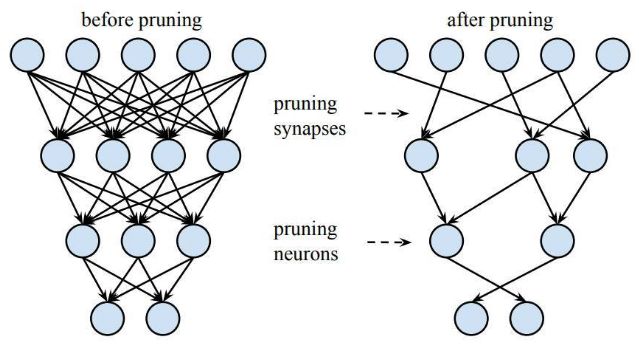

2. 剪枝

首先进行剪枝操作,也是很传统的方法,就是通过一定策略来过滤掉一些不重要的神经网络连接。然后再重新训练进行参数微调,不断重复这个过程直到不能够再进行剪枝为止。剪枝后的神经网络连接大大减少,剩下的都是对网络分类有最重要贡献的连接。其他被剪掉的连接的参数很小,产生的数值对结果影响可以通过重新训练来微调其他参数而弥补。在imageNet数据集上,剪枝方法可以将AlexNet的参数数量减少9倍而没有精度上的损失。VGG-16同样有类似的现象,参数总量可以减少13倍左右而没有精度损失。

3. 量化

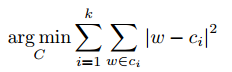

接下来在剪枝网络上做进一步量化操作。基本思路是权重共享和聚类。假设给定了k个类,这是权重参数量化后可能产生的k个值,然后对权重执行聚类操作,聚类方法选择了k-means方式。然后会得到k个区间,这些权重参数都分布在这k个区间中。然后用对应k个区间的数值来替代原来的权重数据。K个数值通常需要log2(k)比特来表示。这样就从原来的32bit降低到了log2(k)。

以下为k-means方法的目标函数:

作者在同一层网络上进行权重共享,不同层之间的权重分别进行聚类。为什么不同层之间的权重不能够进行共享?可以这样想,权重之所以可以共享和量化,是因为其表达的信息有一些共性,从数学上看同一层权重之间是以“求和”方式连接的,而不同层时间是“相乘”关系,后者有一定顺序性,无法做到共享。否则会导致较高错误率,而且层与层之间还有激活函数,归一化函数,不能简单的进行共享。

训练也进行了量化,在原来权重求得梯度值基础上进行同样的聚类和量化操作,然后对量化的权重进行微调得到新的值。过程如下图所示。这里作者并不是用未量化的梯度来更新权重,用量化的梯度来更新可以减少训练迭代,在这里只进行了两次训练,第一次先训练出初始权重数据,第二次是用量化的梯度更新权重。

4. 霍夫曼编码

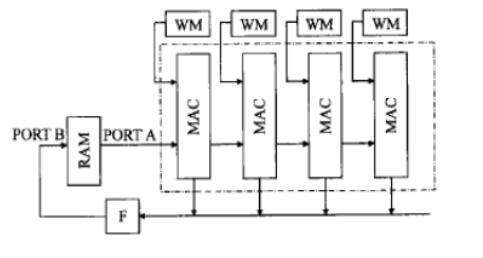

神经网络在FPGA上部署通常需要大量的缓存,为了降低缓存空间,霍夫曼编码进一步来压缩权重。霍夫曼编码是一种无损编码,其通过数据的重复率来进行数据重新编码,重复率高的用少的比特,重复率少的用多的比特,这样就降低了数据存储空间。虽然霍夫曼编码能压缩2到3倍权重,但是并不适合在FPGA上实现。因为霍夫曼解码要消耗大量资源,同时霍夫曼解码是单bit进行解析,速度较慢。这些都不利于FPGA上加速深度神经网络。

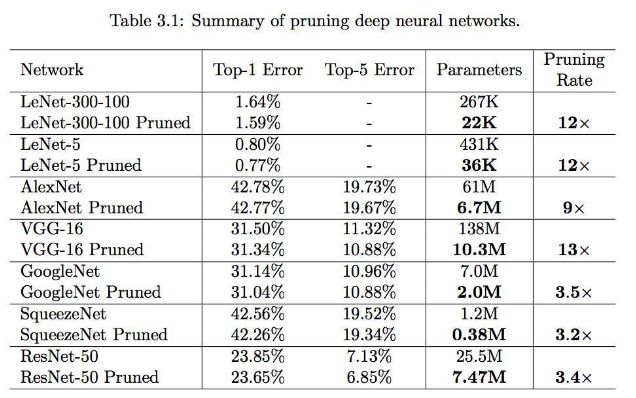

5. 实验结果

作者主要在AlexNet和VGG-16上进行了尝试,结果如图:

从结果中可以获得以下结论:

1) 全连接层的剪枝和量化都很大,说明全连接层信息有很大冗余;

2) 越深的网络压缩比例越大;

结论

本文介绍了深度压缩方法,其结合了剪枝,量化和霍夫曼编码的方式来最大限度降低权重数据量,这种方法促进了深度神经网络在FPGA器件上的应用能力。

编辑:hfy

-

FPGA

+关注

关注

1629文章

21729浏览量

602984 -

神经网络

+关注

关注

42文章

4771浏览量

100712

发布评论请先 登录

相关推荐

如何设计BP神经网络图像压缩算法?

深度神经网络是什么

基于深度神经网络的激光雷达物体识别系统

卷积神经网络模型发展及应用

深度神经网络的压缩和正则化剖析

深度神经网络模型的压缩和优化综述

神经网络在FPGA上的应用:深度压缩方法

神经网络在FPGA上的应用:深度压缩方法

评论