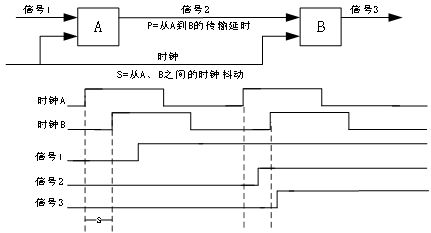

设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期 T,则当信号在一个触发器上改变后,在下一个逻辑级上将不会改变,直到两个时钟周期以后才改变,如图所示。

图1

02、FPGA所使用的时钟必须具有低抖动特性

传输时间为信号在第一个触发器输出处所需的保持时间加上两级之间的任何组合逻辑的延迟,再加两级之间的布线延迟以及信号进入第二级触发器的设置时间。无论时钟速率为多少,每一个 FPGA 设计所用的时钟必须具有低抖动特性。抖动 S 是触发器的一个时钟输入到另一个触发器的时钟输入之间的最大延迟。为使电路正常工作,抖动必须小于两个触发器之间的传输时间。

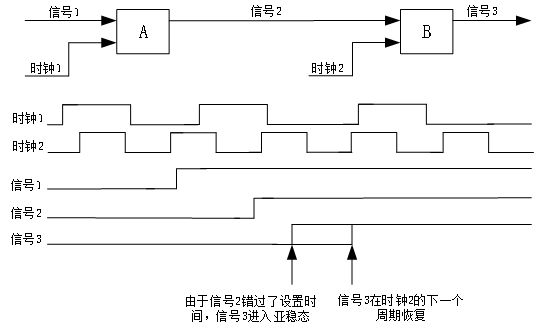

图 2 显示了如果抖动大于传输时间(S>P)将出现的情况,该电路用时钟的两个上升沿来延 迟信号 1。然而,信号 1 上的一个改变会在相同的时钟周期上传输到的信号 3 上,从而引起信号 2 的改变。因为 S > P,电路将不能不正常。

图2

注意事项

须注意的是,时钟速率与传输延时并没有什么关系,甚至普通的 100bps 时钟也会出现抖动问题。这意味着虽然 FPGA 供应商宣称他们的芯片具有较短的传输时间和很高的时钟速率,但抖动问题可能会严重,甚至那些没有运行在最高速率上的设计也是如此。

好在 FPGA 供应商已经认识到时钟抖动的影响,并在他们的芯片中提供低抖动的布线资源。这些特殊的布线能够在芯片中一个给定范围内的任何两个触发器之间提供一个确定的最大抖动。部分产品的低抖动资源覆盖了整个芯片,而其它的则可能只覆盖了 FPGA 逻辑块中的一个特定的行或列。对于一个需要很多不同时钟源的设计,这些低抖动 FPGA 是比较理想的选择。

03、多时钟设计中使用异步时钟将两级逻辑结合

多时钟设计的最严重问题之一是用异步时钟将两级逻辑结合在一起。由于异步时钟会产生亚稳态,从而严重降低设计性能,或完全破坏设计所能实现的功能。在触发器的时序要求产生冲突时(设置时间和保持时间)将产生亚稳态,触发器的最终输出是未知的,并使整个设计处于不确定状态。如果有一级逻辑要将数据异步地发送到另一级,图 3 所示的情形将不能满足触发器的设置和保持时间要求。确切地说,如果设计中含有异步逻辑将有可能会产生亚稳态。在处置异步资源时必需非常小心,因为这可能产生一些很严重的问题。

图3

在用异步时钟产生任何逻辑前应该尽量先考虑采用其它替代方法,用异步时钟的组合逻辑是产生亚稳态问题的主要原因。同样,当违反触发器的设置和保持时间约束时,在一个短时间内输出将具有不确定性,并且将最终设定在“1”或“0”上,确切的状态不可预知。

幸好在面对亚稳态时,已经有了一些解决方案。比如双寄存器方法:进入第一级触发器的数据与时钟异步,所以第一级触发器几乎肯定是亚稳态;然而,只要亚稳态的长度小于时钟的周期,第二级触发器就不会进入亚稳态。但是,FPGA 供应商很少提供亚稳态时间,尽管该时间一般小于触发器的设置和保持时间之和。

编辑:hfy-

FPGA

+关注

关注

1664文章

22504浏览量

639306 -

寄存器

+关注

关注

31文章

5620浏览量

130428

发布评论请先 登录

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

浅谈FPGA的时钟输入要求

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

Texas Instruments PLL1705/PLL1706:3.3-V 双 PLL 多时钟发生器的卓越之选

德州仪器PLL1707与PLL1708:低抖动多时钟发生器的卓越之选

Texas Instruments PLL1707和PLL1708:低抖动多时钟发生器的卓越之选

探索LMH1982多速率视频时钟发生器:特性、应用与设计要点

探索PLL1707 - Q1:低功耗、高性能的多时钟发生器

德州仪器PLL1705/PLL1706:低抖动多时钟发生器的卓越之选

探究PLL1705与PLL1706:3.3V双PLL多时钟发生器的卓越性能

德州仪器PLL1707和PLL1708:低抖动多时钟发生器的卓越之选

德州仪器PLL1707和PLL1708:低抖动多时钟发生器的卓越之选

深入解析PLL1707-Q1:高性能多时钟发生器的理想选择

PLL1708双PLL多时钟发生器技术文档总结

FPGA中时钟速率和多时钟设计案例分析

FPGA中时钟速率和多时钟设计案例分析

评论