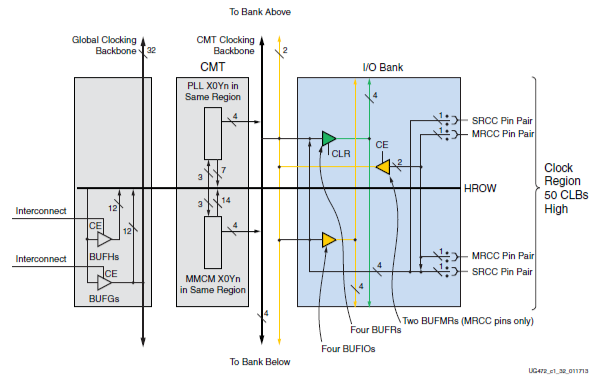

slice与全局时钟在一起就可以实现任意的组合逻辑和时序逻辑功能,但很多时候咱们还需要将FPGA内部的数据暂时存储,用作它用。Slice作为FPGA最基本的单元,也是能够完成数据存储的功能,但显然有些大材小用,因此xilinx公司在其FPGA内部专门集成了很多存储器模块,称作Block RAM,其犹如slice海洋当中的一颗颗明珠,专门实现数据暂存功能,且每个时钟区域都布置了若干个Block RAM。

今天咱们就聊一聊7系列FPGA里面的Block RAM。

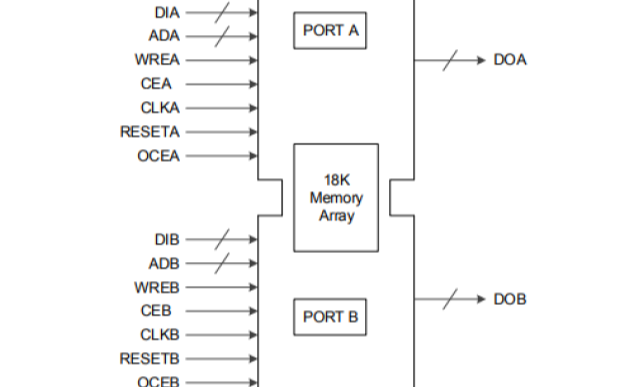

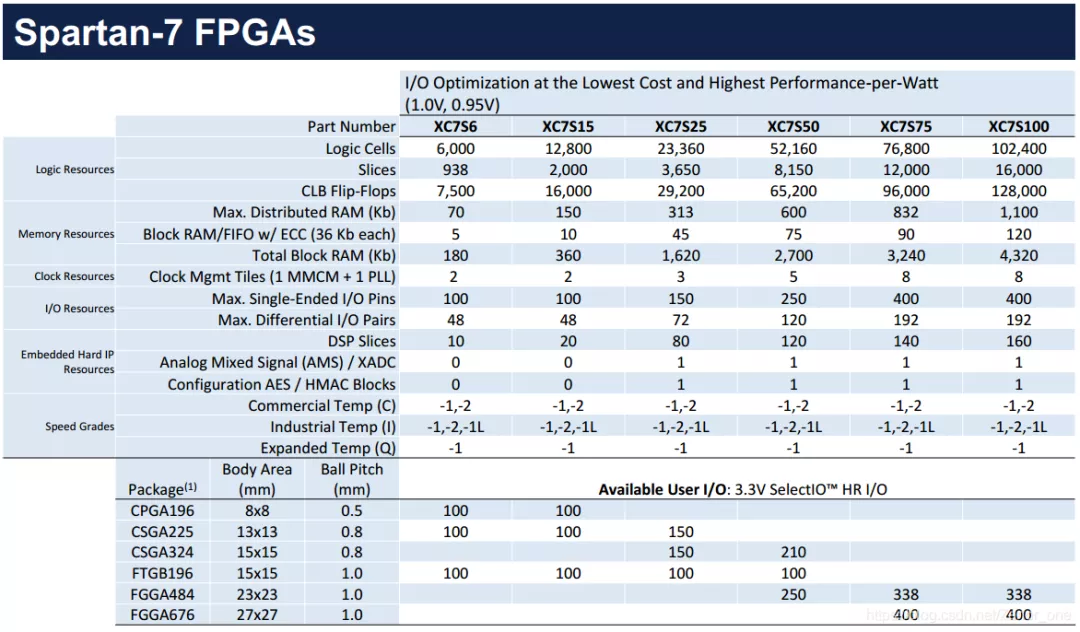

在7系列FPGA里面,每个Block RAM最多可存储36Kb的数据,2个Block RAM可级联实现64kb数据存储,而每个Block RAM又可分成2个18kb的Block RAM,仅此而已,不可再分,亦不可无限级联。

Block RAM在使用的时候都是使用Xilinx CORE Generator来无脑配置,可以配置成RAM、ROM以及运用最广泛的FIFO。RAM可以配置成各种不同的接口模式以及读出模式,FIFO则可配置成同步FIFO和异步FIFO等。所有配置信息咱们都是在FPGA的开发工具Xilinx CORE Generator里面实现。

Block RAM的各种不同配置以及如何在全局时钟下读/写数据RAM和FIFO内容太多,不太好描述,但其实用起来很easy,基本上只用得到以下a几个信号:时钟、复位、时钟使能、读数据、读地址、读使能、写数据、写地址、写使能、数据空信号、数据满信号,以后咱们单独拿出来,用具体例子操作一波!

编辑:hfy

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

存储器

+关注

关注

38文章

7484浏览量

163762 -

Xilinx

+关注

关注

71文章

2167浏览量

121302

发布评论请先 登录

相关推荐

Xilinx 7系列FPGA的时钟结构解析

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx 7系列FPGA管脚是如何定义的?

FPGA从Xilinx 的7系列学起(8)

FPGA的RAM存储资源详细资料说明

Xilinx 7系列与Ultrascale系列FPGA的区别

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

xilinx 7系列FPGA里面的Block RAM

xilinx 7系列FPGA里面的Block RAM

评论