1、综合约束

在“设置”对话框的“约束”部分下,选择“默认约束设置”作为活动约束设置;包含在Xilinx设计约束(XDC)文件中捕获的设计约束的一组文件,可以将其应用于设计中。两种类型的设计约束是:

1) 物理约束:这些约束定义引脚的位置以及单元(例如Block RAM,LUT,触发器和设备配置设置)的绝对或相对位置。

2) 时序约束:这些约束定义了设计的频率要求。由于没有时序限制,Vivado设计套件仅针对线长度和布局拥堵来优化设计。

2、综合策略

1) Defaults(默认设置)

2) RuntimeOptimized

执行较少的时序优化,并消除一些RTL优化以减少综合运行时间。

3) AreaOptimized_high

执行常规面积优化,包括强制执行三进制加法器,在比较器中使用新阈值以使用进位链以及实现面积优化的多路复用器。

4) AreaOptimized_medium

执行常规面积优化,包括更改控制集优化的阈值,强制执行三进制加法器,将推理的乘法器阈值降低到DSP模块,将移位寄存器移入BRAM,在比较器中使用较低阈值以使用进位链,以及进行区域优化的MUX操作。

5) AlternateRoutability

一组提高路由能力的算法(较少使用MUXF和CARRY)。

6) AreaMapLargeShiftRegToBRAM

检测大型移位寄存器,并使用专用的Block RAM实现它们。

7) AreaMultThresholdDSP

专用DSP块推断的下限阈值。

8) FewerCarryChains

较高的操作数大小阈值以使用LUT代替进位链。

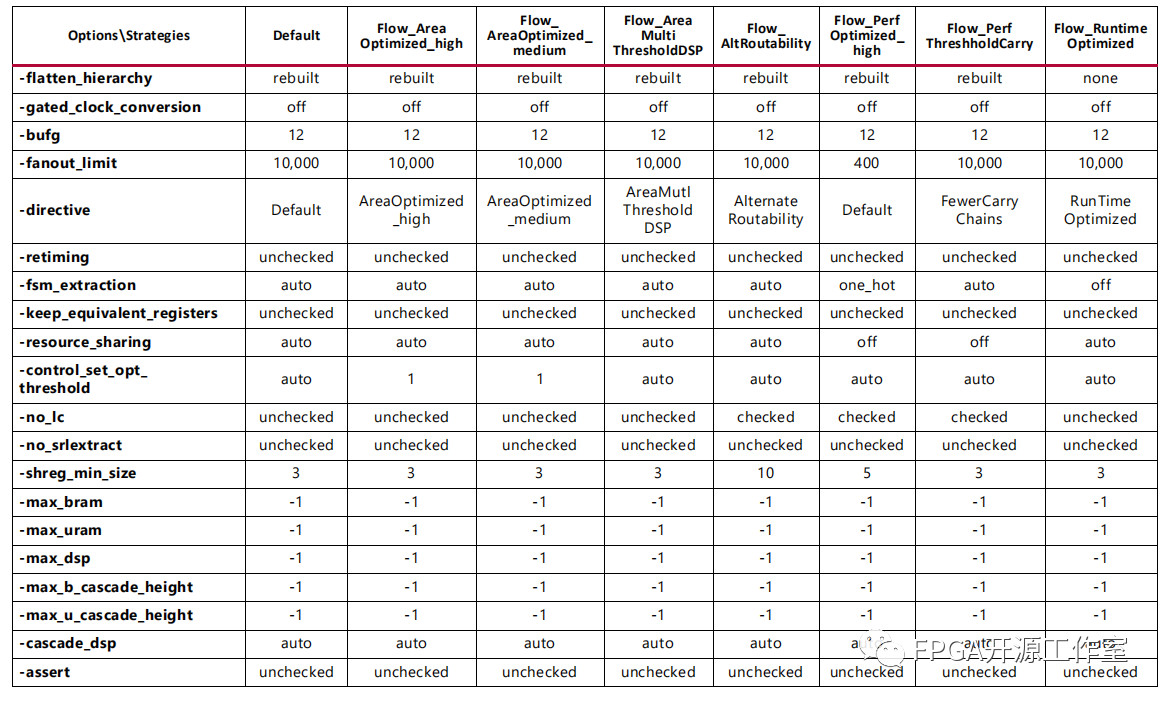

3、其他选项

-flatten_hierarchy:确定Vivado综合如何控制层次结构。

- none:指示综合工具不要展平层次结构。综合的输出与原始RTL具有相同的层次结构。

-full :指示工具完全展平层次结构,仅保留顶层。

-rebuilt:设置后,重新构建允许综合工具展平层次结构,执行综合,然后基于原始RTL重建层次结构。该值使QoR受益于跨边界优化,其最终层次类似于RTL,以便于分析。

-gated_clock_conversion:启用和禁用综合工具转换时钟逻辑的功能。

-bufg: 控制工具在设计中推断出多少BUFG。当设计网表中的其他BUFG对合成过程不可见时,Vivado设计工具将使用此选项。该工具可以推断出指定的数量,并跟踪RTL中实例化的BUFG数量。例如,如果-bufg选项设置为12,并且在RTL中实例化了三个BUFG,则Vivado综合工具最多可以推断出另外九个BUFG。

-fanout_limit:指定信号在开始复制逻辑之前必须驱动的负载数。此全局限制是一般指南,当工具确定有必要时,可以忽略该选项。

-retiming :布尔选项

-fsm_extraction : 控制综合如何提取和映射有限状态机。 FSM_ENCODING更详细地描述了这些选项。

FSM_ENCODING可以放在状态机寄存器上。合法的值是“ one_hot”,“ sequential”,“johnson”,“ gray”,“ auto”和“ none”。“ auto”值是默认值,并允许该工具确定最佳编码。可以在RTL或XDC中设置此属性。

-keep_equivalent_registers :防止合并具有相同输入逻辑的寄存器。

-resource_sharing:设置不同信号之间的算术运算符共享。这些值是自动的,打开的和关闭的。自动值集执行资源共享以取决于设计时间。

-control_set_opt_threshold: 将时钟使能优化的阈值设置为较少的控制集。默认值为自动,这意味着该工具将根据目标设备选择一个值。支持任何正整数值。

给定值是工具将控制集移入寄存器的D逻辑所需的扇出数量。如果扇出大于该值,则该工具尝试使该信号驱动该寄存器上的control_set_pin。

-no_lc:选中后,此选项将关闭LUT合并。

-no_srlextract:选中后,此选项将关闭完整设计的SRL提取,以便将其实现为简单寄存器。

-shreg_min_size:推断SRL的阈值。默认设置为3。这将设置顺序元素的数量,这些元素将导致推断固定延迟链的SRL(静态SRL)。策略也将此设置定义为5和10。

-max_bram:描述设计中允许的最大块RAM数量。通常在设计中有黑匣子或第三方网表时使用此选项,并允许设计人员为这些网表节省空间。

-max_uram:设置设计中允许的最大UltraRAM(UltraScale+™设备块RAM)块。默认设置为-1表示该工具选择指定零件允许的最大数量。

-max_dsp:描述设计中允许的最大块DSP数量。通常在设计中有黑匣子或第三方网表时使用,并为这些网表留出空间。默认设置为-1表示该工具选择指定零件允许的最大数量。

-max_bram_cascade_height:控制该工具可以级联的BRAM的最大数量。默认设置为-1表示该工具选择指定零件允许的最大数量。

-max_uram_cascade_height:控制该工具可以级联的UltraScale+设备UltraRAM块的最大数量。默认设置为-1表示该工具选择指定零件允许的最大数量。

-cascade_dsp: 控制如何实现总和DSP模块输出中的加法器。默认情况下,使用块内置加法器链计算DSP输出的总和。价值树迫使总和在结构中实现。值是:auto,tree和force。默认为自动。

-no_timing_driven: (可选)禁用默认的时序驱动综合算法。这导致减少了综合运行时间,但忽略了时序对综合的影响。

-sfcu:在单文件编译单元模式下运行综合。

-assert: 启用要评估的VHDL断言语句。故障或错误的严重性级别会停止综合流程并产生错误。警告的严重性级别会生成警告。

tcl.pre和tcl.post选项是在合成之前和之后立即运行的Tcl文件的挂钩。

4、Tcl Commands to Get Property

get_property DIRECTORY [current_project] get_property DIRECTORY [current_run]

编辑:hfy

-

FPGA

+关注

关注

1664文章

22545浏览量

640420 -

Xilinx

+关注

关注

73文章

2208浏览量

132136 -

Vivado

+关注

关注

19文章

860浏览量

71484

发布评论请先 登录

基于Vivado的AD9680 FPGA芯片测试

Vivado时序约束中invert参数的作用和应用场景

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

Xilinx FPGA串行通信协议介绍

Windows环境下用Vivado调试E203

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

win10环境下使用vivado生成.bit与.mcs文件

时序约束问题的解决办法

关于综合保持时间约束不满足的问题

FPGA开发板vivado综合、下载程序问题汇总

Vivado无法选中开发板的常见原因及解决方法

Xilinx FPGA案例学习之Vivado设计综合约束

Xilinx FPGA案例学习之Vivado设计综合约束

评论