在fpga工程中加入时序约束的目的:

1、给quartusii 提出时序要求;

2、quartusii 在布局布线时会尽量优先去满足给出的时序要求;

3、STA静态时序分析工具根据你提出的约束去判断时序是否满足的标准。

举个形象的比喻:就好比我要让代工厂(类比quartus ii)给我加工一批零件,要求长宽高为10x10x10cm,误差不超过1mm(类比时序约束条件)。代工厂按要求(即约束条件)开始进行生产加工,工厂为了不返工,肯定会尽量生产出达到我要求的零件。当加工完成后,质检员(类比STA静态时序分析工具)按我给出的要求进行检验看是否满足要求。要是工厂想尽了各种办法也不能达到我给出的要求,那么就是我给出的要求太高了(即时序约束中的过约束),要是我给出的要求太低(比如说加工成方形就行,而没有指出长宽高),那么工厂很容易就生产出来了,但这并不是我想要的,这是由于我给出的约束太松 即相当于时序里的 欠约束。

quartus ii里的静态时序分析(STA):是套用特定的时序模型,针对特定电路分析其是否违反设计者给定的时序限制。说白了就是检查fpga内部所有寄存器的建立时间保持时间是否满足spec给定的要求。

1、Data Arrival Time 数据到达目的寄存器REG2时间

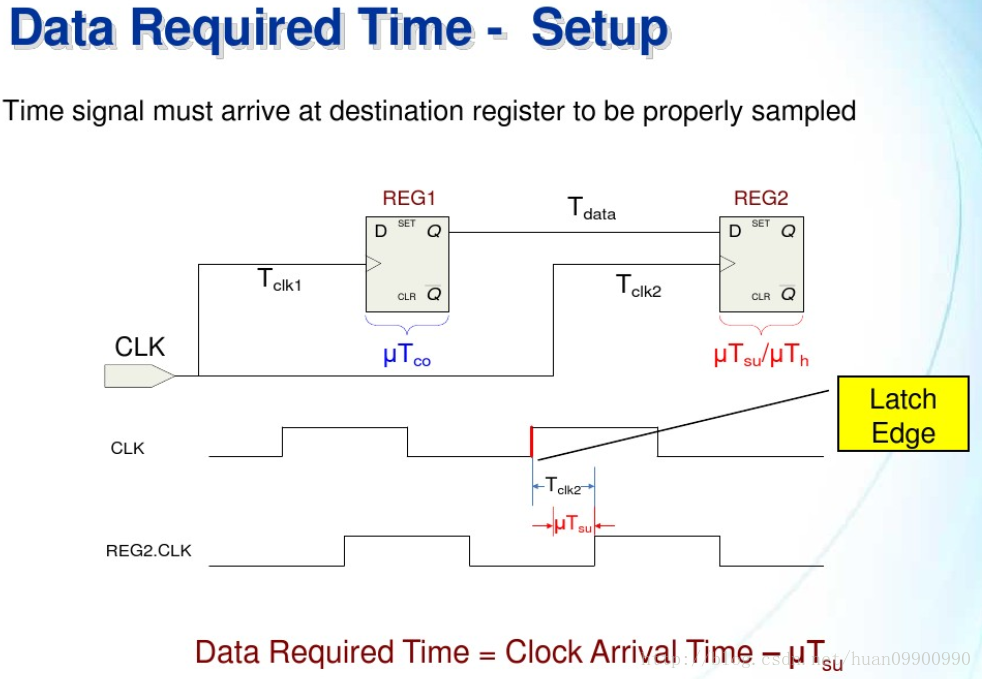

3、Data Required Time 数据需求时间-Setup

指数据需要在需求时间前到达目的寄存器,否则不满足建立时间关系,不能被正确采样。

最大延迟是防止数据来的太慢 ,当时钟沿已经到来时,数据还没到,这样就不能在上升沿被寄存器正确采样。

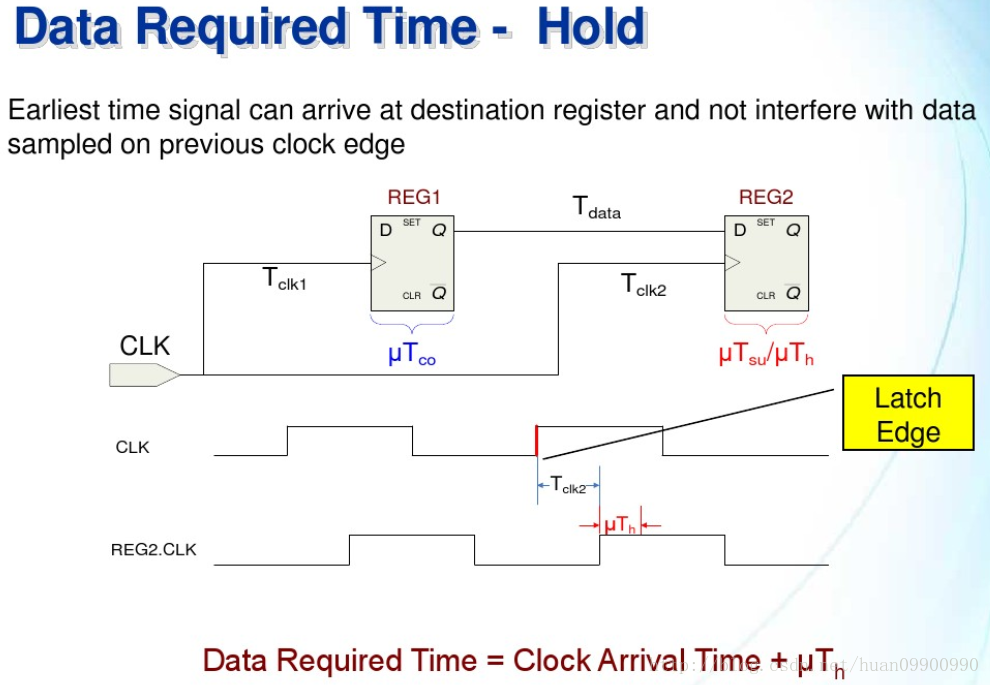

4、Data Required Time 数据需求时间-Hold

指数据在时钟锁存沿到达后,必须保持一段稳定的时间,使数据被正确采样。做最小延迟约束是为了防止数据传输过快,使得寄存器还在锁存上一个数据时,下一个数据就来了,使得上次锁存数据发生错误。

所以 保持时间必须小于 tco+tlogic(组合逻辑延时),这里 tco+tlogic(组合逻辑延时)就是数据从源寄存器到目的寄存器的时间。

5、时序裕量slack

Setup Slack=Setup Required Time - Data Arrival Time

Hold Slack=Data Arrival Time - Hold Required Time

时序裕量为正 表示时序满足时序约束条件,为负,时序不满足。

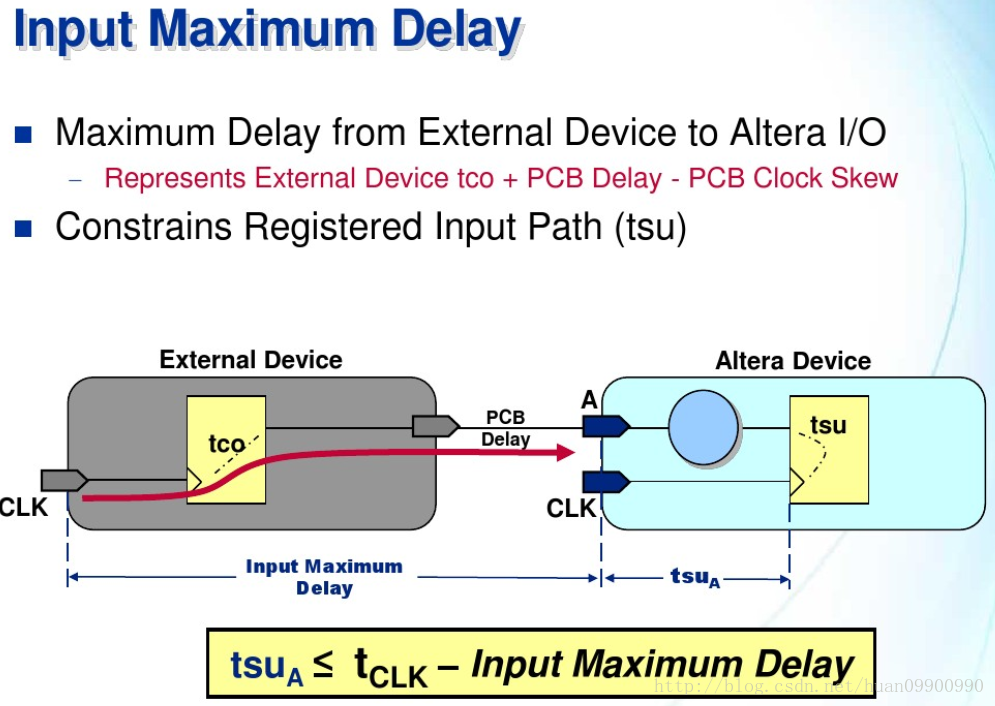

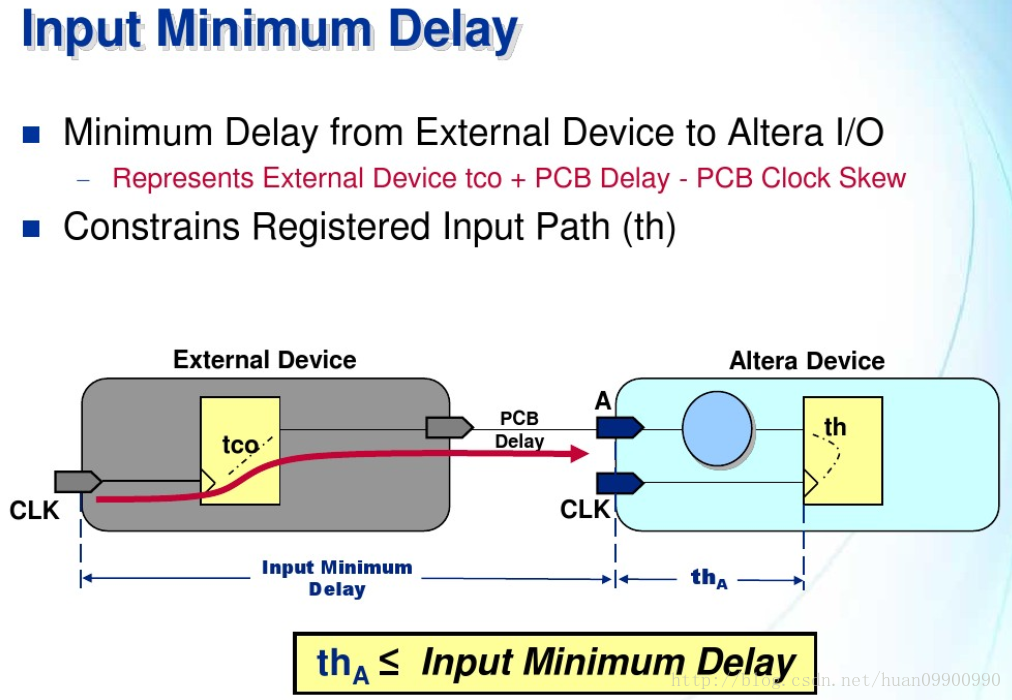

6、Input Delay 输入最大最小延迟

Input Delay=数据路径延迟-时钟路径延迟+utco(外部器件)

输入延迟 Input Delay=Data Arrival Time-Clock Arrival Time

=launch Edge+Tclk1+uTco+Tdata-latch edge-Tclk2

数据相对于时钟到达目的寄存器的时间差值。即数据和时钟从同一时间点(launch)开始,到达目的寄存REG2的时间差。

数据到达REG2走的路径延时是:时钟从launch开始 经过Tclk1的延迟到达REG1,REG1在时钟沿来之后,经过Tco的时间把数据送出REG1,然后数据再经过路径延迟Tdata 到达REG2的数据管脚。

时钟到达REG2走的路径延时是:时钟也从同一时间点(launch)开始,经过路径延迟Tclk2就到达REG2的时钟管脚。

输入最大延迟是约束为了满足寄存器的建立时间,输入最小延迟是位了满足寄存器的保持时间。

Input Maximum Delay=Data Arrival Time最大值-Clock Arrival Time 最小值

“fpga-centric”Input Maximum Delay<=tclk-tsu(fpga)

Input Minimum Delay=Data Arrival Time最小值-Clock Arrival Time 最大值

“fpga-centric” Input Minimum Delay>=th(fpga)

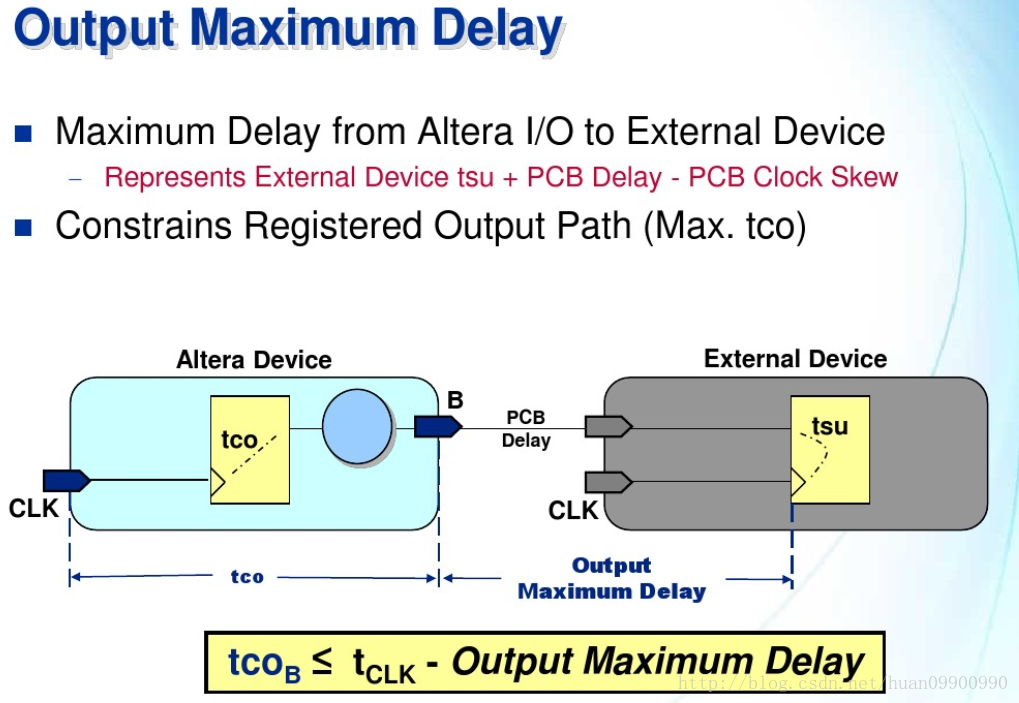

7、output Delay 输出最大最小延迟

output Maximum Delay=外部器件tsu+数据路径最大延迟-时钟路径最小延迟

output Minimum Delay=外部器件th+数据路径最小延迟-时钟路径最大延迟

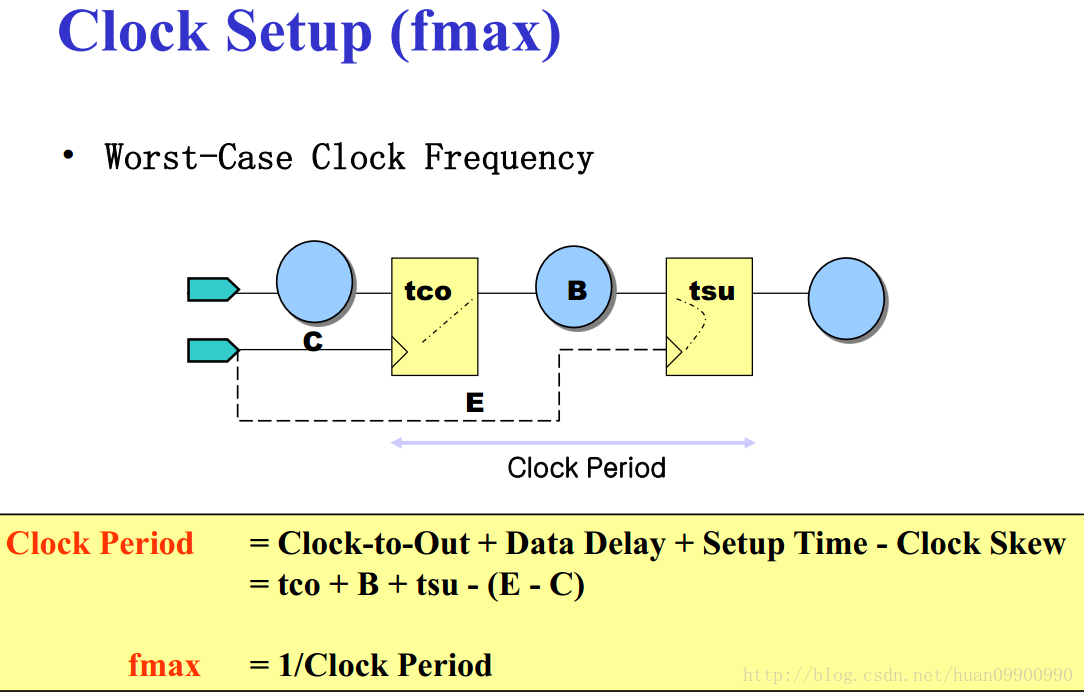

8、Fmax

指设计能运行的最高频率,即周期为最小时,频率最大

当Setup Slack=0时,系统刚好满足建立时间,此时周期为最小值。

period=tco+data_delay+tsu-tskew

编辑:hfy

-

FPGA

+关注

关注

1629文章

21735浏览量

603122 -

寄存器

+关注

关注

31文章

5342浏览量

120285

发布评论请先 登录

相关推荐

FPGA驱动AD芯片之实现与芯片通信

使用modelsim时的问题分析

时序逻辑电路故障分析

FPGA如何估算分析功耗

FPGA 高级设计:时序分析和收敛

Xilinx FPGA编程技巧之常用时序约束详解

FPGA工程的时序约束实践案例

Xilinx FPGA编程技巧之常用时序约束详解

fpga仿真文件怎么写

浅析FPGA的调试-内嵌逻辑分析仪(SignalTap)原理及实例

FPGA quartus ii里的静态时序分析

FPGA quartus ii里的静态时序分析

评论