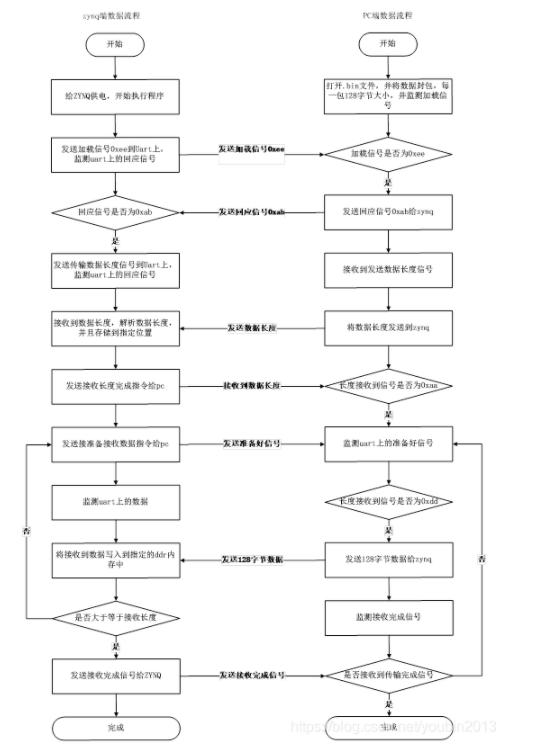

话不多说,进入今天的主题:生成zynq裸核启动文件。

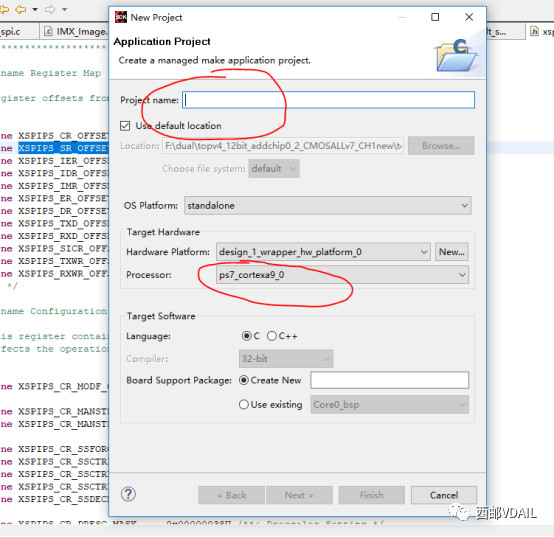

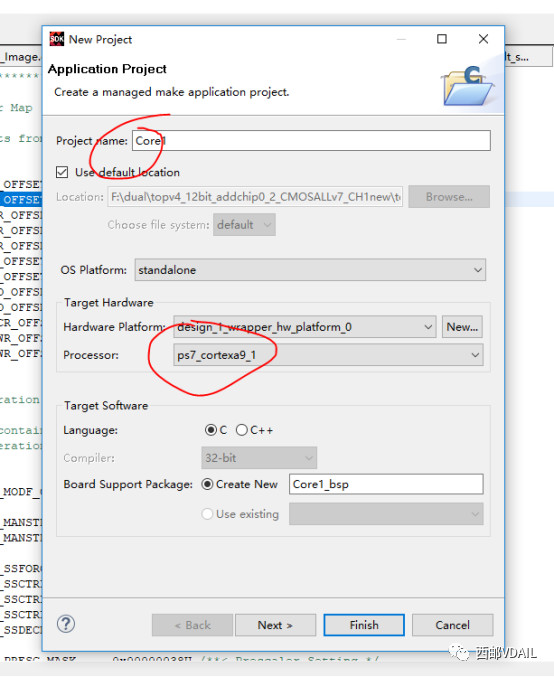

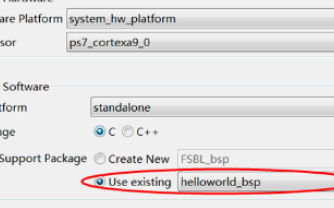

注意:如上图所示,

Core0 工程建立时选择ps7_cortexa9_0,

Core1 工程建立时选择ps7_cortexa9_1

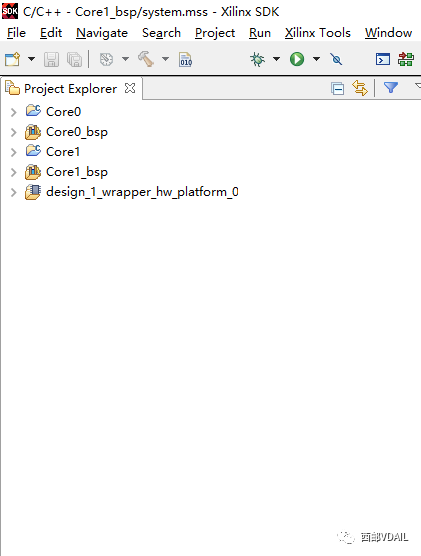

完成后如下图所示:

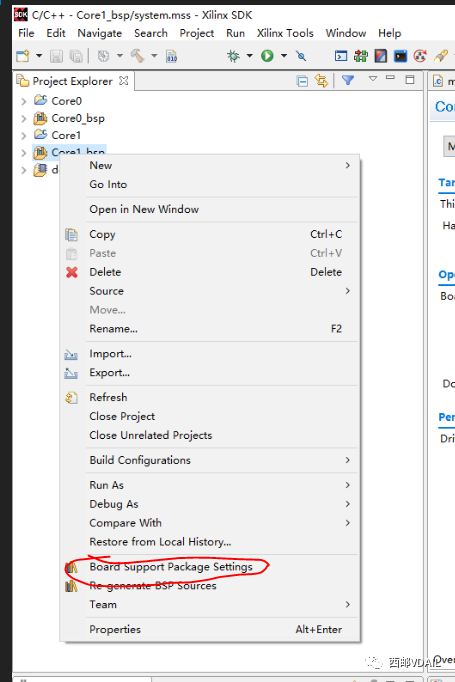

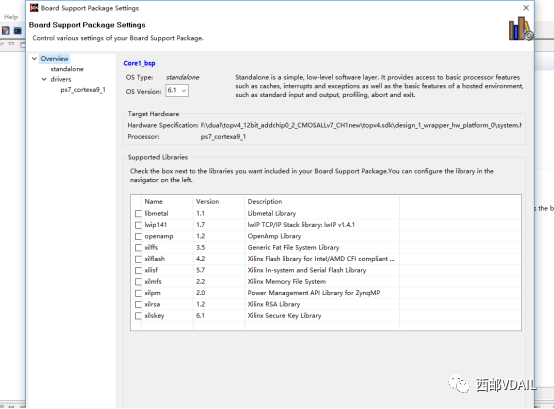

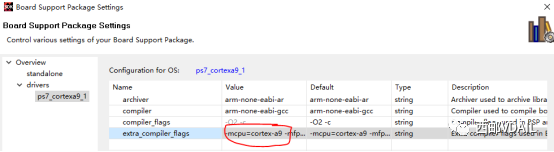

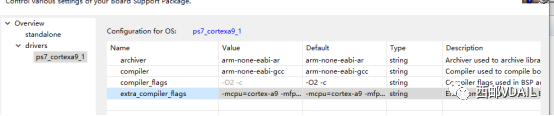

2. 配置Core1即从核中的BSP文件

在下图中画圈处,配置:-DUSE_AMP=1

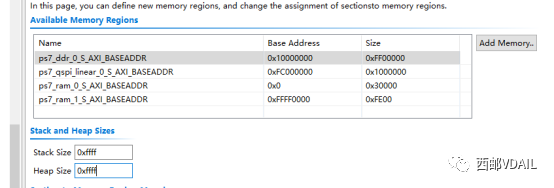

3. 配置Core0和Core1的DDR空间分配

通过修改lscript.ld文件中的内容,可以改变在存储器中的执行位置, 因为ELF文件是加载到DDR中执行的,所以两个DDR地址不能重合

Core0的配置 :画圈处栈空间也要分配,防止溢出

Core1配置

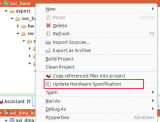

4. 建立FSBL文件,并配置main()文件

配置main() 跟第三步中的DDR空间配置有关

在FSBL的src中找到main.c文件打开,在里面添加下面一段代码,用于启动CPU1:

#define sev() __asm__("sev")

#define CPU1STARTADR 0xFFFFFFF0 //Core1 DDR配置中的SIZE大小

#define CPU1STARTMEM 0x10000000 //Core1 DDR配置中的起始地址

void StartCpu1(void)

{

#if 1

Xil_Out32(CPU1STARTADR, CPU1STARTMEM);

dmb(); //waits until write has finished

sev();

#endif

}

将上面的代码在main()中添加到:Load boot image的位置,将CPU1的启动函数,放置于此位置,改动后的代码段如下:

5. 生成mcs文件和烧写mcs文件到QSPI Flash

单击‘Core1’,选择Xilinx Tools –> Create zynq boot image,选择Add,选择文件…/ Core1/Debug/ Core1.elf,点击打开。然后选择Core1.elf, Core0.elf在Core1.elf上面。然后在Output pach后面把boot.bin修改为Boot.mcs。然后点击 Create Image

选择文件生成存储地址

选择MCS

画圈处是添加的文件

顺序为:FSBL.elf .bit文件 Core0.elf Core1.elf

点击Create Image 生成.mcs文件

6. 完成操作将.MCS文件烧写进板子里

bin文件用来烧写到SD卡,mcs文件用来烧写到QSPI flash中

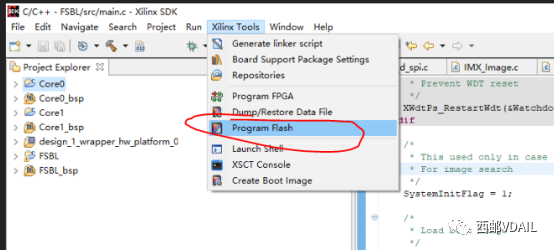

选择Xilinx Tools –> Program Flash,在Image File后面选择刚才生成的Boot.mcs文件,Offset为0x0,Flash Type为qsip_single。勾选Blank check after erase和Verify after flash。检查开发板上电和连线状况,然后点击Program

编辑:hfy

-

存储器

+关注

关注

38文章

7507浏览量

163963 -

DDR

+关注

关注

11文章

712浏览量

65380 -

Vivado

+关注

关注

19文章

812浏览量

66637

发布评论请先 登录

相关推荐

关于zynq启动的问题,求达人解答!

玩转Zynq连载29——[ex51] 制作裸跑程序的启动文件BOOT.bin

Zynq在非JTAG模式下的启动配置流程

ZYNQ-7000如何生成从Flash和SD卡启动的镜像文件

生成zynq裸核启动文件步骤解析

生成zynq裸核启动文件步骤解析

评论