电机驱动Motor drive 是组装在胶片式照相机内的微型电机或弹簧及其附件的总称,借助微型电机自动地卷取胶片,大多是指 35 毫米单镜头反光相机所用的。

01 供电电路原理

供电部分原理图如图 1-1 所示:

图 1-1

从图 1-1 中可知道供电有+5V、+3.3V、+1.5V 三种,其中每个电源均有 0.1µF 的旁路电容,将电源中的高频串扰旁路到地,防止高频信号通过电源串扰到其它模块中。同时还能将电源本身的工频干扰滤除。

值得注意的是:在布线的时候,经退藕电容退藕后的电源输出点应该尽量紧靠芯片的电源引脚进行供电,过长的引线有可能重新变成干扰接收天线,导致退藕效果消失。如果无法让每个退藕后的电源输出点均紧靠芯片的电源引脚,那么可以采用分别退藕的方法,即分别尽量紧靠每个芯片的电源引脚点接入退藕电容进行退藕,这也解释了为什么图 1-1 的 3.3V 电源有两个退藕输出点。

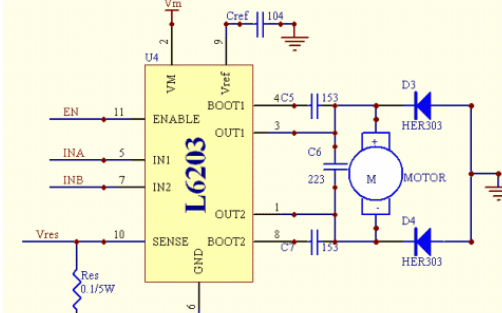

02、电机驱动电路原理

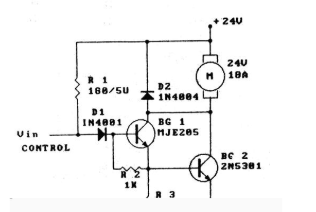

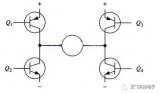

电机驱动电路原理如图 2-1 所示:

图 2-1

图 2-1 中 Header 4X2 为 4 排 2 列插针,FM0~3 为FPGA芯片 I/O 输出口,加入的插针给予一个可动的机制,在需要使用时才用跳线帽进行相连,提高 I/O 口的使用效率。RES5 是五端口排阻,内部集成了 4 个等阻值且一端公共连接的电阻,PIN 1 是公共端,PIN2~5 为排阻的输出端,排阻原理图如图 2-2 所示:

图 2-2

该排阻公共端接电源,即上拉电阻形式,作用是增强FPGA芯片 I/O 口(以下简称 I/O 口)的驱动能力,实际上就是增加 I/O 输出高电平时输出电流的大小。当 I/O 输出高电平时,+5V 电源经排阻与 IN1~4 相连,相当于为 I/O 提供一个额外的电流输出源,从而提高驱动能力。当 I/O 输出低电平时,可将 I/O 近似看做接地,而 IN1~4 因与 I/O 由导线直接相连,因此直接接受了 I/O 的低电平输出信号。此时,+5V 电源经排阻 R、I/O 内部电路(电阻近似为零)后接地,因此该路的电流不能大于 I/O 的拉电流(Ii)最大值,有公式 2-1:

由公式 2-2 可以得出排阻的取值范围。

该上拉电阻除了提高驱动能力外,还有一个作用,就是进行电平转换。经查,ULN2003 的接口逻辑为:5V-TTL, 5V-CMOS 逻辑。而在 3.3V 供电的情况下,I/O 口可以提供 3.3V-LVTTL,3.3V-LVCMOS,3.3V-PCI 和 SSTL-3 接口逻辑电平。因此,需要外接 5V 的上拉电阻将 I/O 电平规格变成 5V 电平逻辑。

芯片 ULN2003 内部集成 7 组达林顿管,专门用于提高驱动电流,芯片引脚间逻辑如图 2-3 所示:

图 2-3

图 2-4

由于 I/O 电流远远不足以驱动电机,因此需要外接该芯片驱动电机,ULN2003 内部集成的达林顿管电路如图 2-4 所示。达林顿管的形式具有将弱点信号转化成强电信号的特点,I/O 电平逻辑从 PIN IN 输入,通过达林顿管控制 PIN 9(COMMON)端输入的强电信号按照 I/O 信号规律变化。值得注意的是:ULN2003 输出逻辑将与输入逻辑相反,编程时应该注意该特点。

RES6 是六端口排阻,内部集成了 5 个等阻值且一端公共连接的电阻,PIN 1 是公共端,PIN2~6 为排阻的输出端,原理图与接法说明可参考上述图 2-2,排阻取值范围计算参见公式 2-2,此处不再赘述。值得注意的是:RES6 的 PIN 1 与 PIN 2 相连,是因为多出了一个不使用的电阻,为了避免 PIN 2 悬空,因此将 PIN 2 与 PIN 1(公共端)相连,即 PIN 2 对应的电阻被短路,从而既避免的悬空的引脚,又能使该电阻失效。

03 电机指示灯电路原理

电机指示灯电路如图 3-1 所示:

图 3-1

电机部分指示灯用于指示各路信号的逻辑电平状态,其中 R106~109 为限流电阻,防止发光二极管因电流过大烧毁。值得注意的是:该指示灯的发光二极管接成共阳极,由 M0~3 信号端口产生低电平点亮对应的二极管,而 ULN2003 的 OUT 与 IN 逻辑电平相反,因此对于 I/O 口 FM0~3 来说,输出高电平就能点亮对应的发光二极管,例如:FM0 输出高电平,则对应 LD17 点亮,编程时应注意此电路将 I/O 实际逻辑反相了两次,对应关系为 I/O 口输出哪路高电平则对应点亮哪路指示灯。

04 时钟电路原理

时钟电路如图 4-1 所示:

图 4-1

采用 50Mhz 有源晶振产生时钟信号,接法采用有源晶振的典型接法:PIN 1 悬空,PIN 2 接地,PIN 3 输出时钟信号,PIN 4 接电源。由于FPGA的 I/O 供电为 3.3V,而时钟电路产生的时钟信号要由 I/O 口接收,因此时钟信号最大值不能超过 3.3V,故时钟电路电源采用 3.3V 供电。

05FPGA 部分电路原理

FPGA 部分电路原理图如图 5-1 所示:

图 5-1

Header 18X2 为 18 排 2 列排阵,两组排阵分别与 PIN 口、3.3V 电源、数字地相连,提供了可动的机制,使得 PIN 口可根据需要用排线与目标相连,达到信号传输的目的。而 3.3V 电源以及数字地针口则可以根据需要,用排线为目标提供逻辑高电平或逻辑低电平。

U21D 为 FPGA 芯片的时钟信号接收部分,通过网络标号“CLK0~3”与对应的时钟信号端口相连。

U21C 为 FPGA 芯片的供电及接地部分,含有“GND”字样的是“地”端口,与数字地相连,VCCIO1~4 为 I/O 口供电端口,采用 3.3V 电源供电,通过网络标号“+3.3V”与 3.3V 电源端口相连。VCCA_PLL1、VCCA_PLL2、VCCINT 为内部运算器和输入缓冲区的供电端口,采用 1.5V 电源供电,通过网络标号“+1.5V”与 1.5V 电源端口相连。

U21B 为 JTAG 与 AS 下载部分,TMS、TCK、TD1、TD0 分别为 JATAG 下载方式的模式选择端、时钟信号端、数据输入端、数据输出端。DATA0 为 AS 下载的数据端口,MSEL0、MSEL1、nCE、nCEO、CONF_ DONE、nCONFIG、nSTATUS 端口按照典型接法相连。值得注意的是:无论 AS 还是 JTAG 都是通过 JTAG 标准通讯,AS 下载一般是下载 POF 到 PROM(flash)里,重新上电仍然可以加载,JTAG 下载是通过 JTAG 口将 sof 文件直接下载到 FPGA 内,一般是临时调试用的,掉电就丢失了。

U22 是电可擦除 ROM,用于存放 AS 下载后的数据,使得 FPGA 的程序段掉电也能得以保存,DATA 端是数据读取端,用于读取 ROM 内数据。DCLK 为时钟端口,用于接收时钟信号进行同步传输。nCS 是片选端口,用于接收片选信号表示对该芯片进行通讯。ASDI 为 AS 下载数据输入端,用于接收 AS 下载数据。VCC 与 GND 分别为电源端口与地端口,分别接 3.3V 与数字地。

编辑:hfy

-

FPGA

+关注

关注

1629文章

21735浏览量

603152 -

发光二极管

+关注

关注

13文章

1199浏览量

66312 -

电机驱动

+关注

关注

60文章

1216浏览量

86740 -

微型电机

+关注

关注

2文章

93浏览量

23613 -

时钟电路

+关注

关注

10文章

236浏览量

50719

发布评论请先 登录

相关推荐

几种小型直流电机驱动电路

电机供电电路及驱动电路原理解析

电机供电电路及驱动电路原理解析

评论