在这篇文章中,我们将介绍如何调用 Hyperlynx®、如何设置简单的原理图以及如何运行一些基本的仿真操作。Hyperlynx® 可支持下列两种仿真工作流程。

LineSim:

用来预布局仿真,是设计周期中的早期仿真工具,主要用来评估假设情景并帮助定义电路板参数和布线指南。通过创建 I/O 缓存器、走线,终端以及连接器/电缆组件的示意图,在“Schematic GUI”中完成 LineSim 中的仿真。

BoardSim:

用于布局后仿真以对 PCB 设计进行分析。PCB 中所需的网络从布局文件中选出,然后在像 LineSim 这样的工具中进行仿真。由于它使用的是含布线约束、相邻网络布线以及距离等信息的布局文件,仿真是高度准确的。 可以在 LineSim 中查找任何违规操作或所需的更改,并在最终 PCB 上签发制造之前将其反馈到布局中。

在本系列中,可以使用 LineSim 和 Boardsim(如需要),具体取决于所讨论的主题。

现在我们通过一个简单的仿真操作来了解一下这个工具。调用 Hyperlynx® 并选择“New -> New SI Schematic”,如果调用的是“Waveform Viewer”,选择“Both”或“Oscilloscope”

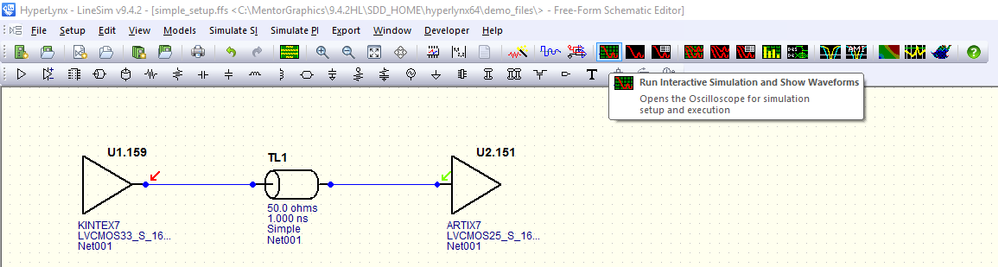

Hyperlynx® 支持 SI 仿真所需的基本元素,如下面的屏幕截图所示:

发射器和接收器(IBIS 模型)

传输线

“Simple”、“Microstrip”、“Stripline”、“Wire”、“Cable”、“Connector”

叠加线和耦合线

通孔

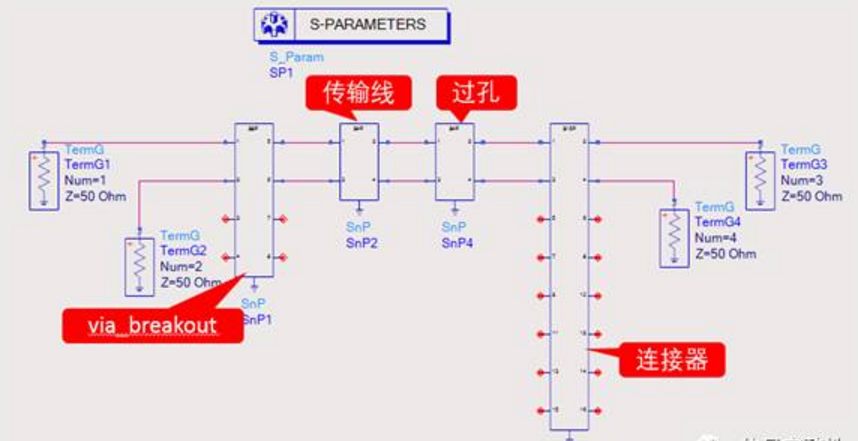

S 参数/Spice 模型

电压和接地

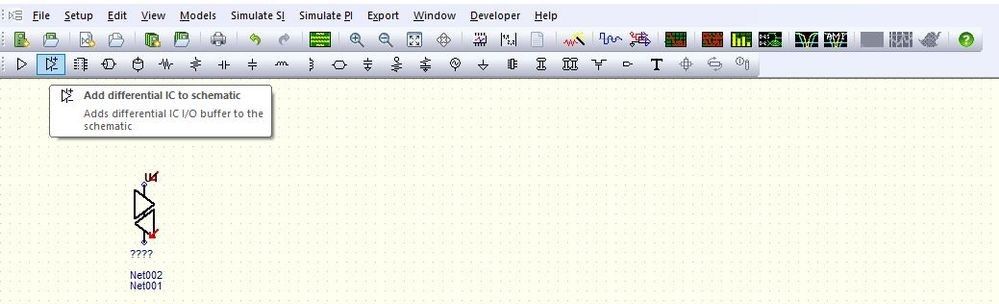

要创建原理图,请针对单端 I/O 标准选择“Add IC to Schematic”或针对差分 I/O 标准选择“Add differential IC to Schematic”。

单端建立:

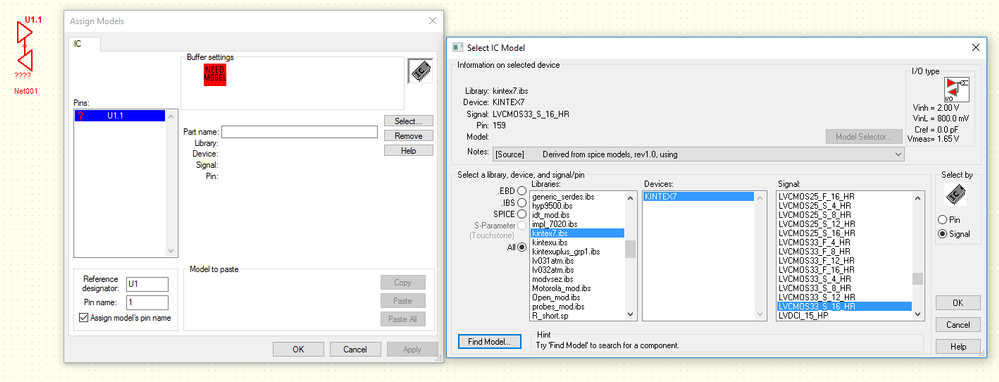

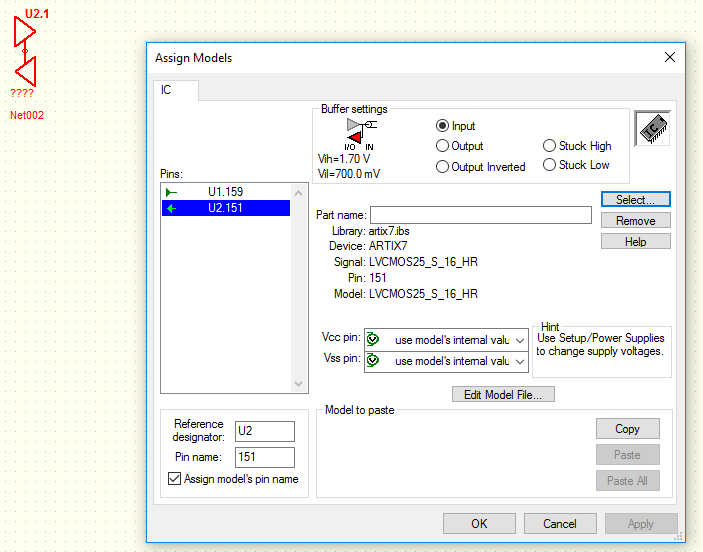

双击 IC 打开“Assign Models”窗口。我们将使用单端 I/O 标准 LVCMOS33。

注意:您需要将 IBIS 文件 (.ibs) 保存在 Hyperlynx® 的“Libs”文件夹 (C:/MentorGraphics/9.4.2HL/SDD_HOME/hyperlynx64/Libs) of Hyperlynx® 中,才能在默认库中查看它。 您可以选择在“Setup -> Options ->Directories”下的“Model-Library”文件路径中添加更多文件夹。要包含设计文件夹中的所有文件夹,务必选中“Add design folder”和“Add design folder subfolders”。

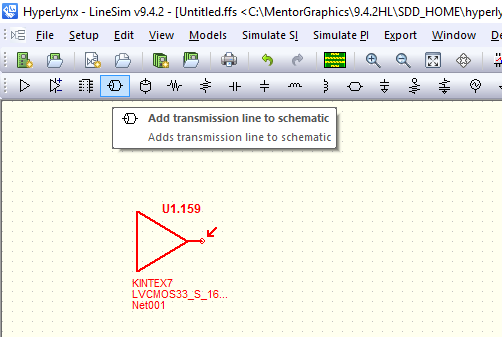

选择必要的模型设置(在此示例中为变送器,因此应选择输出),然后单击“OK”

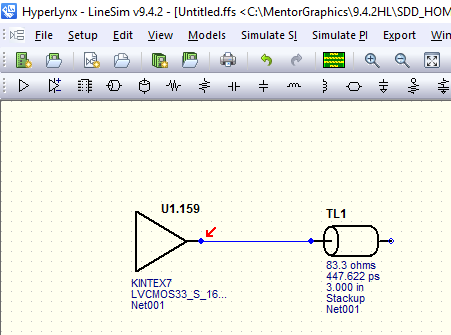

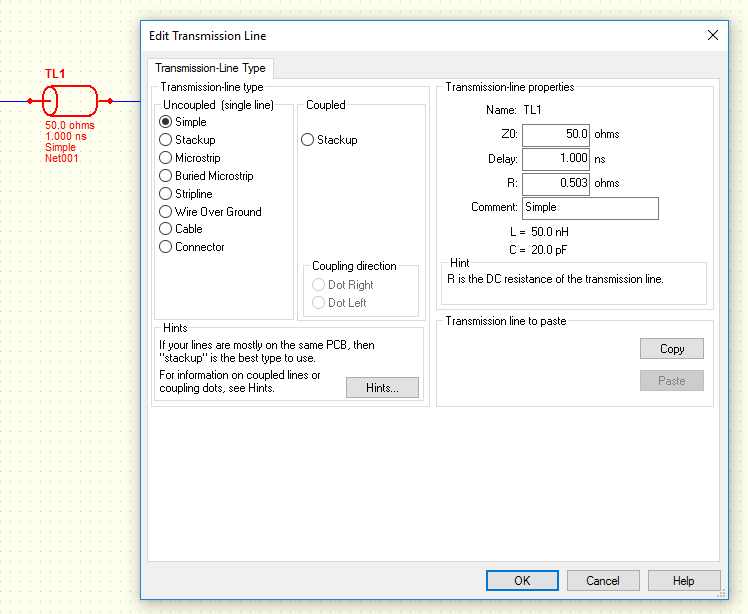

单击“Add transmission line to schematic”

双击 TL1 设置传输线并选择“Simple”非耦合类型,然后将“Z0“设置为 50 ohms、将“Delay”设置为 1.000 ns

通过选择必要的“Receiver IBIS Model”并将“Buffer”设置为“Input”来设置“接收器”并完成原理图。保存原理图设置。

运行仿真,选择“Run Interactive Simulations and Show Waveforms”按钮(该按钮会打开“Digital Oscilloscope”窗口)。

在“Oscilloscope”窗口中设置以下设置,然后单击“Start Simulation

Operation -> Standard

Stimulus -> Global,

Oscillator -> 100 MHz, 50% Duty

IC modeling -> Typical

Thresholds for -> U2.151

Horizontal Scale -> 5 ns/div”

蓝线显示 U2 的 Vinh、Vinl 阈值。在确定接收器波形是否如预期那样超过这些阈值时,上述步骤非常有用,让接收器可以确定所需的逻辑是“Low”还是“High”。 RX 波形 (绿色)和 TX 波形 (红色)的转换不清晰,我们会在本系列后面的主题中详细讨论。

差分建立:

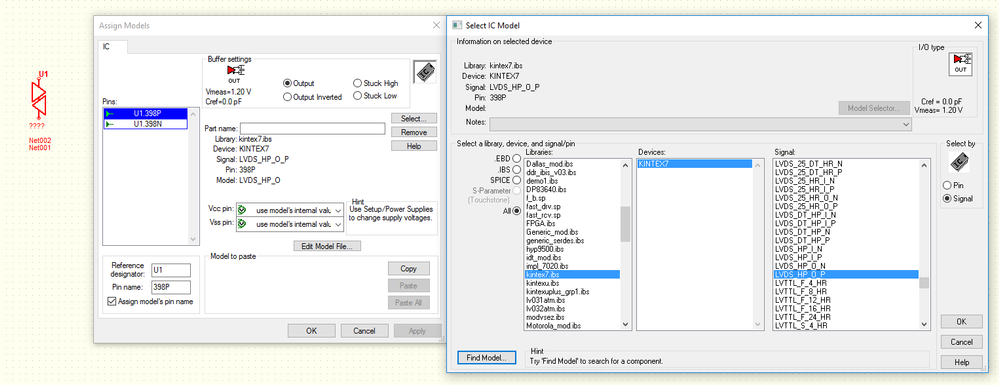

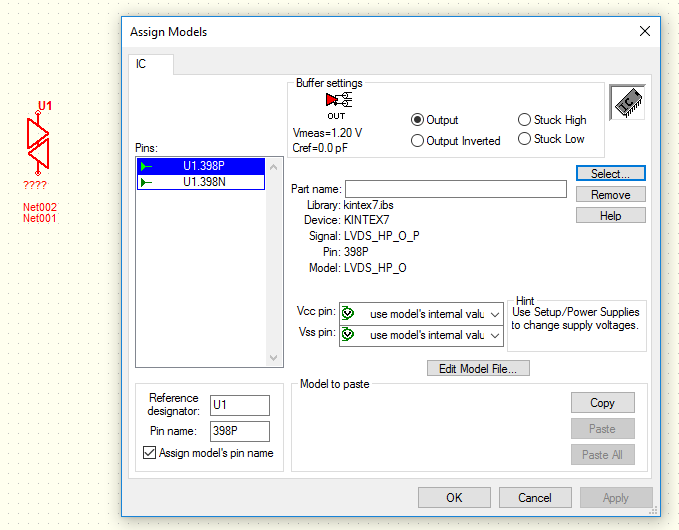

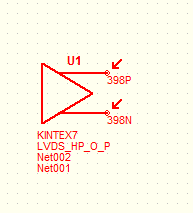

“Add differential IC to Schematic”后双击 IC,打开“Assign Models”窗口。我们将通过差分 I/O 标准 LVDS 来进行此建立,因为它是最常用的差分 I/O 标准之一。

选择必要的模型设置。在这个示例中用的是一个发射器,因此“P”后缀被选为输出,而且“N”会自动变为“Output Inverted”,因为这是一个差分缓存器。单击“OK”。

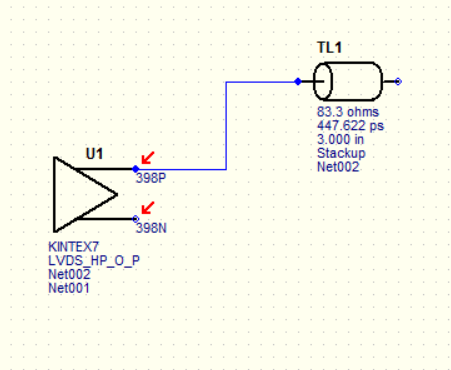

单击“Add transmission line to schematic”。

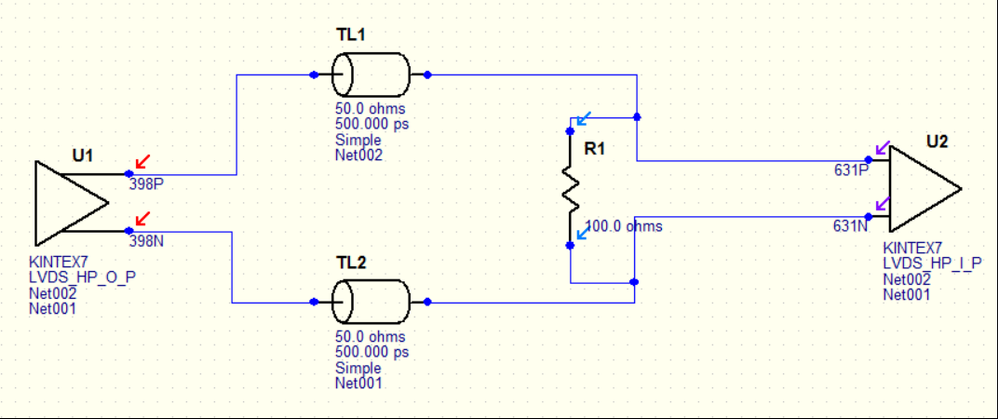

双击 TL1 设置传输线。如果是非耦合类型,选择“Simple”,然后将“Z0”设置为 50 欧姆;将“Delay”设置为 0.5 ns,并选择“Copy”以重复使用“N”传输线。

添加 TL2,双击“Edit”,然后选择“Paste”将 TL1 的属性复制到 TL2。

通过选择必要的“Receiver IBIS Model”并将“Buffer”设置为“Input”来设置“Receiver”。这样原理图就完成了。

保存原理图设置。

添加 LVDS 所需的 100 欧姆终端电阻,并通过双击“R”符号将值设置为 100 欧姆。

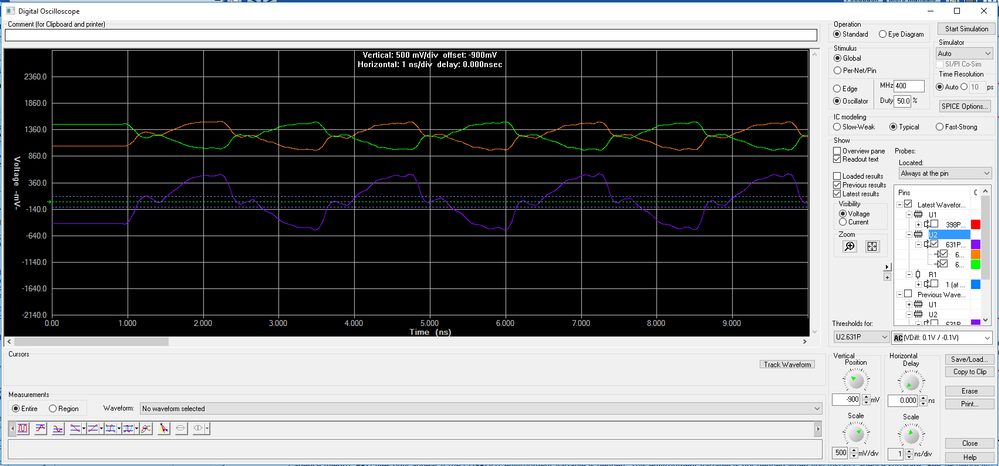

通过选择“Run Interactive Simulations and Show Waveforms”按钮。(该按钮随即会打开“Digital Oscilloscope”窗口)来运行仿真。在“Oscilloscope”窗口中输入以下设置,然后单击“Start Simulation”:

Operation -> Standard

Stimulus -> Global,

Oscillator -> 400 MHz, 50% Duty

IC modeling -> Typical

Thresholds for -> U2.631P

Horizontal Scale -> 1ns/div

Horizontal Scale -> 1ns/div

Vertical Position -> -900 mv/div

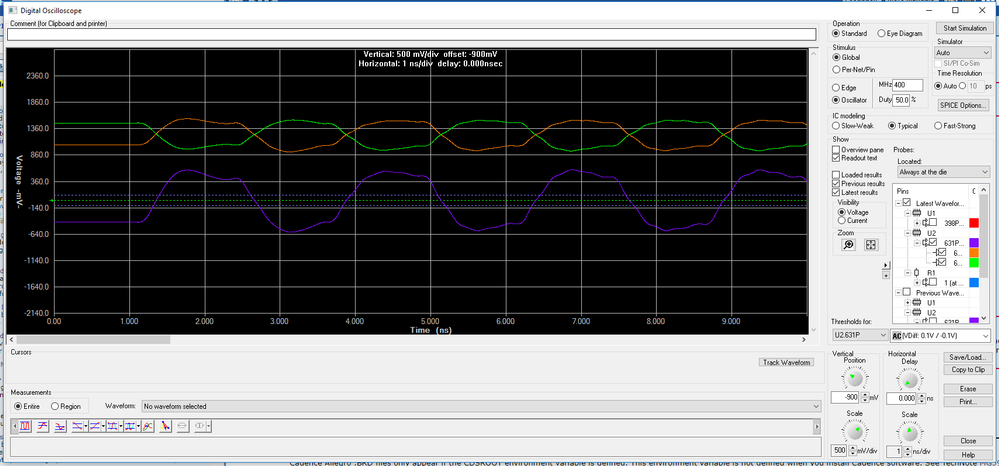

信号探测可以在“At the Pin”或“At the die”处完成。

在引脚处探测:

如果您在电路板上的引脚上进行物理探测,此操作指的是将仿真探头置于引脚上,从而展示您在实验室示波器中会看到的结果。“Purple”是差分探头的波形。

在裸片处探测:

指的是将仿真探头放置在裸片内从而展示裸片所看到的、无法在电路板上探测到结果。

有关如何对内部和外部终端进行探测的详情,请参阅(Xilinx Answer 57566)。

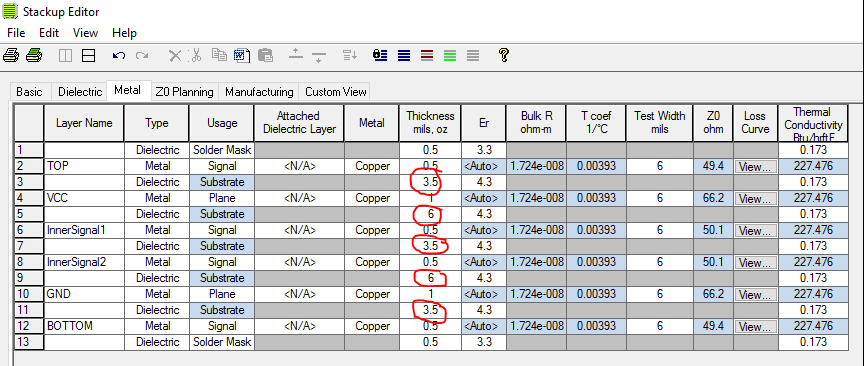

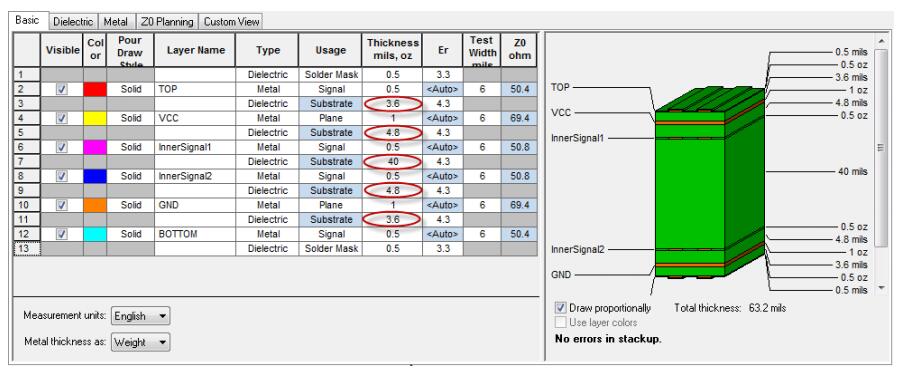

定义 Stackup

PCB 的叠层需要针对介电材料、金属类型、信号以及平面层在电路板中其他项目的布置来进行定义。在运行仿真之前进行此设置有助于模拟 PCB 及各种特性(例如走线阻抗、走线分离及其他参数等)。

Hyperlynx® 提供了一个含基于电子数据表视图的 Stackup Editor(您可以在该视图中输入值和图像面板以使叠加结果可视化)。编辑器可以通过选择“Setup -> Stackup Edit”或“Edit Stackup”按钮来访问,如下所示:

如上图所示,编辑器有各种标签及其快捷说明。

基要:通过添加/删除层、设置测量单位(英制/公制)和金属厚度(厚度/重量)来定义叠层信息。

介电:定义叠层的介电特性,如技术、损耗角正切和导热系数。可以选择根据周围的介电层来计算金属层的介电常数。

金属:定义金属特性,如金属类型(铜/铝/锡等)、厚度和金属的其他属性。

Z0 规划:定义叠层的特征阻抗。此计划编制标签是最有用的标签之一,因为它让您能够在计算单迹和差分对走线的特定目标阻抗时得出最佳数据。

制造:定义金属表面的粗糙度和痕量蚀刻参数。

定制视图:用来设置从其他标签派生的电子数据表信息的自定义视图,并可根据用户偏爱进行调整。

有关这些标签的高级详细信息,请参阅“Hyperlynx”用户指南。

现在我们来设置一个“Z0”为 50 欧姆的叠层,因为这是最常用的值。走线阻抗由走线的“Width”、参考平面上方的“Height”或“Dielectric thickness”以及“Dielectric constant”来决定。有多种方法来可设置叠层编辑器中的阻抗,然而我们将使用“Metal”标签来快速设置所需的阻抗。

打开“Stackup Editor”,然后单击“View -> Calculate Z0”(如果未启用,则启用它)。这样工具就可以基于叠加来自动计算特征阻抗了。

如下所示,选择“Metal”标签,然后设置“电介质厚度”,并将信号层标记为“Z0”。

确保在您修改参数后,“Picture”面板中显示“No errors found in stackup”的消息。

通过“Z0 Planning”标签来检查单迹和差分对的目标阻抗所需的走线宽度和间距。这个步骤很有用,由于接口/协议具有不同的阻抗要求,因此此标签有助于理解要满足这些规格所需的宽度或间距。

1. 适用于单迹:从“Plan for”下拉列表中选择“单迹”,并在信号层的“Target Z0”值列中输入 50、60、40、50,然后按“Enter”键。实现这些阻抗所需的“Trace”宽度随即会被更新。

2. 适用于差分对:从“Plan for”下拉列表中选择“差分对”,在“Strategy”中选择“Solve for width”,然后在信号层的“Target Z0”值列中输入 100、90、80、100。现在按“Enter”键。实现这些阻抗所需的“Trace”宽度随即会显示。也可以按照差分走线分离策略,通过选择“Solve for Separation”的方法来满足“Target Z0”的需要。此策略还包括使用两者(即“Solve for width”和“Solve for Separation”)的选项,并在“Z0 Curve”列中显示结果。

堆栈现已创建,可将其导出以便在将来进行设计和仿真时重用,从而节省时间。单击“File -> Export -> save as .stk file”

单击“OK”关闭编辑器。

注意:PCB 设计的叠层创建是设计进程中最重要和最关键的步骤之一,需要根据复杂性投入所需的时间和精力。“What If”分析可以在编辑器中根据设计和制造要求使用,以实现最终的叠加。但是,上述步骤旨在深入了解编辑器,并仅针对本系列中提及的未来设计和仿真提供叠加。这些步骤不基于任何设计参数。

接下来你们可以通过我们上面讨论的步骤来熟悉这些工具和接口。

在下一篇文章中,我们将介绍 Hyperlynx® 的其他一些功能,为您提供如何使用该工具的基础知识。

在那之前,好好熟悉一下这个工具及各种设置,我们下次再见。

编辑:hfy

-

PCB设计

+关注

关注

394文章

4703浏览量

86598 -

信号完整性

+关注

关注

68文章

1417浏览量

95690

发布评论请先 登录

相关推荐

HYPERLYNX 仿真工具使用指南

信号完整性仿真应用

信号完整性与电源完整性的仿真分析与设计

基于HyperLynx的高速DSP信号完整性仿真

信号完整性仿真实验:Hyperlynx®调用及两种仿真工作流程

信号完整性仿真实验:Hyperlynx®调用及两种仿真工作流程

评论