软件定义无线电是当今业界的主要话题之一。射频(RF)收发器在单芯片集成电路中(IC)中提供了完整的无线电解决方案,推动了软件定义无线电的领域的发展。ADI 收发器产品线推出了这类强大的芯片,正快速应用于许多通过软件控制的无线电设计中。但是如何获得较低的相位噪声仍是使用这些器件需要探索的领域之一。本文评估这些高度集成的射频集成电路(RFIC)的相位噪声性能,重点评估提供外部频率时的情况。

使用外部本振(LO)时对ADI公司 ADRV9009 收发器进行测量表明,当使用低噪声LO时,可显著改善相位噪声。从相位噪声贡献角度来分析收发器架构。通过一系列测量,残余或加性相位噪声被提取为在DAC输出编程的频率的函数。利用该噪声贡献以及LO和参考电压输入频率的相位噪声,可估计出发射输出的总相位噪声。将这些估计值与测得的结果进行比较。

动机

相位噪声是无线电设计中表征信号质量的重要指标之一。在架构定义阶段需要进行大量工作,确保以经济的方式满足相位噪声需求。

通过分析ADRV9009收发器的测量结果,其噪声性能结果却决于所选架构,不同架构结果差异较大。使用内部LO功能时,相位噪声由IC内部的锁相环(PLL)和压控振荡器(VCO)决定。内部LO在设计上能满足大多数通信应用的需求。对于需要改进相位噪声的应用,将低相位噪声源作为外部LO时,可显著改进相位噪声。

如图1所示,ADRV9009收发器在10 kHz至100 kHz频段相位噪声改善超过40 dB。以上测量的条件为:对于内部LO测量,LO频率设置为2.6 GHz, DAC输出为8 MHz。对于外部LO测量,Rohde & SchwarzSMA100B用作LO源。由于外部LO信号需要经过ADRV9009的内部分频器,因此为获得2.6 GHz的LO频率,信号源设置为5.2 GHz。使用Holzworth HA7402相位噪声分析仪进行相位噪声的测量。

图1. ADRV9009收发器相位噪声测量。使用内部LO时,相位噪声受到IC内部PLL/VCO的限制。如果使用低相位噪声外部LO,可显著改进相位噪声。

ADRV9009收发器

ADRV9009是ADI收发器产品线的新产品。收发器架构如图2所示。该芯片使用直接变频架构,将发射和接收双通道收发链路集成在单芯片中。其中包含正交校正、直流失调和LO泄漏校正等数字处理算法,这些算法保证了直接变频架构的性能。收发器提供了射频(RF)与数字之间转换的完整功能。支持高达6GHz的RF频率,JESD204B接口则为基于ASIC或FPGA的处理器提供高速数据接口。

图2. ADRV9009收发器功能框图。

无线电与外部输入的参考频率同步。转换器时钟、LO和数字时钟的PLL均会与参考时钟锁相。通过外部LO的配置可以绕过内部LO PLL。LO路径的PLL或外部LO输入与混频器端口之间有一个分频器,用于生成直接变频架构所需的正交LO信号。转换器时钟和LO会直接影响相位噪声,在评估相位噪声贡献因素时我们会对此进行进一步讨论。

检查相位噪声贡献因素

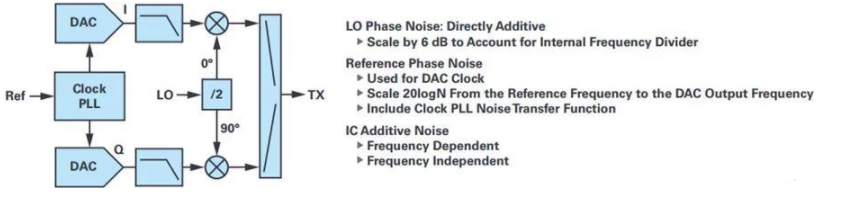

发射的相位噪声由多个因素组成。图3阐明了使用直接变频波形发生器架构的简单功能框图以及主要相位噪声因素。

图3. 直接上变频功能框图和关联相位噪声贡献因素。

在倍频器或分频器中,相位噪声的比例为20logN,其中N是输入输出频率比。

这比例也适用于直接数字频率合成器(DDS),其中时钟噪声贡献与DDS输出频率的比例为20logN。

要考虑的第二个方面是PLL中的相位噪声传递函数,注入PLL的基准频率将作为频率比例函数(类似于倍频器)按比例分配到输出,但会受环路带宽(BW)和所选的环路滤波器所形成的低通滤波器影响。

将这些原则应用于收发器,可检查各种噪声因素的贡献。注入收发器的频率有两种,即LO频率和基准频率。LO频率直接影响相位噪声输出,但在用于创建混频器正交LO信号的内部分频器中减少了6 dB。基准频率贡献由几个因素决定。它用于在时钟PLL中创建DAC时钟。时钟输出上由于基准频率而产生的噪声将与PLL的噪声传递函数成比例。然后,这种噪声贡献再次与DAC时钟与DAC输出频率比成比例。这种效果可以简化为基准频率和DAC输出频率的比例,并受PLL BW低通传递函数影响。

接下来,考虑收发器相位噪声贡献。在发射路径中,所有电路元件都会产生残余噪声,另一个噪声贡献是DAC输出的加性噪声,它随DAC输出频率而变化。这可以总结为两个残余相位噪声术语:频率相关噪声贡献和频率无关噪声贡献。频率相关噪声与DAC输出频率的比例为20logN。频率无关噪声是固定的,将作为收发器的相位噪底。

为了提取IC残余噪声贡献作为频率相关贡献因素和频率无关贡献因素的函数进行了一系列相位噪声测量,如图4所示。

(a). The Reference Frequency and LO Frequency.

(b). The Transceiver Transmit Output Phase Noise.

(c). The Transceiver Residual Phase Noise.

图4. 用于提取可变相位噪声贡献因素的相位噪声测量。

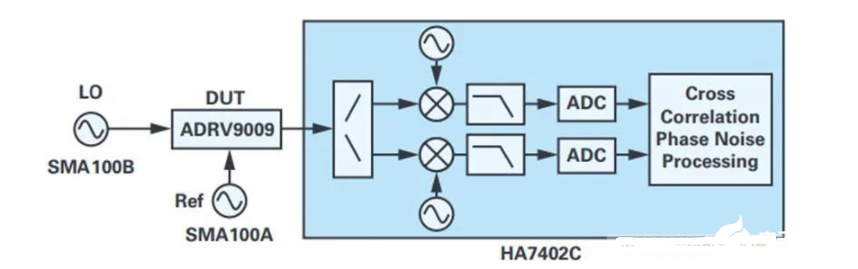

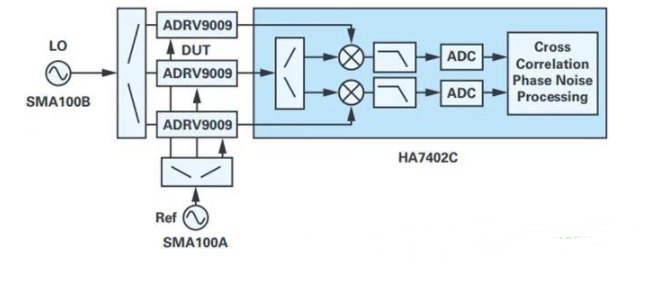

用于相位噪声测量的测试设置如图5所示。对于收发器LO和基准频率输入,分别使用了Rohde & Schwarz SMA100B和100 A。Holzworth HA7402C用作相位噪声测试设置。对于绝对相位噪声测量,将收发器的发射输出注入测试设置。对于残余相位噪声测量,需要三个收发器,并且将额外的收发器作为测试设置中混频器的LO端口,可从测量中去除基准频率和LO频率的噪声贡献。

(a). Absolute Phase Noise Measurement.

(b). Residual Phase Noise Measurement.

图5. 用于相位噪声测量的测试设置。

通过评估图4的实测数据,从收发器IC中提取了频率相关和频率无关相位噪声贡献因素。估计值如图6所示。估计值来自于对实测数据的拟合结果以及在偏移频率大于1 MHz时对相位噪底应用的阈值设置。

图6. 收发器残余相位噪声贡献。这些曲线是从图4的实测数据中提取出来的。

绝对相位噪声测量和预测

如前所述通过评估不同相位噪声贡献,基于DAC输出频率以及用于参考和本振的振荡源,相位噪声可以通过计算预测。实测和预测结果如图7所示。

(a). DAC Ouput = 12.5 MHz.

(b). DAC Output = 25 MHz.

(c). DAC Output = 50 MHz.

(d). DAC Output = 100 MHz.

图7. 外部LO的测量相位噪声与预测相位噪声的对比。对于2.6 GHz的收发器中心频率,LO设置为5.2GHz。DAC输出频率从12.5 MHz到100 MHz不等。结果是可预测的,并表明这种分析方法可以推广到额外的频率。

贡献可通过下式计算:

LO相位噪声贡献:使用了图4测得的LO相位噪声,并将其降低了6 dB,以对应收发器内部的分频器。

参考相位噪声贡献:以图4的实测参考噪声作为起始点。收发器中的时钟PLL具有几百kHz的环路带宽,因此采用具有类似环路带宽的二阶低通滤波器来抑制参考噪声。然后将噪声按DAC输出频率与基准频率比的20log进行缩减。

IC贡献:使用了图6的曲线。

测量结果与预测结果非常接近,图表显示了哪些贡献因素控制不同的偏移频率。在低于5 kHz左右的偏移频率下,第一个LO占主导地位。在高于1 MHz左右的偏移频率下,IC残余噪声占主导地位。在10 kHz左右至500 kHz左右的中等偏移频率下,DAC输出频率成为一个因素。在较高的DAC输出频率下,IC频率相关噪声占主导地位。降低DAC输出频率时,IC贡献减至LO频率主导性能的那个点。

外部LO考虑因素

探索外部LO用法的设计有一些因素值得注意。有两点可能有所限制:

使用内部分频器时,启动或切换外部LO时存在相位模糊。内部LO包含RF相位同步功能,这是外部LO尚不具备的。

当外部LO跳频时,QEC算法存在一个建立时间,该时间可能在频率变化后的瞬间以杂散方式影响图像。

这两项都导致了多通道系统跨越大于收发器瞬时带宽工作的复杂性。未来的收发器可能会克服这些限制,但在撰写本文之际,当ADRV9009与外部LO一起使用时,这些复杂性依然存在。

尽管存在这些复杂性,仍有许多应用可以利用外部LO改进相位噪声。其中包括具有不太严格的动态跳频要求的任何单通道或低通道系统,或任何具有固定LO频率的多通道系统。

如窄带相控阵这种特殊应用使用外部LO可以获得更好的相位噪声性能。在该应用中,使用收发器作为通用波形发生器和接收器是切实可行的,它可以支持各种工作频率,然后在实际运行或最终的LO实现中选择特定的频段。

对于工作频带在收发器瞬时带宽内的相控阵系统,外部LO可以是单一频率,在这种情况下,使用外部LO结构来构建相控阵是一个非常实用的选择。在评估系统相位噪声时,可以选择一个噪声远远小于LO的参考频率信号。如果将一个公共LO分布到多个收发器,当系统中收发器数量增加时,来自IC的噪声贡献将降低,直到系统噪声主要来自于外部LO。该结论简化了系统工程噪声分析。由于噪声主要由公共LO控制,工程工作可以集中在中央LO设计的性能/价格权衡上。

总结

现在有一种方法是利用外部LO来预测ADRV9009收发器相位噪声。该方法允许利用DAC输出频率的函数方程来跟踪参考振荡器、LO源和收发器的贡献。测量结果与预测结果非常吻合,表明该方法也可用于分析使用其他参考源是收发器的性能。这种方法也很普遍,可以用于任何波形发生器的设计中。

在努力创建低相位噪声LO源时,使用外部LO测得的相位噪声性能有明显的优势。我们的目的是在评估架构选项时为系统设计人员提供一系列选项。对于使用收发器外部LO输入的低相位噪声应用中,该描述为在各种条件下评估系统级相位噪声奠定了基础。

在评估系统相位噪声时,可以选择噪声贡献远远小于LO的参考频率源。如果将一个公共LO分布到多个收发器,当系统中收发器数量增加时,来自IC的噪声贡献将降低,直到系统噪声主要来自于外部LO。该结论简化了系统工程噪声分析。由于噪声主要由公共LO控制,工程工作可以集中在中央LO设计的性能/价格权衡上。

在努力创建低相位噪声LO源时,使用外部LO测得的相位噪声性能有明显的优势。我们的目的是在评估架构选项时为系统设计人员提供一系列选项。对于使用收发器外部LO输入的低相位噪声应用中,该描述为在各种条件下评估系统级相位噪声奠定了基础。

ADRV9009

●双发射器

●双接收器

●双输入共享观察接收器

●最大接收器带宽:200 MHz

●最大可调谐发射器合成带宽:450 MHz

●最大观察接收器带宽:450 MHz

●全集成的小数 N 射频合成器

●全集成的时钟合成器

●适用于射频 LO 和基带时钟的多芯片相位同步

●JESD204B 数据路径接口

●调谐范围:75 MHz 至 6000 MHz

编辑:hfy

-

收发器

+关注

关注

10文章

3524浏览量

106428 -

无线电

+关注

关注

60文章

2154浏览量

117057 -

压控振荡器

+关注

关注

10文章

134浏览量

29405

发布评论请先 登录

相关推荐

光纤收发器与IO-Link收发器的区别

光纤收发器指示灯的常见故障及解决方案

无线收发器工作原理,无线收发器怎么使用

AN-557:实验者项目:在业余无线电收发器内集成AD9850DDS器件以实现数字本振功能

AFE7070模拟本振的输入端LO,想使用CDCM6208输出,这个可以直接使用吗?

801系列光纤收发器:打造全能型数据传输解决方案

使用外部本振(LO)时对ADRV9009 收发器测量解决方案

使用外部本振(LO)时对ADRV9009 收发器测量解决方案

评论