时钟篇

选用全局时钟缓冲区(BUFG)作为时钟输入信号,BUFG是最稳定的时钟输入源,可以避免误差。

只用一个时钟沿来寄存数据,使用时钟的两个沿是不可靠的,如果时钟沿“漂移”,就会导致时序错误。

不要随意将内部信号作为时钟,如门控时钟和分频时钟,而要使用CLKDLL或者DCM产生的时钟,或者可以通过建立时钟使能或者DCM产生不同的时钟信号。

FPGA尽量采取同步设计,也就是所有时钟都是同一个源头,如果使用两个没有相位关系的异步时钟,必须要解决跨时钟域问题。

性能篇

逻辑级的时延不要超过时序预算的百分之五十,否则会影响系统的运行频率。可以通过分析时序报告中某个路径的时序统计量来掌握系统的逻辑级时延。

对于关键的输出选择快速转换速率,可以为LVCMOS和LVTTL电平选择转换速率来降低输出时延。

如果设计允许增加延迟,可以对组合逻辑采用流水操作来提高性能。

利用四种全局约束来对设计进行全局约束,周期、偏置、输入/输出,管脚到管脚。

I/O寄存器提供了最快的时钟到输入、输出到时钟的延时,对于输入、输出信号,管脚到寄存器、寄存器到管脚都不可以有组合逻辑存在,对于三态寄存器,必须低电平有效,才能被综合到IOB当中。

尽量使用IP核进行设计,因为IP核都是针对FPGA器件进行了优化,性能更高。

编程篇

使用Case语句而不是if-then-else语句

复杂的if-then-else语句在综合布局布线以后会生成优先级译码逻辑,增加路径上的时延。然而,case语句则综合为并行逻辑,没有时延。

有限状态机尽量不要包含有算术逻辑、数据通路逻辑以及其它与状态机不相关的组合逻辑;

状态机编写的时候,下一状态逻辑和输出译码逻辑必须放在独立的进程中或者always语句中,综合工具在输出和下一状态逻辑之间不允许共享资源。

尽量使用一位编码有限状态机;

使用不同风格的计数器,二进制计数器是非常慢的,可以考虑LFSR,Pre -scalar,Johnson.

代码设计要按照功能块划分成不同的层次,层次化有助于设计更加容易读懂,也容易调试和复用。

编辑:hfy

-

FPGA

+关注

关注

1634文章

21819浏览量

607389

发布评论请先 登录

相关推荐

FPGA时序约束之衍生时钟约束和时钟分组约束

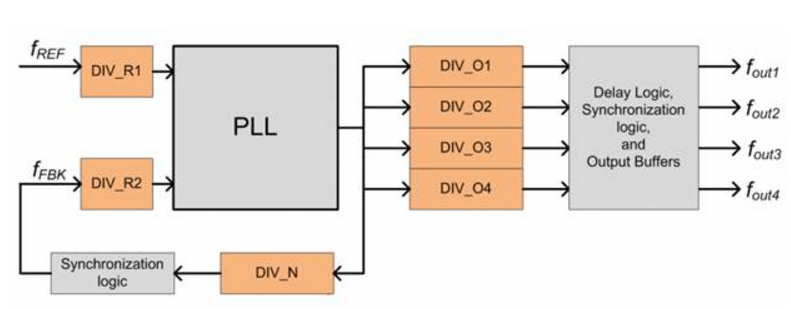

基于lmk03806的高性能可编程时钟发生器的设计与fpga实现 毕...

时钟IC怎么满足高性能时序需求?

基于FPGA的时钟设计

(10)FPGA跨时钟域处理

(12)FPGA时钟设计原则

(29)FPGA原语设计(差分时钟转单端时钟)

(30)FPGA原语设计(单端时钟转差分时钟)

FPGA设计小技巧(时钟/性能/编程)

FPGA设计小技巧(时钟/性能/编程)

评论