研究人员采用1.6μm 18-V CMOS技术制造了一个包含所提出的缓冲放大器的列驱动IC,其评估结果表明,在提供相同的沉降时间时,静态电流降低了39.2%。在几乎相同的静态电流汲取和占用的有效面积的情况下,所提出的放大器在沉降时间方面也实现了高达49.1%(90%下降)和19.9%(99.9%下降)的改进。

相关论文以题为“High-Speed Rail-to-Rail Class-AB Buffer Amplifier with Compact, Adaptive Biasing for FPD Applications”于2020年11月29日发表在《Electronics》上。

大尺寸、高分辨率平板显示器(FPD)面板的需求,对薄膜晶体管液晶显示器(TFT-LCD)列(数据或源)驱动器的低功耗、高回转率工作有强烈的要求。由于显示面板需要更大的尺寸和更高的分辨率,为了更有效地驱动大功率的电阻和电容负载,且具有低功耗、小面积和快速的沉降时间,液晶驱动系统的列驱动器变得非常重要。FPD面板的列驱动器一般包括移位寄存器、输入寄存器、数据锁存器、电平移位器、数模转换器(DAC)和带输出开关的输出缓冲器。

FPD驱动系统一般采用模拟或数字驱动方式。随着显示分辨率的提高,输出缓冲器的电阻和电容负载增加,而所需的沉降时间则减少。液晶柱驱动器的输出缓冲器的目标沉降时间应短于面板的水平扫描时间。轨对轨A类、AB类或B类放大器已被普遍用作FPD柱驱动器的缓冲放大器。输出缓冲放大器采用了轨至轨输入级和双路径推挽输出级,B类和AB类输出部分组合在一起,以提高回转率。

因此,随着偏置电流的增加,静态功耗也会增加,以提供高回转率的性能。为了在没有大的静态偏置电流的情况下提高回转率,人们提出了具有动态偏置的轨到轨、折叠式级联、AB类缓冲放大器。但是,它们存在一些缺点。动态偏置电路采用P型回转检测器来增加核心放大器N型输入差分对的尾部电流,采用N型回转检测器来增加P型输入差分对的尾部电流。

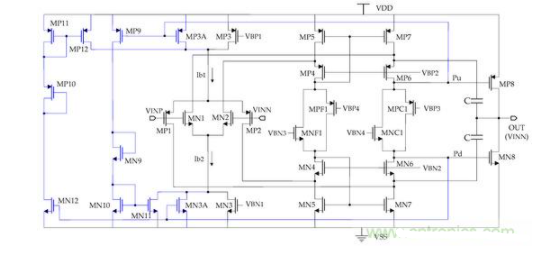

因此,可以提高回转率,但功率和面积开销也变大。此外,由于每个输入差分对都使用了相反类型的回转检测器,因此缓冲放大器不能在整个轨至轨输入信号范围内充分发挥作用。为了解决这个问题,人们提出了一种图1所示的改进型类AB输出放大器。在这个缓冲放大器中,动态偏置电路经过修改,允许使用与输入差分对相同类型的回转检测器来动态调整偏置电流,从而在整个轨到轨信号范围内实现了完全的回转率提升。然而,不幸的是,由此产生的动态偏置电路需要许多晶体管(多达26个晶体管)。因此,它仍然会导致功率和面积开销的大幅增加。所以,在TFT-LCD列驱动器的设计中,一个低功耗、小面积的高回转率输出缓冲放大器是不可缺少的。

图1.传统缓冲放大器 传统的缓冲放大器,在整个轨到轨输入和输出信号范围内具有回转率增强功能。

拟议的缓冲放大器

所提出的缓冲放大器的电路原理图如图2所示。它被配置为一个互补差分输入级,然后是一个浮动电流源级,用于提供轨至轨输入共模范围,并像传统的缓冲放大器那样进行class-AB操作。然而,与传统的缓冲放大器不同的是,所提出的缓冲放大器并没有使用具有辅助差分对和多个电流镜的笨重动态偏置电路来提高回转率。相反,它只集成了两个额外的晶体管,MP3A和MN3A,作为互补输入级中共源放大器的尾流源,它们分别由信号Pu和Pd驱动输出驱动晶体管MP8和MN8。用于MP3A(MN3A)电流镜像工作的晶体管MP9、MN9、MN10和MN11(MN12、MP10、MP11和MP12)用于整个轨至轨信号范围内的全回转率增强。MN9(MN10)通过降低电流镜像晶体管MN10和MN11(MP11和MP12)的漏极和栅极电压以及共源放大器的静态电流来降低静态电流,而MP9和MN12则作为额外的尾流源。

随后,研究人员所提出的缓冲放大器在输入级中结合了主尾流源(MP3和MN3)和辅助尾流源(MP3A和MN3A),以实现快速瞬态工作。这些辅助晶体管的尺寸比输出驱动器MP8和MN8小40倍左右。此外,由于窄幅效应,即MOS晶体管的阈值电压随着晶体管宽度的变窄而增加,MP3A和MN3A的阈值电压变得比MP8和MN8的阈值电压在稳定状态下要高。这些效应结合在一起,让MP3A和MN3A的偏置电流比MP8和MN8的偏置电流小很多。

例如,在研究人员的设计中(DC 8.5 V = VDD/2 @VDD = 17 V),MP3A和MN3A的尺寸是这样的,阈值电压被做成937和964 mV,而MP8和MN8的尺寸是这样的,阈值电压分别被做成808和831 mV,结果MP3A和MN3A的阈值电压比MP8和MN8的阈值电压高约130 mV。现在,将Pu和Pd的偏置电压分别设置为VDD 888和910 mV,使其大于MP8和MN8的阈值电压,而小于MP3A和MN3A的阈值电压。这导致MP3A和MN3A的偏置电流约为5 nA,与MP3/MN3(1.6 µA)、MP5/MN5(2.1 µA)、MP7/MN7(2.1 µA)和MP8/MN8(5.6 µA)的偏置电流相比,可以忽略不计,导致稳态下放大器的整体偏置电流几乎没有增加。

图2.建议的缓冲放大器在整个轨到轨信号范围内具有面积和功率效率的提升。

实验结果

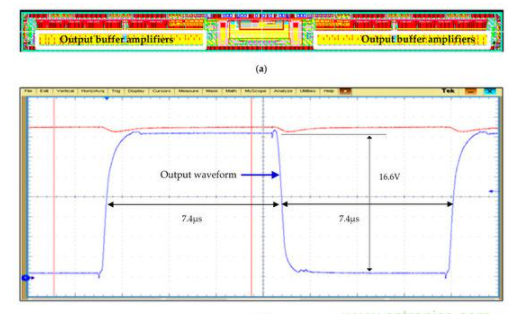

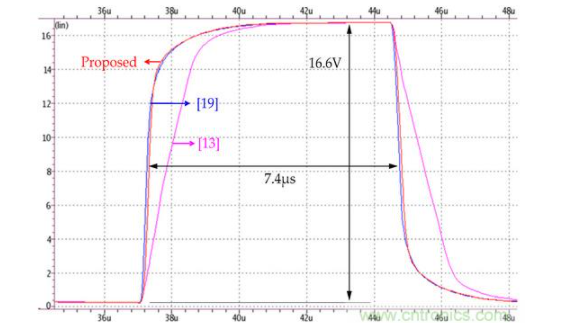

研究人员采用1.6 μm 18 V CMOS技术,设计并制造了一个包含所提出的缓冲放大器的大尺寸平板显示器(FPD)的列驱动IC。图3a描绘了列驱动IC的布局图,其中有源区占据了12 685μm2×1010μm2。图3b显示,测量到的点反转中白色图案(全摆)的输出波形证明了所提出的输出缓冲电路具有快速的瞬态响应。图4所示为传统缓冲放大器和所提出的缓冲放大器的仿真输出波形,其中的沉降行为可以进行比较。仿真的条件是,缓冲放大器在0.2 V~16.8 V的电压摆幅下,相同地驱动一个8.5ΚΩ的电阻和300 pF的电容作为55英寸TFT-LCD面板的柱线负载。由图4可知,所提出的输出缓冲器的上升和下降过渡的沉降时间比传统缓冲放大器快得多。需要注意的是,为了实现这种高性能,所提出的缓冲放大器所使用的静态电流远远低于传统缓冲放大器。

图3.采用所提出的输出缓冲放大器的列驱动IC。使用所提出的输出缓冲放大器的列驱动IC。(a)布局图和(b)测得的白色图案(VSS2 +0.2 V(0.2 V)-VDD -0.2 V(16.8 V))在点逆中的输出波形。

图4.缓冲放大器的模拟输出波形。

所提出的缓冲器放大器性能的提高来自于缓冲器可以使用较少的晶体管数量更有效地实现回转率的提高,从而获得更高的面积效率、更低的功耗和更快的沉降。以上提出的实验评估结果意味着,所提出的缓冲放大器适用于高回转率工作的放大器,非常适合作为大型高清晰度FPD的列驱动器。

结论

研究人员提出了一种具有自适应偏置电路的高速、低功耗、轨到轨、折叠式级联、AB类输出缓冲放大器。所提出的缓冲放大器采用了一种紧凑、新颖的自适应偏置方案来提高回转率。为了获得更快的瞬态响应,所提出的自适应偏置方案只需要两个附加尾流源的晶体管和八个电流镜的晶体管。这些额外的晶体管可以在回转期间为核心放大器提供大量的额外偏置电流,而在稳态期间消耗的电流可以忽略不计。所提出的自适应偏置方法可以适用于高回转率工作的放大器,并且非常适合大型高清晰度FPD中的列驱动器。

-

CMOS

+关注

关注

58文章

5707浏览量

235375 -

驱动IC

+关注

关注

9文章

302浏览量

33808 -

数模转换器

+关注

关注

14文章

1003浏览量

83165 -

缓冲放大器

+关注

关注

1文章

28浏览量

16677

发布评论请先 登录

相关推荐

MCU中运算放大器的应用与比较

5V精密CMOS运算放大器轨对轨输出输入增益恒定

缓冲放大器的几种类型介绍

什么是缓冲放大器

缓冲放大器的工作原理和优点

适用于大型平板显示器(FPD)应用高抖动率的轨缓冲放大器方案设计

适用于大型平板显示器(FPD)应用高抖动率的轨缓冲放大器方案设计

评论