1 概述

I2S(Inter—IC Sound)总线, 又称 集成电路内置音频总线,是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专门用于音频设备之间的数据传输,广泛应用于各种多媒体系统。I2S采用了沿独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。

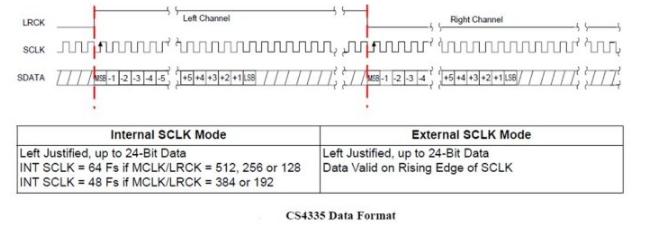

在飞利浦公司的I2S标准中,I2S主要有三个信号。

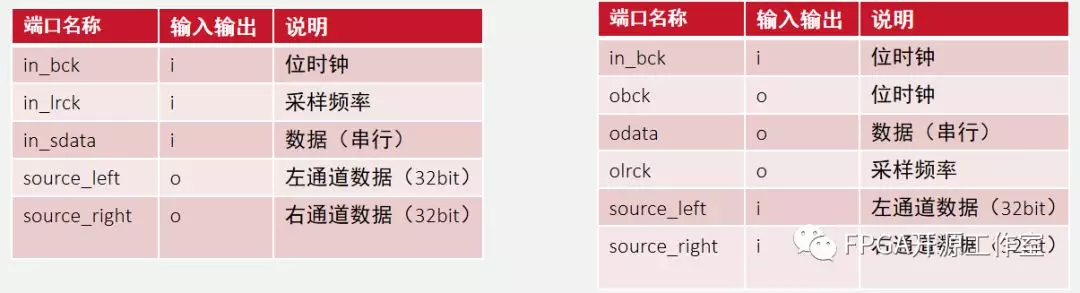

1.位时钟 BICK(也叫串行时钟SCLK),即对应数字音频的每一位数据,BCLK都有1个脉冲。BCLK的频率=2×采样频率×采样位数。

2.帧时钟LRCK,(也称WS),用于切换左右声道的数据。LRCK为“1”表示正在传输的是右声道的数据,为“0”则表示正在传输的是左声道的数据。LRCK的频率等于采样频率。

3.串行数据SDATA,就是用二进制补码表示的音频数据。

有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍。随着技术的发展,在统一的 I2S接口下,出现了多种不同的数据格式。根据SDATA数据相对于LRCK和SCLK的位置不同,分为左对齐(较少使用)、I2S格式(即飞利浦规定的格式)和右对齐(也叫日本格式、普通格式)。

以下是I2S Sample rate 44.1Khz 和48Khz部分系列。

2 模式

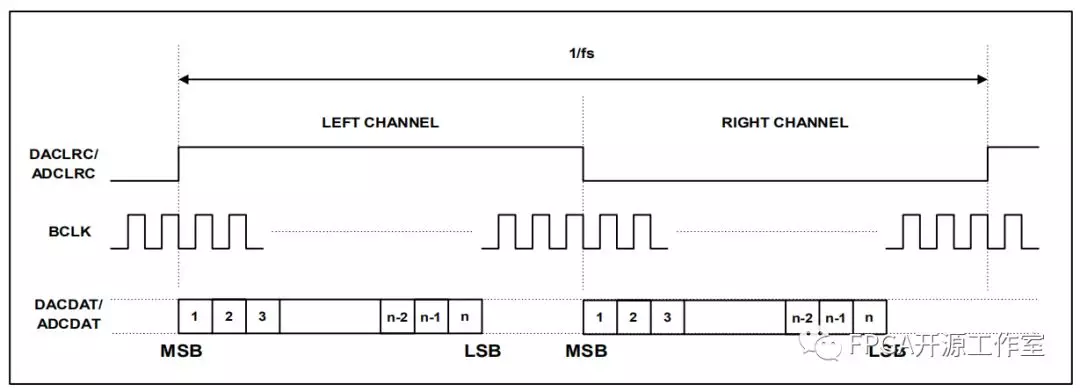

左对齐模式:SDATA 的MSB在BCLK的第一个上升获得根据LRCK的传输。

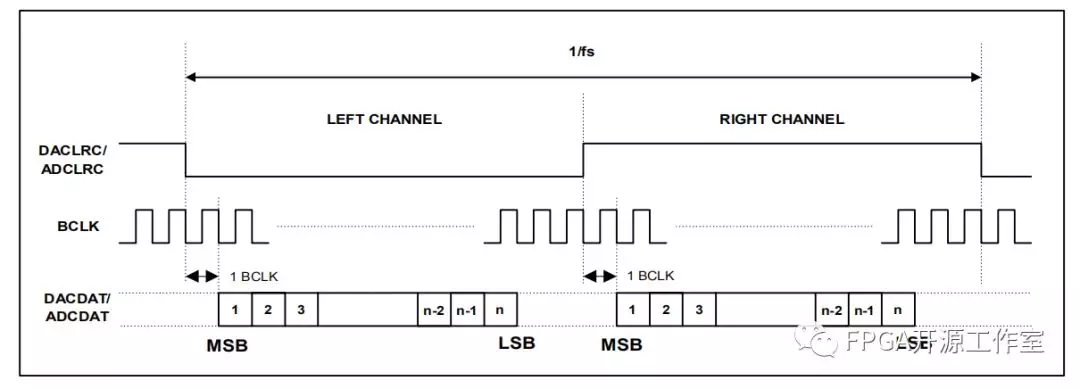

I2S模式:SDATA 的MSB在BCLK的第二个上升获得根据LRCK的传输。

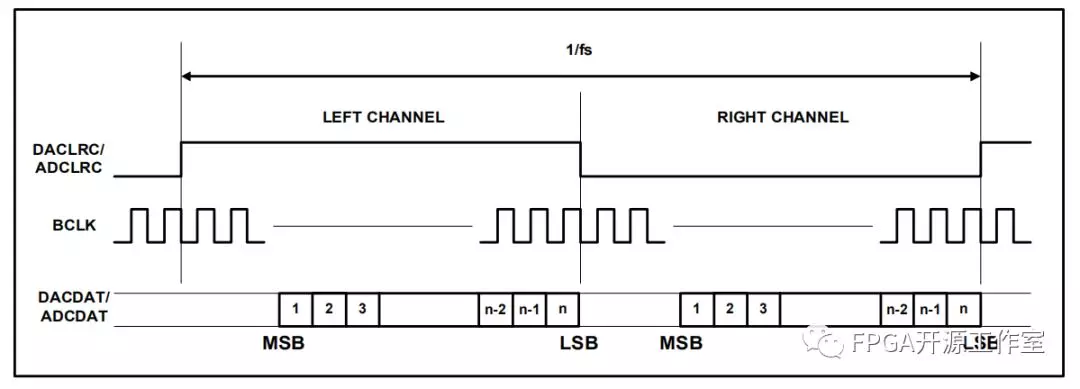

右对齐模式。

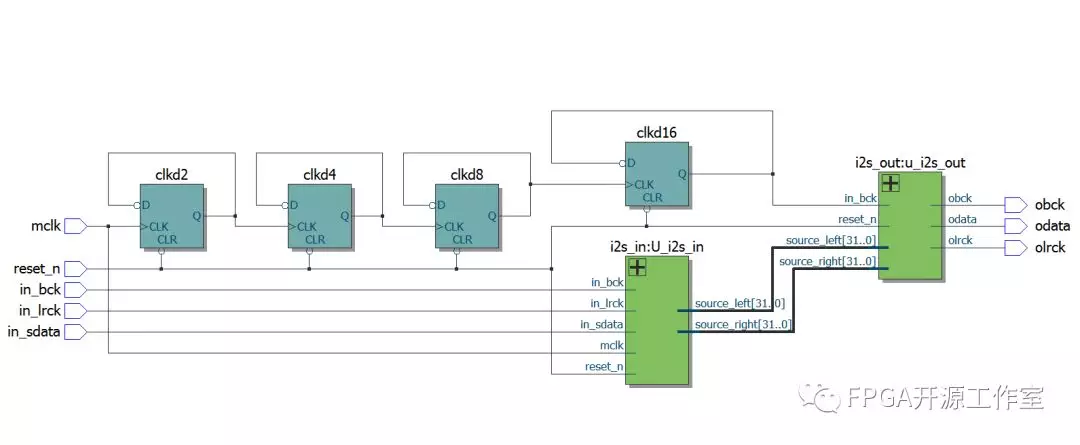

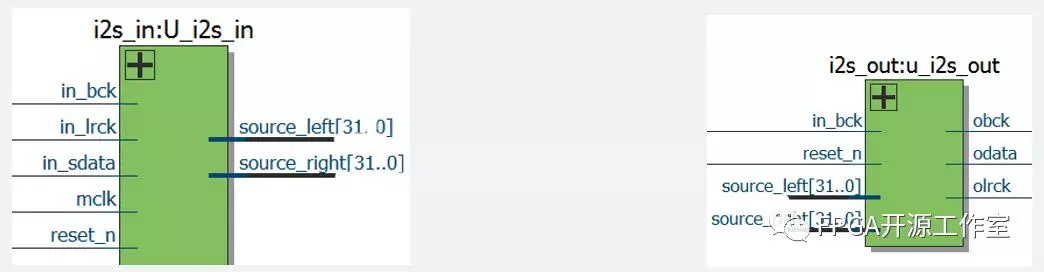

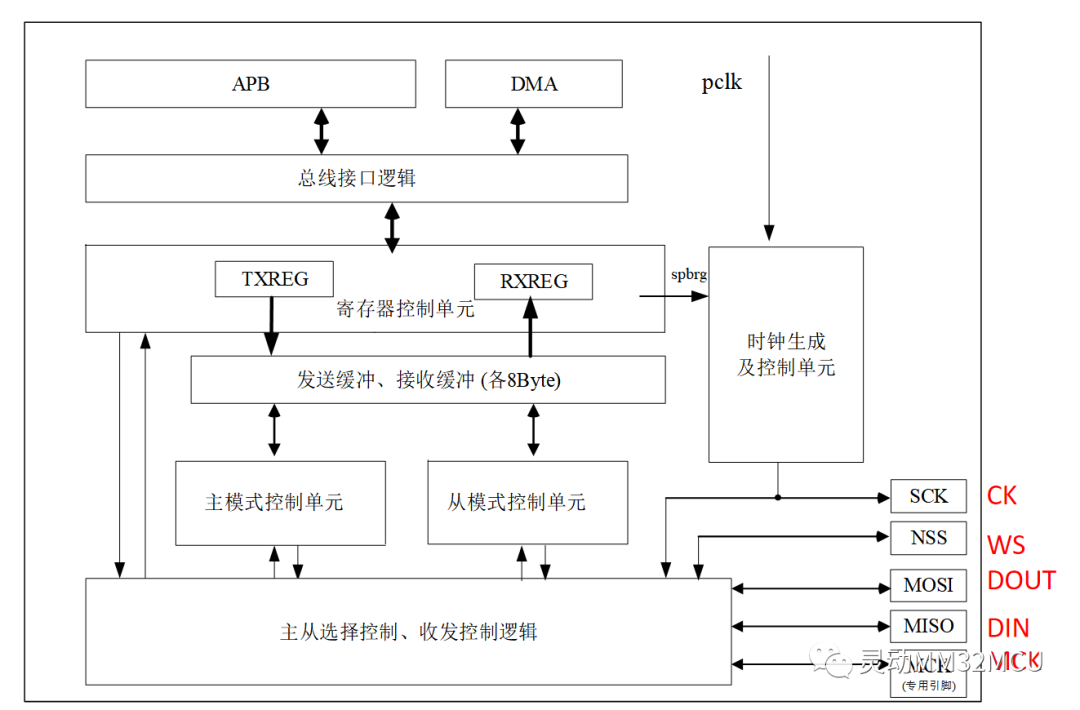

i2s_test模块为i2s_in和i2s_out模块的顶层,i2s_in模块将输入的串行数据转换成并行的数据,然后i2s_out模块将并行数据转换成串行数据输出。

I2s_in模块和I2s_out模块的接口说明如下。

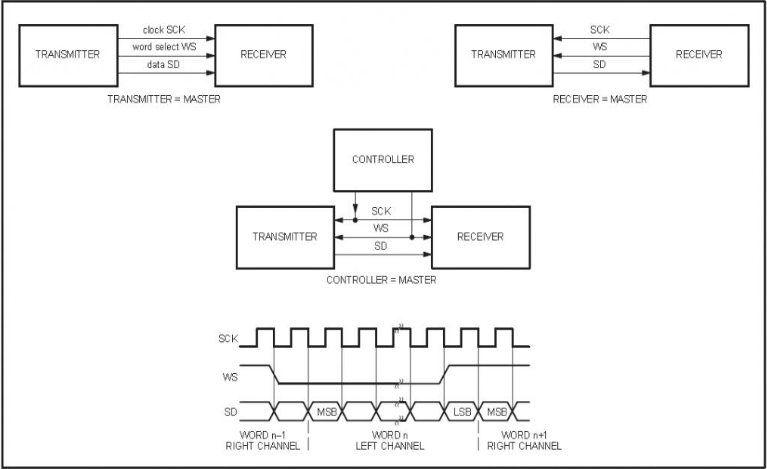

I2s test bench设计

让i2s_out模块将并行转为串行,然后使用i2s_in模块将串行转为并行。验证数据是否正确。

Test bench源码:

1. // test bench

2.

3. `timescale 1ps/1ps

4.

5. module tb32bitmaster();

6.

7. initial begin #600000000 $finish; end //600us

8.

9. reg preset_n;

10. initial begin preset_n = 1; #10000 preset_n = 0; #100000 preset_n = 1; end

11.

12. reg pclk;

13. initial begin pclk = 0; #313333 pclk = 0; forever #11072.1 pclk = ~pclk; end

14.

15. reg start;

16. initial begin start = 0; #400000 start = 1; end

17.

18. reg clkd2, clkd4, clkd8, clkd16;

19. wire reset_n = preset_n;

20.

21. always @(posedge pclk or negedge reset_n)

22. if (0 == reset_n)

23. clkd2

24. else

25. clkd2

26.

27. always @(posedge clkd2 or negedge reset_n)

28. if (0 == reset_n)

29. clkd4

30. else

31. clkd4

32.

33. always @(posedge clkd4 or negedge reset_n)

34. if (0 == reset_n)

35. clkd8

36. else

37. clkd8

38. always @(posedge clkd8 or negedge reset_n)

39. if (0 == reset_n)

40. clkd16

41. else

42. clkd16

43.

44.

45. wire bck, lrck, sdata;

46. wire [31:0] y0, y1;

47.

48. i2s_in U_i2s_in(

49. .mclk(pclk),

50. .reset_n(reset_n),

51.

52. .in_bck(bck),

53. .in_lrck(lrck),

54. .in_sdata(sdata),

55. //controls

56. //output

57. .source_left(y0),

58. .source_right(y1)

59. );

60.

61. i2s_out u_i2s_out(

62. .in_bck(clkd16),

63. .reset_n(reset_n),

64. .source_left(32'h5555_aaaa),

65. .source_right(32'haaaa_5555),

66. .obck(bck),

67. .olrck(lrck),

68. .odata(sdata)

69. );

70. endmodule

71.

72. `include "i2s_out.v"

73. `include "i2s_in.v"

从仿真结果看我们的i2s_out和i2s_in模块仿真设计成功。

编辑:hfy

-

FPGA

+关注

关注

1630文章

21761浏览量

604390 -

I2S

+关注

关注

1文章

65浏览量

41979

发布评论请先 登录

相关推荐

全面解析I2S、TDM、PCM音频总线

音频接口I2S实验

基于FPGA和AD1836的I2S接口设计

I2S设备和MSP430器件的连接指南

i2s音频总线学习

几种常见的I2S数据格式

音频总线I2S协议:I2S收发模块FPGA的仿真设计

音频总线I2S协议:I2S收发模块FPGA的仿真设计

评论