将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。

本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

软件使用Vivado 2018.1。

参考工程:ddr3_test。

第五篇:mig读写时序下板实现

1顶层文件和约束文件

ddr3_test.v

参见参考工程:ddr3_test。

ddr3.xdc

1. set_property PACKAGE_PIN E3 [get_ports clk]

2. set_property IOSTANDARD LVCMOS33 [get_ports clk]

3. set_property PACKAGE_PIN D9 [get_ports reset]

4. set_property PACKAGE_PIN E1 [get_ports init_calib_complete]

5. set_property IOSTANDARD LVCMOS33 [get_ports init_calib_complete]

6. set_property IOSTANDARD LVCMOS33 [get_ports reset]

2 下板实现读写时序

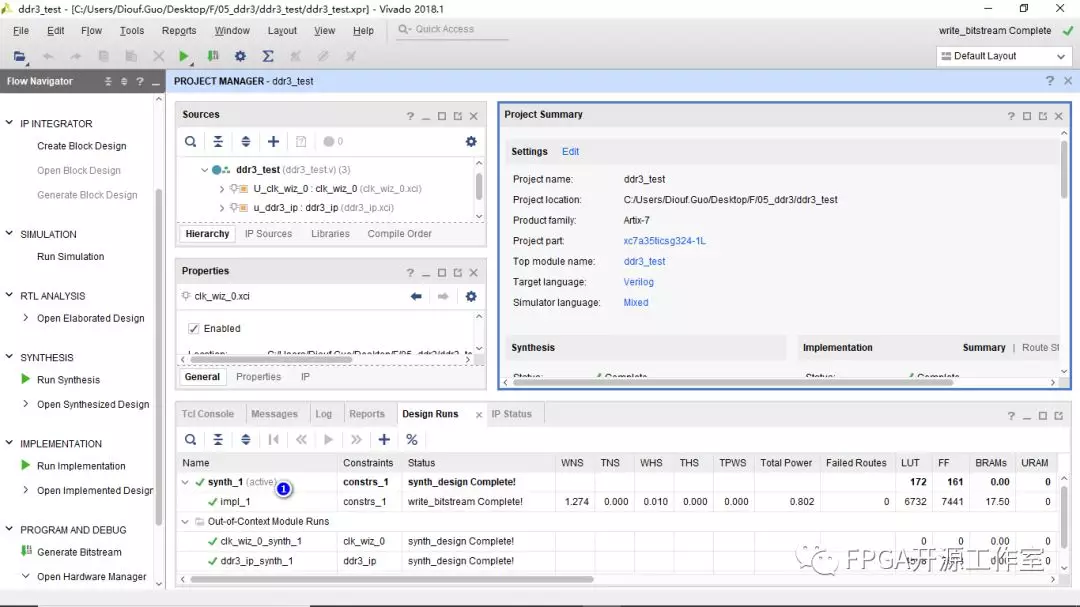

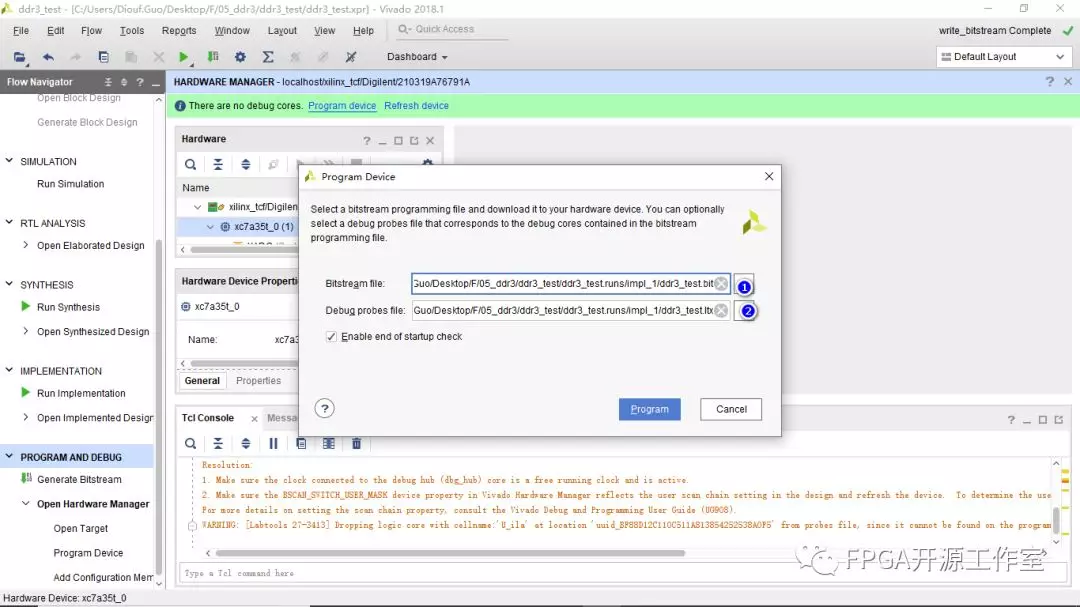

1>①完成综合和实现

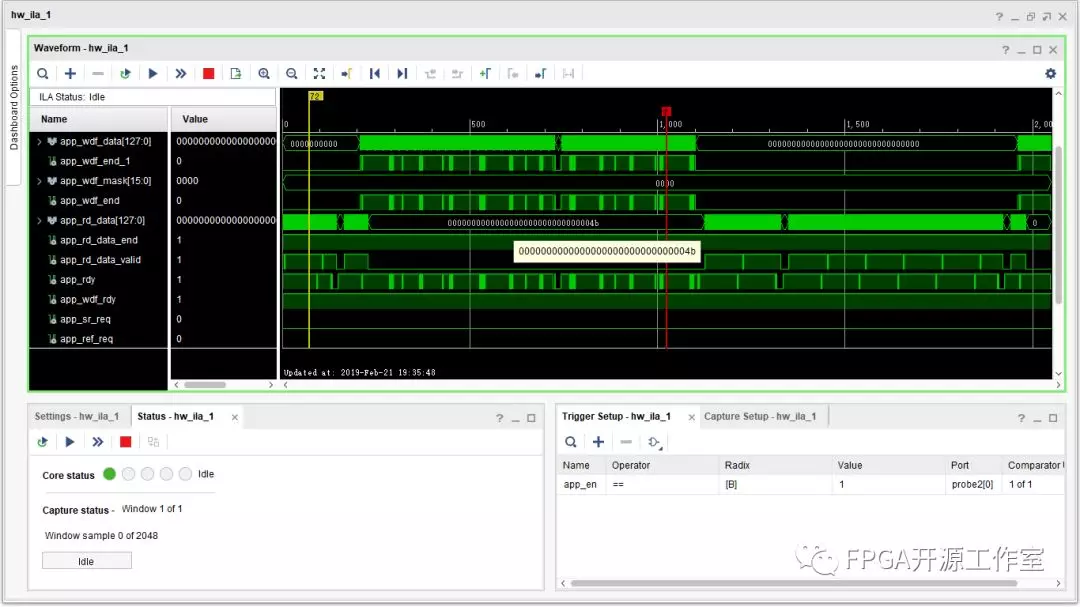

3>下载完成,查看波形。

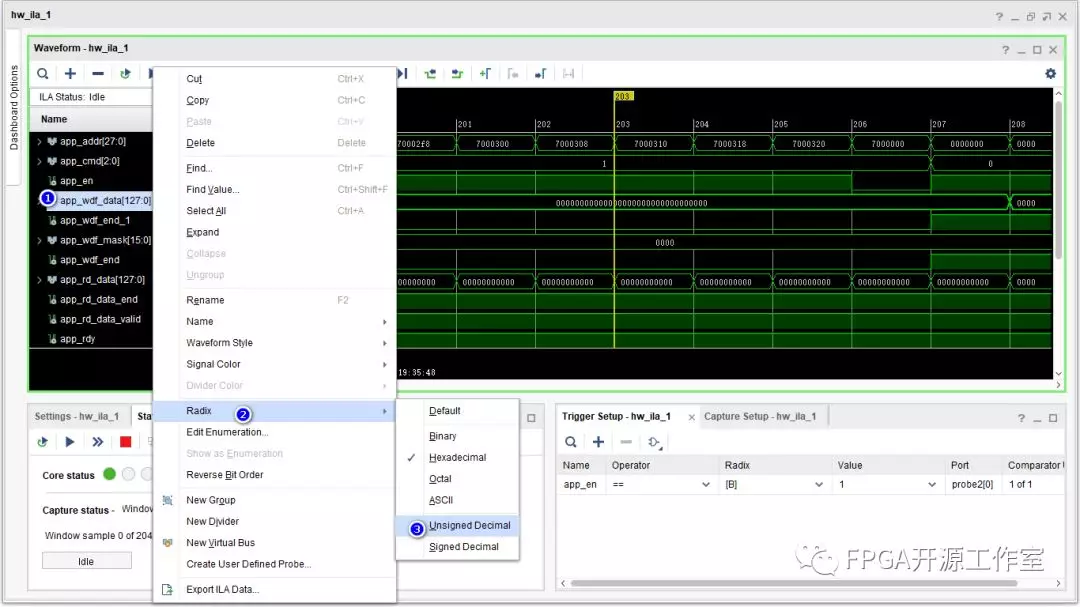

4>将app_wdf_data数据格式改为Unsigned Decimal。

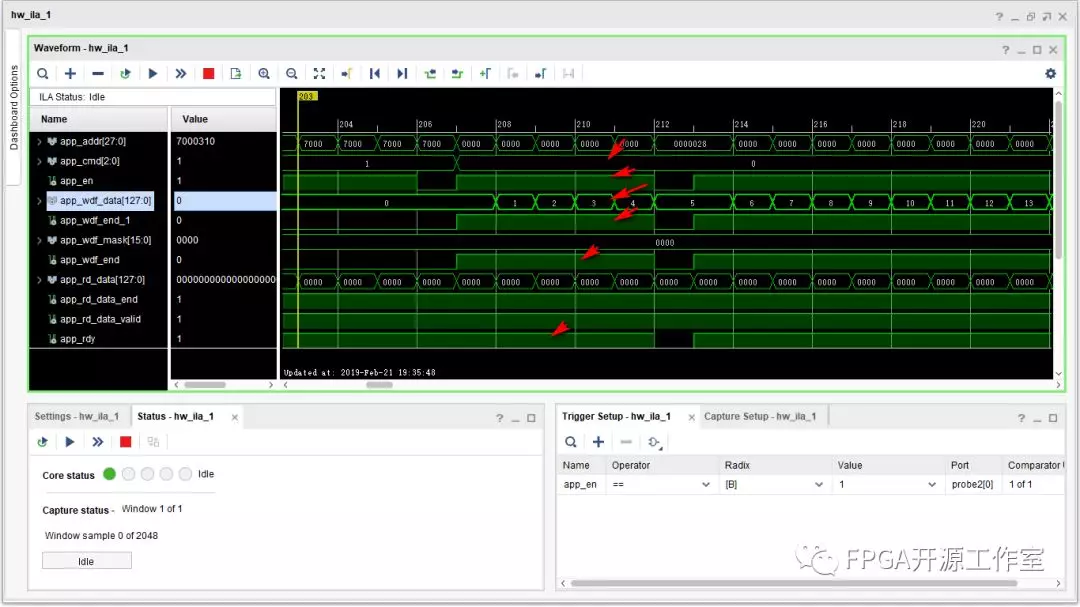

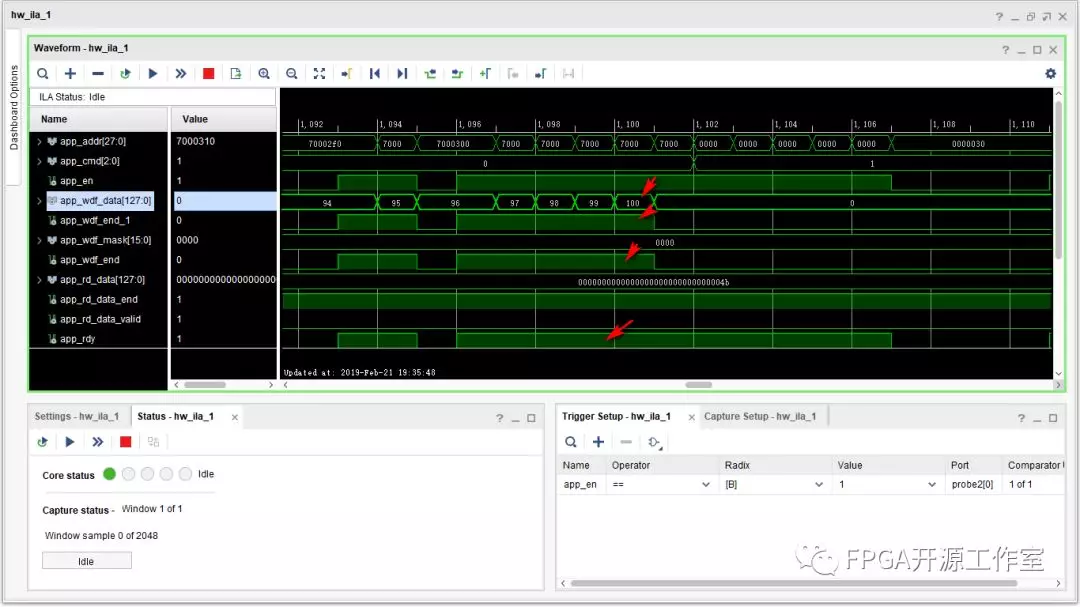

5>查看写时序。

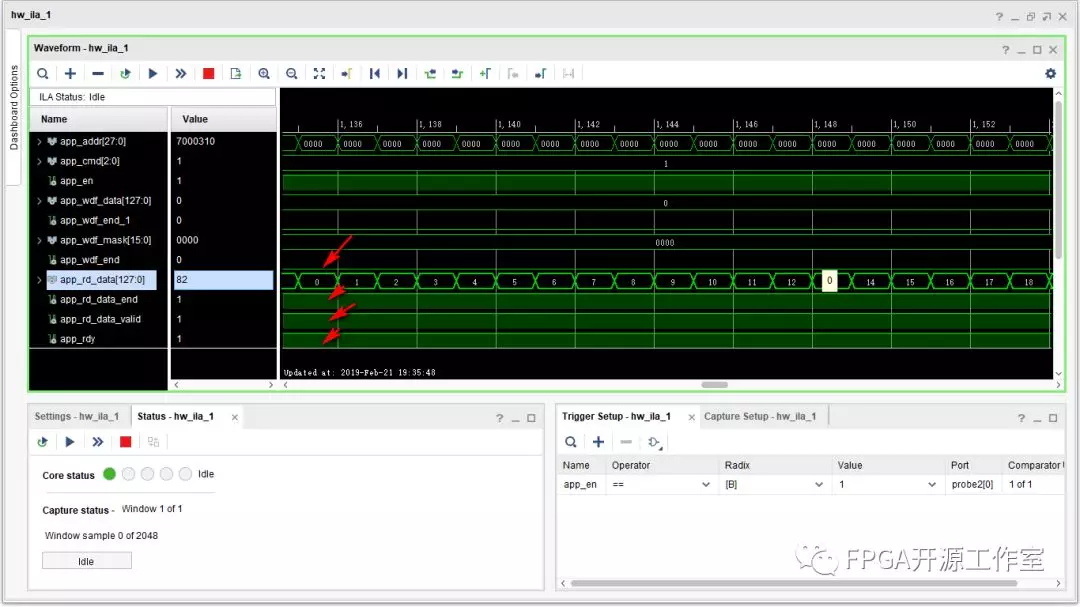

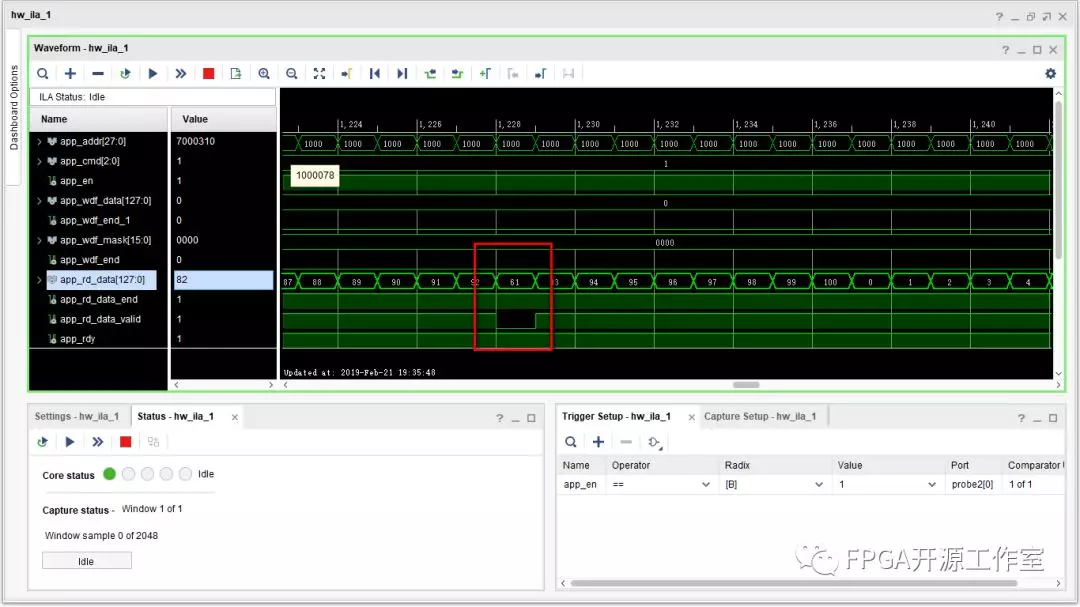

6>查看读时序。

基于xilinx mig ip对ddr3读写验证完成。

编辑:hfy

-

FPGA

+关注

关注

1630文章

21763浏览量

604525 -

DDR3

+关注

关注

2文章

276浏览量

42324

发布评论请先 登录

相关推荐

正点原子fpga开发板不同型号

正点原子和野火开发板哪个好

【米尔-Xilinx XC7A100T FPGA开发板试用】+01.开箱(zmj)

基于FPGA的DDR3多端口读写存储管理设计

国产FPGA核心板!米尔紫光同创Logos-2和Xilinx Artix-7核心板

FPGA核心板 Xilinx Artix-7系列XC7A100T开发平台,米尔FPGA工业开发板

精选推荐!紫光盘古系列FPGA开发板信息汇总

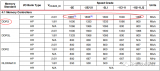

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

fpga开发板是什么?fpga开发板有哪些?

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

基于Digilent的Arty Artix-35T FPGA开发板的DDR3读写控制

基于Digilent的Arty Artix-35T FPGA开发板的DDR3读写控制

评论