讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。

本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

软件使用Vivado 2018.1。

第一篇:DDR3和mig的介绍

1 DDR3介绍

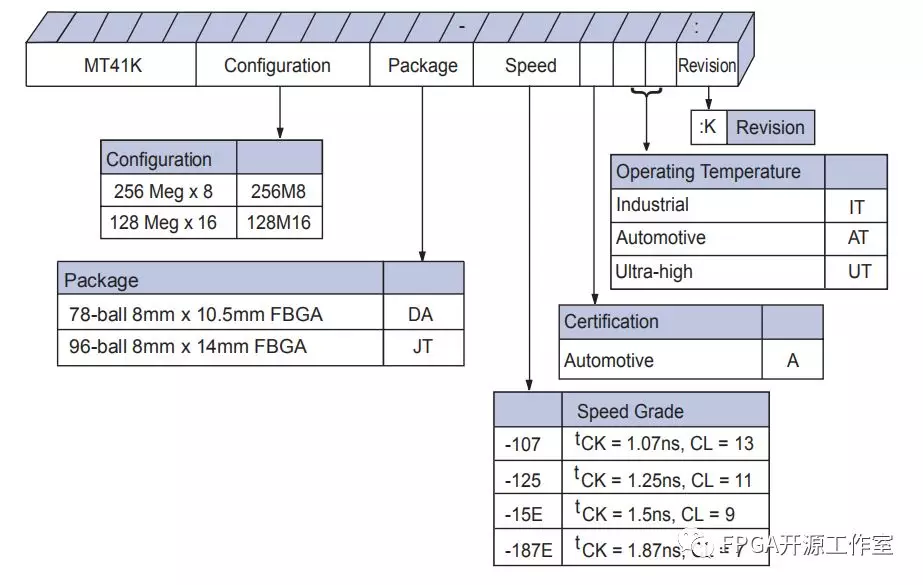

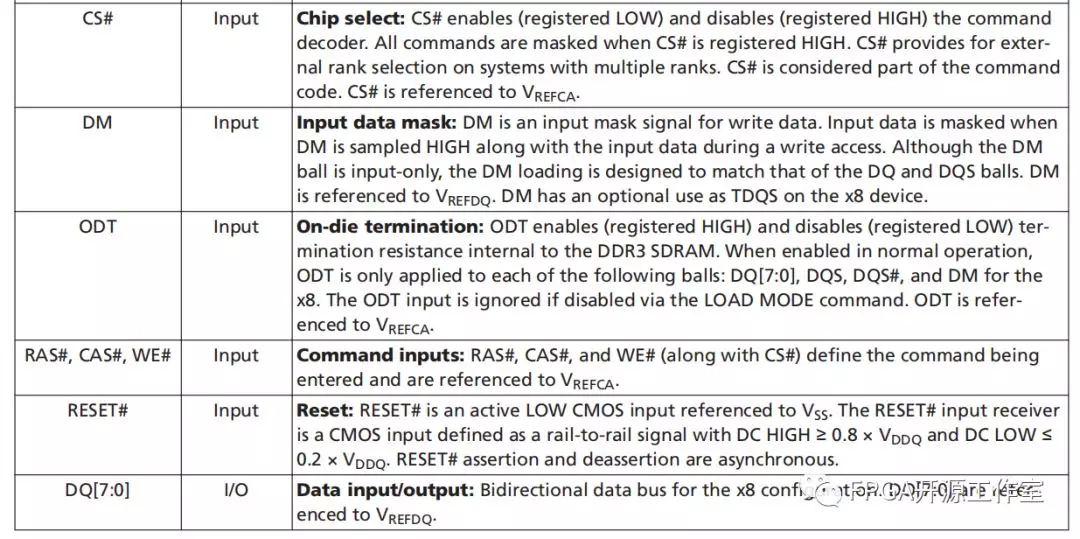

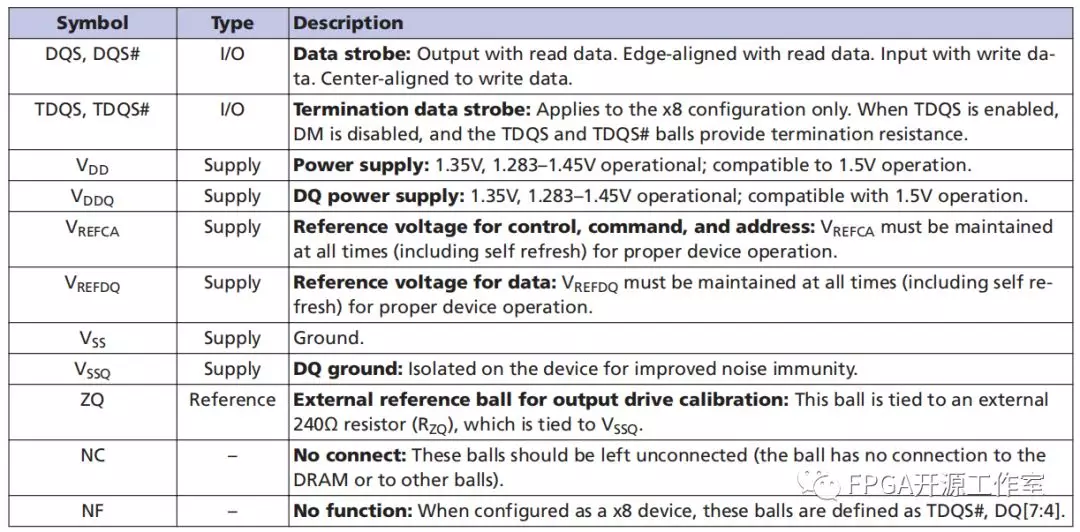

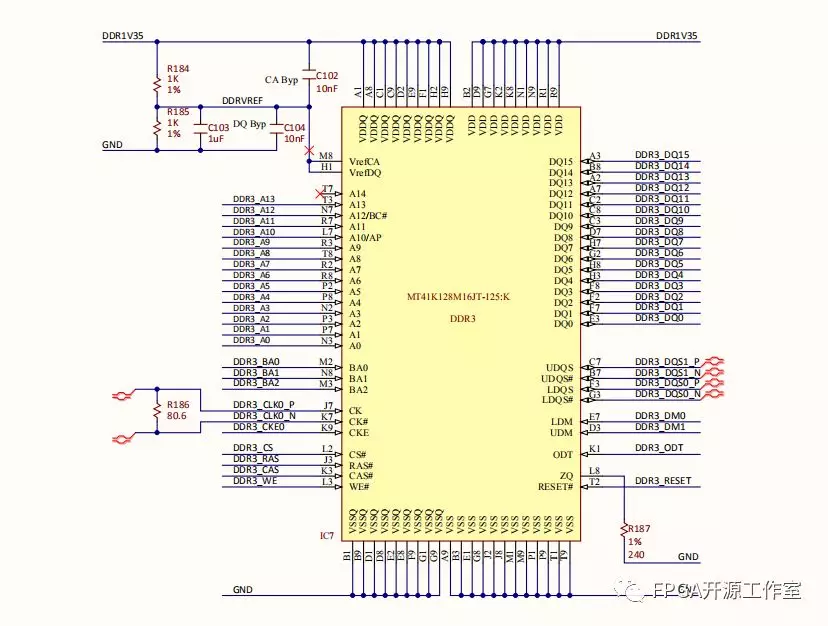

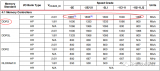

以镁光的MT41K128M16为例来介绍DDR3。

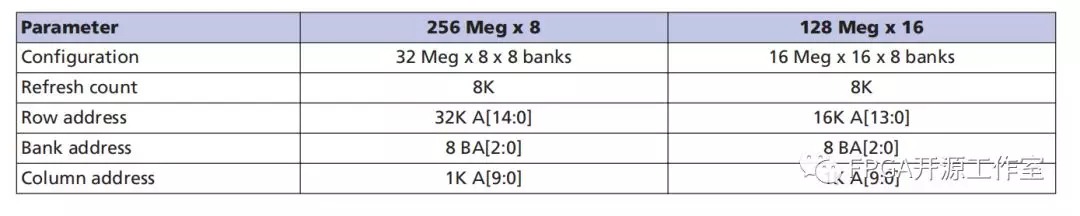

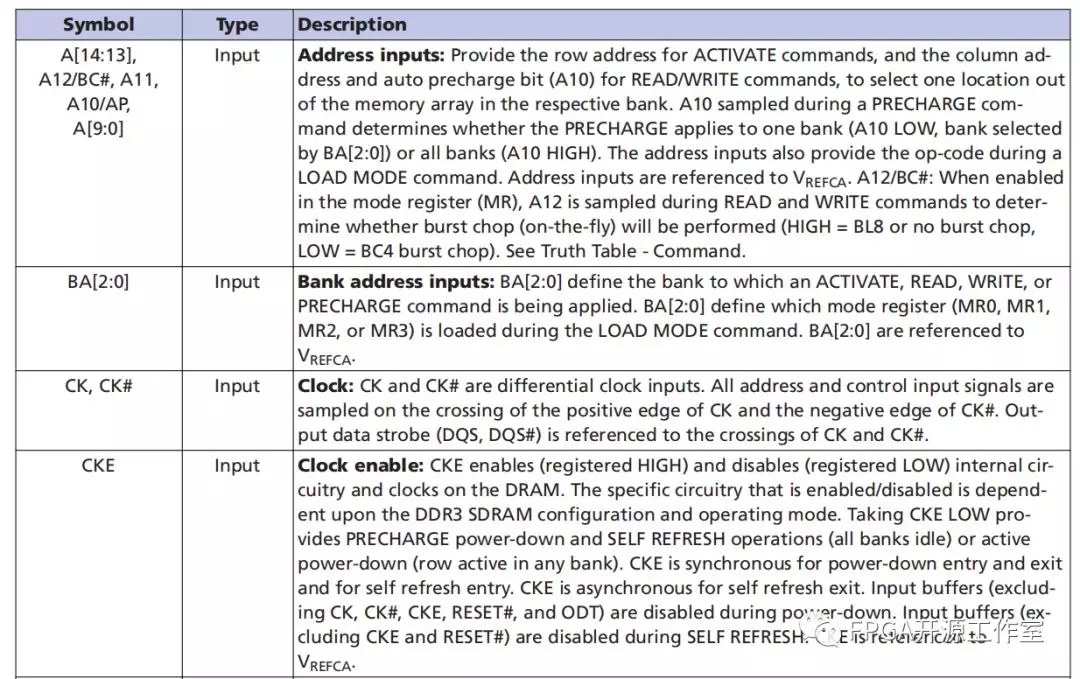

通过以上信息我们即可知道DDR3的内存容量,Row,Column和Bank的地址位宽。开发板选用的MT41K128M16 DDR3的容量为16Megx16x8banks=2048Mb=2Gb。

1.1 DDR3命名

使用xilinx mig IP来控制DDR3的数据读写我们了解DDR3以上信息即可。

2 mig介绍

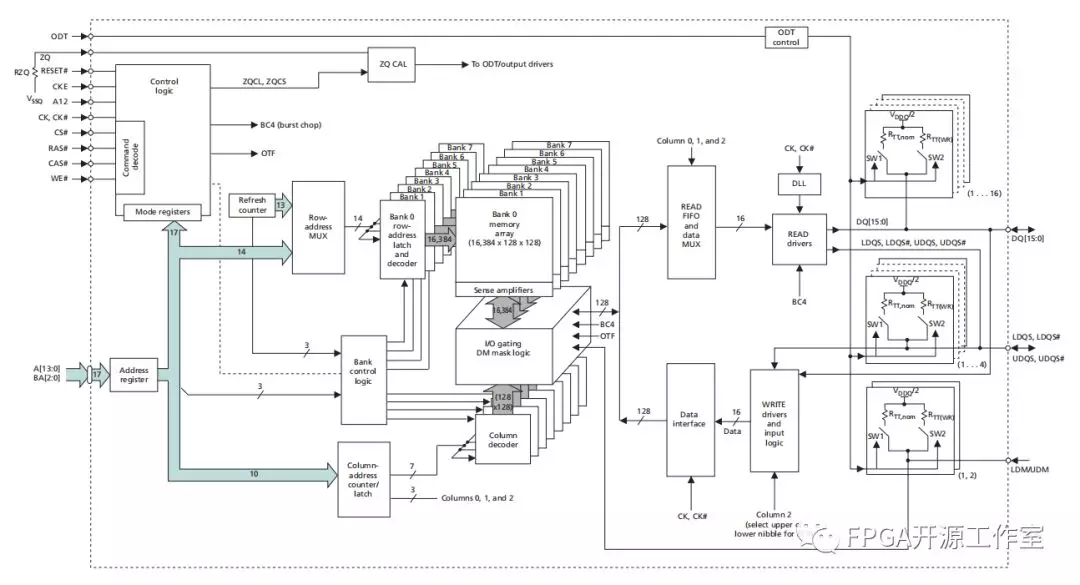

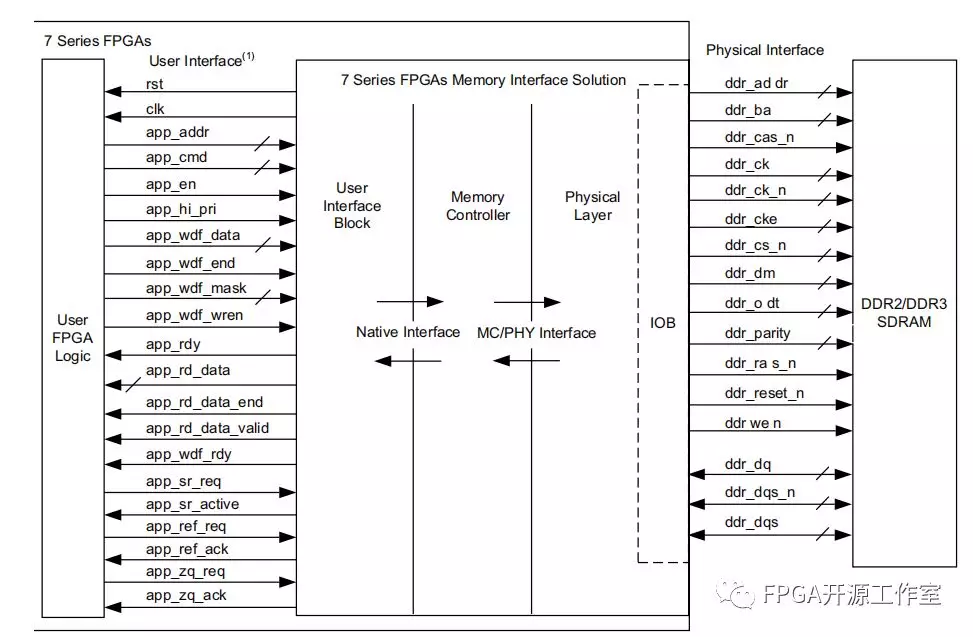

如上图所示,mig(Memory Interface Solution) IP由三部分组成User Interface Block,Memory Controller和Physical Layer。IP的一边是连接DDR3的接口(Physical Interface),另一边是用户逻辑控制接口(User FPGA Logic)。想要正确的控制DDR3的读写,我们需要正确的设置mig IP和正确的用户逻辑控制接口逻辑。

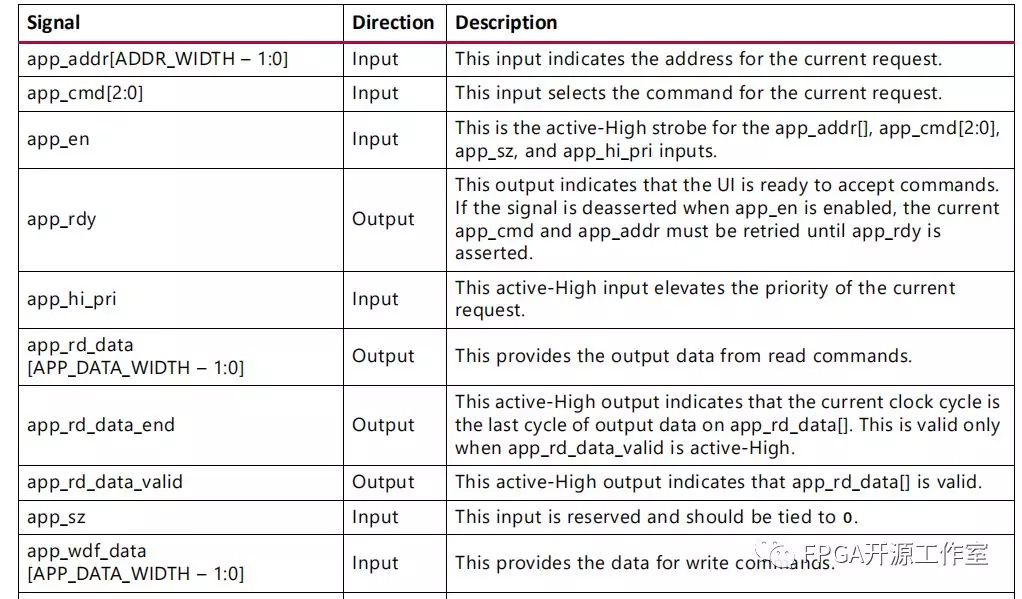

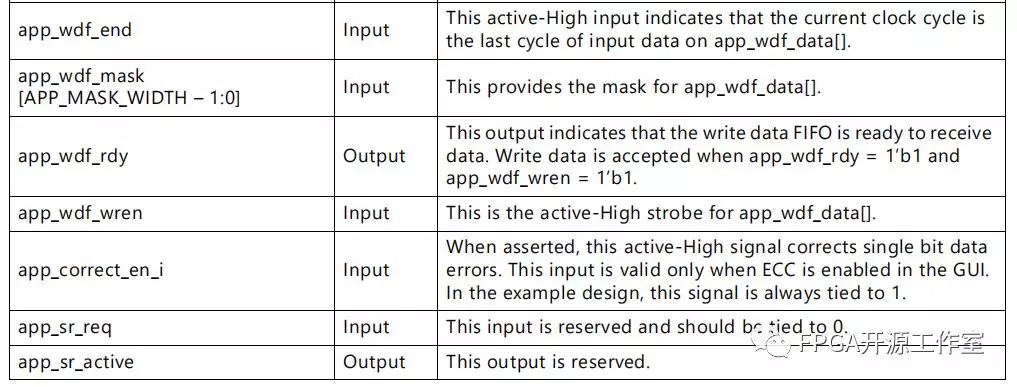

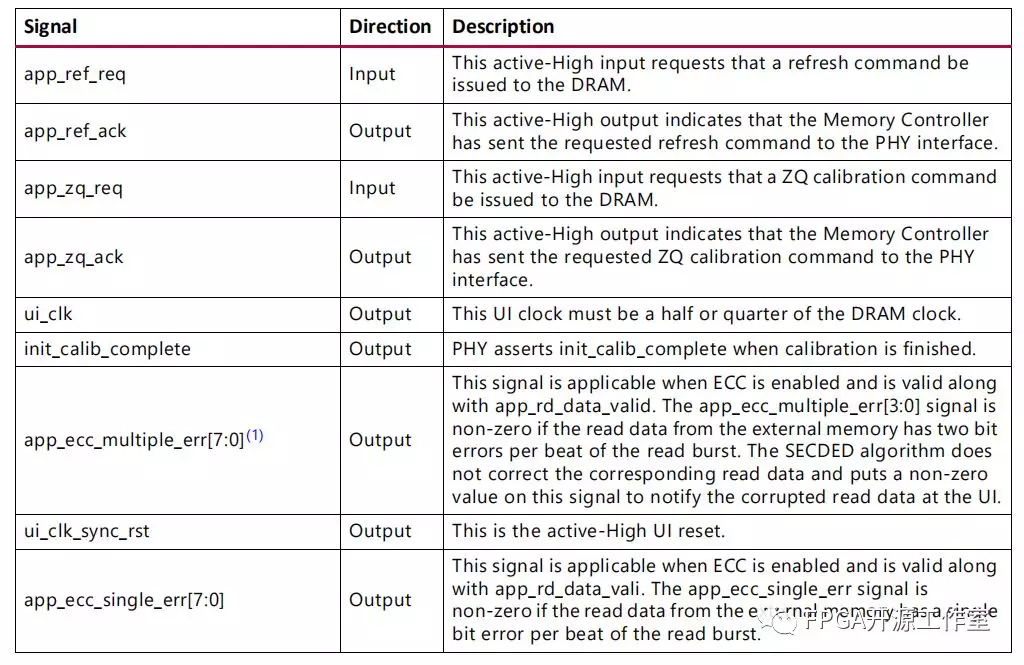

2.1 mig user interface

对于mig用户端接口含义我们将在《第三篇--mig IP用户逻辑接口读写时序分析》中详细介绍。

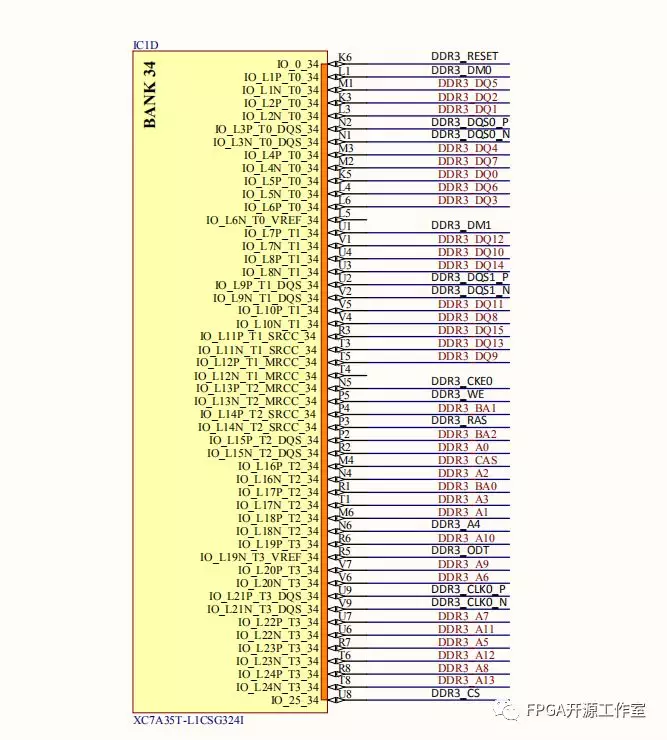

3 DDR3原理图和FPGA原理图

-

FPGA

+关注

关注

1629文章

21729浏览量

603011 -

DDR3

+关注

关注

2文章

276浏览量

42244 -

开发板

+关注

关注

25文章

5032浏览量

97375

发布评论请先 登录

相关推荐

【米尔-Xilinx XC7A100T FPGA开发板试用】测试一

如何选择DDR内存条 DDR3与DDR4内存区别

正点原子和野火开发板哪个好

【米尔-Xilinx XC7A100T FPGA开发板试用】+01.开箱(zmj)

基于FPGA的DDR3多端口读写存储管理设计

国产FPGA核心板!米尔紫光同创Logos-2和Xilinx Artix-7核心板

FPGA核心板 Xilinx Artix-7系列XC7A100T开发平台,米尔FPGA工业开发板

G2D图像处理硬件调用和测试-基于米尔-全志T113-i开发板

基于Arty Artix-35T FPGA开发板的DDR3和mig介绍

基于Arty Artix-35T FPGA开发板的DDR3和mig介绍

评论