如何存储关键数据的方法,属于规模测试验证的手段,但对于Verilog的调试过程还不够直观,因为无法确切地了解Verilog代码仿真中各个关联信号是如何作用的。Verilog的确可以像C/C++一样启动调试模式,针对每行代码进行调试。但请注意,由于Verilog是并行执行的,而仿真是采用delta时间逐步并行推进的,采用代码调试较为困难,所以常常需要存储全部或部分仿真数据,这就是波形文件。

在进行FPGA开发的过程中,稍微大一点的项目,进行一次编译综合与布线是非常耗时的,所以在开发的过程中一般采取先进行功能仿真,功能仿真结果正确无误以后再进行综合和布局布线。一般来说,先添加好时钟约束,进行综合与布线时无严重警告,此时如果功能仿真(前仿)仍然正确,那么任务就基本完成了。但如果是一个比较完整的项目开发,应该还需要进行布线后的时延仿真(后仿)。这里,主要介绍如何将前仿和后仿的时序波形图保存以及再次打开上一次的仿真结果。

相关文件说明

1. 波形数据库文件(.WDB),其中包含所有的仿真数据。

2. 波形配置文件(.WCFG),其中包含于波形配置文件中的对象相关联的顺序和设置

在保存 .WCFG文件之前,对波形配置的修改(包括创建波形配置或添加HDL对象)不是永久性的,可以通过 File -> Save Waveform Configuration As 将波形配置保存下来。波形数据库文件(.WDB)包含了波形配置文件中所有信号的仿真数据,单个 .WDB可以对应多个 .WCFG文件, 可以通过打开 .WDB文件查看上一次保存下来的仿真波形。

具体的保存与读取

保存

1. 将需要观测的信号拉倒图形窗口界面

2. 设置仿真时间

3. 保存 .WCFG 波形配置文件到指定路径

4. 保存 .WDB 仿真波形。为了能将波形数据保存下来,需要在测试代码中加上如下代码,放在最末端即可。为了下一次仿真不影响已保存的仿真波形,建议将 .WDB 文件拷贝并修改名字。

`define dump_level 10

//module dump_task;

initial begin#1; //延迟1ns记录,方便与其他仿真动作协调

`ifdef VCS_DUMP //Synopsys VCD+格式存储

$display("Start Recording Waveform in VPD format!");

$vcdpluson();

$vcdplustraceon;

`endif

`ifdef FSDB_DUMP //Synopsys fsdb格式存储

$display("Start Recording Waveform in FSDB format!");

$fsdbDumpfile("dump.fsdb");

$fsdbDumpvars('dump_level);

`endif

`ifdef NC_DUMP//cadence 格式存储

$recordsetup("dump","version=1","run=1","directory=.");

$recordvars("depth=6");

`endif

`ifdef VCD_DUMP//工业标准VCD格式存储

$display("Start Recording Waveform in VCD format!");

$dumpfile("dump.vcd");

$dumpvars('dump_level);

`endif

end

5. 运行仿真(前后仿的 .WDB 会自动保存到 .sim/sim_1/ 下的三个路径之一,与仿真类型有关)。

读取

1. 点击Vivado的菜单栏中的 Flow -> Open Static simulation,然后选中之前保存的 .WDB 文件即可。

2. 点击Vivado的菜单栏中的 File -> Open Waveform Configuration,选择我们之前保存的 .WCFG文件即可恢复上一次的仿真结果

总结

时序仿真波形的保存与读取在大工程的功能仿真、时序仿真、以及问题分析中,可以为开发者节约很多时间。当一个项目比较复杂时,跑一次仿真耗时会非常长,尤其是需要进行后仿时,耗时比综合和布局布线更长,所以我们最好是将时序波形保存下来进行分析,可以避免浪费许多不必要的时间。

-

FPGA

+关注

关注

1631文章

21806浏览量

606691 -

Vivado

+关注

关注

19文章

815浏览量

66960 -

时序仿真

+关注

关注

0文章

14浏览量

7466

发布评论请先 登录

相关推荐

ADS1263工作时序与手册不一致怎么解决?

正点原子fpga开发指南

Vivado使用小技巧

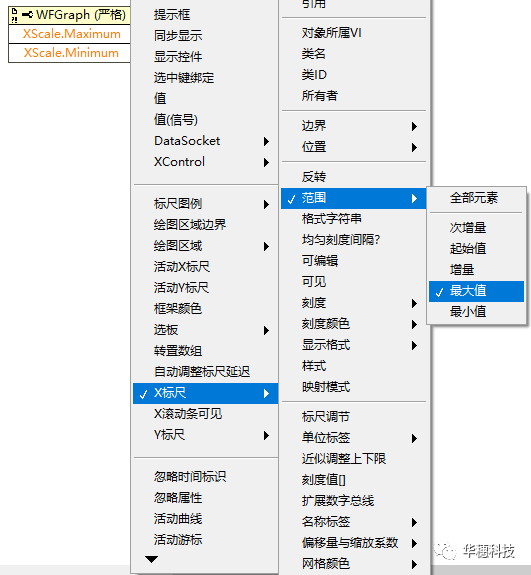

LabVIEW波形图截取局部数据

三菱PLC数据怎么读取与保存

FPGA 高级设计:时序分析和收敛

示波器如何保存波形数据?

示波器如何直连电脑进行波形读取

ADXL345读取id失败的原因?

泰克示波器保存波形csv

深入探索Vivado非工程模式FPGA设计流程

FPGA开发:Vivado时序波形图保存和读取

FPGA开发:Vivado时序波形图保存和读取

评论