本篇主要介绍PCIe总线的AC耦合电容、总线的去加重等高速信号调整技术。

AC耦合电容可以参考之前的文章《逻辑电平之差分互连AC耦合电容(7)》,本文主要针对PCIe接口介绍AC耦合电容的实际使用。

信号调整相关资料可以参考之前的文章《高速信号调整技术》,本文主要针对PCIe介绍其使用的具体的调整技术。

1、AC耦合电容

一般使用AC耦合电容是为了提供直流偏压。直流偏压就是滤除信号的直流分量,使信号关于0轴对称。

从这个作用看,其实理想电容应该可以放在通道的任何一个地方。但实际电路中的电容并非理想的,有寄生电感的存在,而且焊盘和换层过孔都是阻抗不连续点。

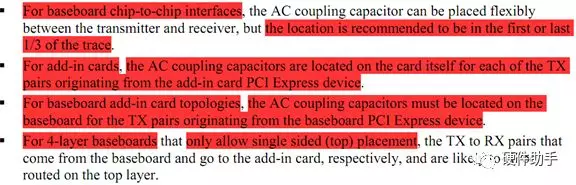

那为什么PCIe要求放在发送端呢?其实仔细看PCIe规范是说如果是两块板连接时,要放在发送的那块板上。如果发送接收在同一块板上,那么就随意吧,但最好靠近一端。

下面是从PCIe 3.0规范中摘取出来的截图,可以清晰的看到对AC耦合电容位置的准确描述!

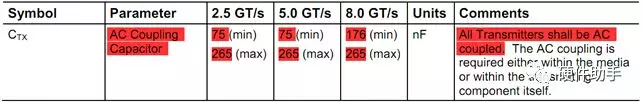

PCIe总线还规定了耦合电容的大小范围,详细参见规范中的表4-18,摘取如下:

PCIe协议规定的AC耦合电容规范

All platforms that have transmitters supporting 8.0 GT/s must implement the 176-265nF CTX value. Platforms operating at 2.5 or 5.0 GT/s only may implement over arange of 75 to 265 nF. (如果是PCIe 3.0则AC耦合电容必须选择大一些!!!这就是为什么大部分时候我们看到参考设计中的AC耦合电容都选择0.1uF,而有时候会遇到有的设计的耦合电容不是0.1uF,而是0.22uF之类的值,对此不要感到惊讶。)

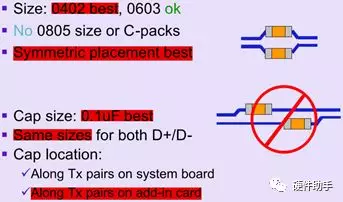

针对AC耦合电容,PCB布局布线一定要讲求对称!!!

2、高速信号调整

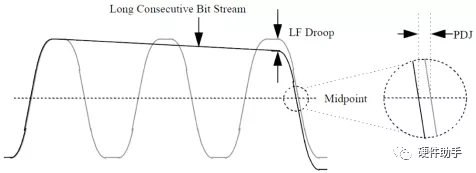

由于PCIe的速率越来越高,而普通的PCB板材和接插件对信号的传输损耗较严重,因此PCIe G1和G2在发送端都采用了去加重技术(De-emphasis),即发送端在发送信号时对跳变位之后的信号(代表信号中的低频成分)减小幅度发送,这样可以部分补偿一下传输线路对高频成分的衰减,从而得到比较好的眼图(信号摆幅小,眼图高度低,功耗小,EMC辐射小)。

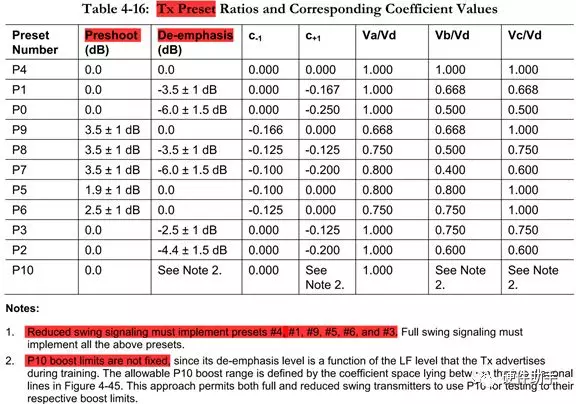

PCIe G1中采用的是-3.5dB的去加重,G2中采用的是-3.5dB和-6dB的去加重。对于G3,由于信号速率更高,需要采用更加复杂的二阶去加重技术,即除了跳变位减小幅度(De-emphasis)发送外,在跳变位的前一位也要增大幅度发送,这个增大的幅度通常叫做Preshoot。

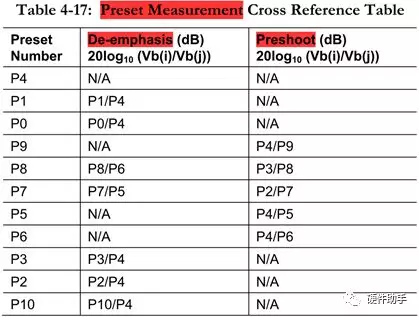

为了应对复杂的链路环境,PCIe G3中规定了共11种不同的Preshoot和De-emphasis的组合(Preset),实际应用中Tx和Rx端可以在Link Training阶段协商出一个最优的Preset值。

PCIe G3除了在发送端对信号高频进行补偿,在接收端还要对信号做均衡(Equalization),就是在Rx端的接收芯片内增加一个均衡电路,可以抬高接收到的信号中的高频分量,从而对线路的损耗进行进一步的补偿。均衡器的强弱也有很多档可选,在Link Training阶段Tx和Rx端会协商出一个最佳的组合。

编辑:hfy

-

AC

+关注

关注

1文章

588浏览量

84346 -

PCIe

+关注

关注

15文章

1234浏览量

82579 -

耦合电容

+关注

关注

2文章

154浏览量

19811

发布评论请先 登录

相关推荐

别忽视!高速电路可能毁于未优化的AC耦合电容

AC耦合电容的选取

完成闭环设计,基于仿真软件的AC耦合电容阻抗优化

ViaExpert仿真AC耦合电容阻抗优化设计方案解析

PCIe总线AC耦合及高速信号调整技术

PCIe总线AC耦合及高速信号调整技术

评论