在goggle上搜zcu102 pynq可以找到一些移植方法的信息

0. Prebuilt

PYNQ移植ZCU102编译好的固件

1. 生成镜像

git clone

$ git clone https://github.com/Xilinx/PYNQ.git

$ cd PYNQ

$ git checkout v2.3

$ git checkout -b vacajk_dev

检查依赖环境,qemu,crosstool-ng

$ cd sdbuild/scripts

$ ./setup_host.sh

$ source /opt/pkg/petalinux/settings.sh

$ source /opt/Xilinx/Vivado/2018.2/settings64.sh

$ cd ../../

拷贝ZCU104的配置作为ZCU102来使用,删除不用的ZCU104petalinux配置

$ cp -rf ./boards/ZCU104 ./boards/ZCU102

$ rm -rf ./boards/ZCU102/petalinux_bsp/

$ mv ./boards/ZCU104/ZCU104.spec ./boards/ZCU102/ZCU102.spec

$ gedit ./boards/ZCU102/ZCU102.spec

修改ZCU102.spec的内容

ARCH_ZCU102 := aarch64

BSP_ZCU102 := xilinx-zcu102-v2018.2-final.bsp

STAGE4_PACKAGES_ZCU102 := ethernet

从官网上下载xilinx-zcu102-v2018.2-final.bsp,复制到./boards/ZCU102目录下从github下载的脚本能够完整的生成img文件,并会自动将所有的环境搭建完毕,但是速度很慢,看了PYNQ的官网发现能够直接下载编译好的rootfs

这样仅仅编译BOOT.bin和只包含kernel的image.ub就可以了。

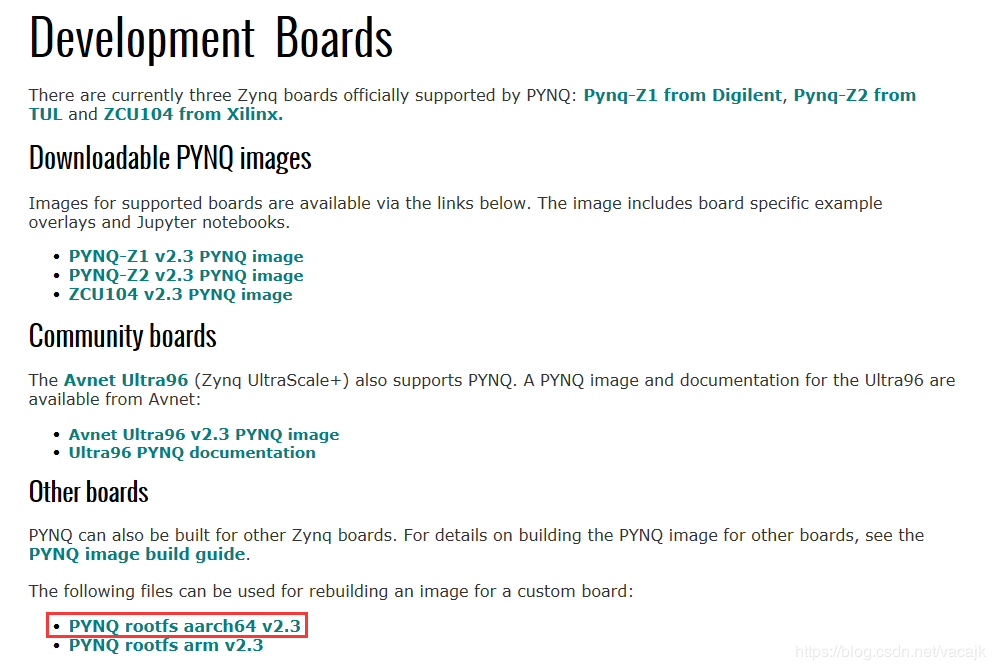

网上下载的rootfs

如果准备使用下载的rootfs,在这里下载rootfs的镜像

http://www.pynq.io/board.html

https://www.xilinx.com/member/forms/download/xef.html?filename=pynq_root...

解压后把bionic.aarch64.2.3.img复制到./sdbuild/prebuilt下

如下指令:

$ make boot_files BOARDS=ZCU102

$ make images BOARDS=ZCU102 PREBUILT=./prebuilt/bionic.aarch64.2.3.img

自行生成的rootfs

如果准备自行编译rootfs,如下指令。比较花时间且网速影响较大

$ make BOARDS=ZCU102

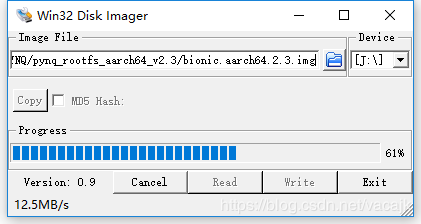

2. 烧写镜像

生成的img文件在./sdbuild/output/ZCU102-2.3.img

使用Win32_Disk_Imager将img烧写到SD卡中

在linux上可以查看SD卡分区及内容,可以看到包含一个FAT32分区用于存放BOOT.bin和image.ub

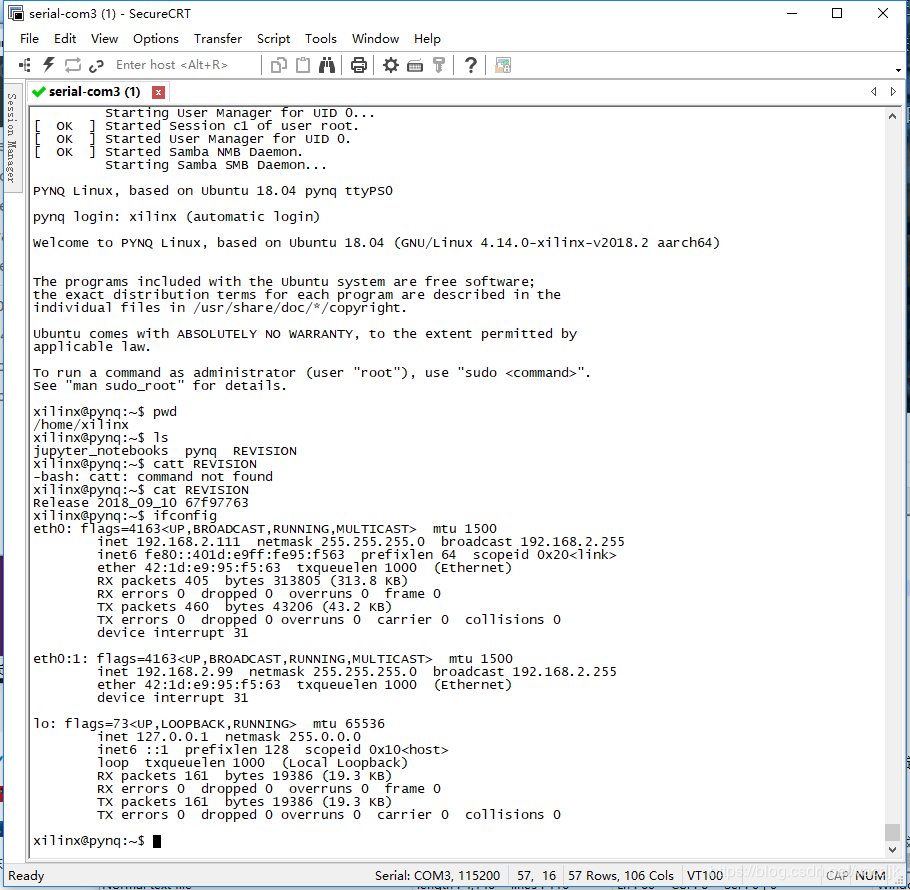

第二个分区是文件系统,ubunttu 18.04尝试启动,使用串口可以看到能够正常登陆

3. 自定义FPGA固件

因为使用的是bsp中的FPGA固件,里面的逻辑外设可能不符合要求,下面重新编辑FPGA固件,测试板上的LED和DIP SWITCH

编辑Vivado工程

使用vivado 2018.2打开xilinx-zcu102-v2018.2-final.bsp中的vivado工程

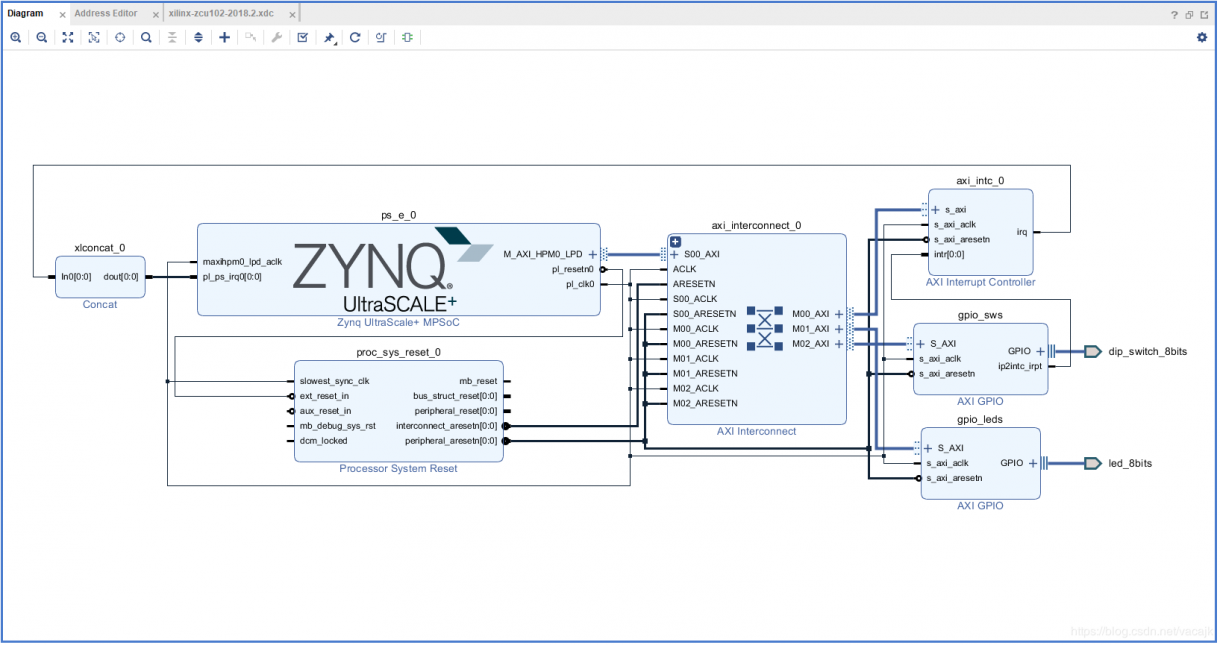

增加两个AXI_GPIO模块,分别用于测试led和switch,添加几个其他ip用于整体系统组成

在xdc中添加IO管脚约束。

set_property PACKAGE_PIN AG14 [get_ports {led_8bits_tri_o[0]}]

set_property PACKAGE_PIN AF13 [get_ports {led_8bits_tri_o[1]}]

set_property PACKAGE_PIN AE13 [get_ports {led_8bits_tri_o[2]}]

set_property PACKAGE_PIN AJ14 [get_ports {led_8bits_tri_o[3]}]

set_property PACKAGE_PIN AJ15 [get_ports {led_8bits_tri_o[4]}]

set_property PACKAGE_PIN AH13 [get_ports {led_8bits_tri_o[5]}]

set_property PACKAGE_PIN AH14 [get_ports {led_8bits_tri_o[6]}]

set_property PACKAGE_PIN AL12 [get_ports {led_8bits_tri_o[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_8bits_tri_o[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_8bits_tri_o[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_8bits_tri_o[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_8bits_tri_o[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_8bits_tri_o[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_8bits_tri_o[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_8bits_tri_o[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_8bits_tri_o[7]}]

set_property PACKAGE_PIN AN14 [get_ports {dip_switch_8bits_tri_i[0]}]

set_property PACKAGE_PIN AP14 [get_ports {dip_switch_8bits_tri_i[1]}]

set_property PACKAGE_PIN AM14 [get_ports {dip_switch_8bits_tri_i[2]}]

set_property PACKAGE_PIN AN13 [get_ports {dip_switch_8bits_tri_i[3]}]

set_property PACKAGE_PIN AN12 [get_ports {dip_switch_8bits_tri_i[4]}]

set_property PACKAGE_PIN AP12 [get_ports {dip_switch_8bits_tri_i[5]}]

set_property PACKAGE_PIN AL13 [get_ports {dip_switch_8bits_tri_i[6]}]

set_property PACKAGE_PIN AK13 [get_ports {dip_switch_8bits_tri_i[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {dip_switch_8bits_tri_i[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {dip_switch_8bits_tri_i[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {dip_switch_8bits_tri_i[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {dip_switch_8bits_tri_i[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {dip_switch_8bits_tri_i[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {dip_switch_8bits_tri_i[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {dip_switch_8bits_tri_i[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {dip_switch_8bits_tri_i[7]}]

Create HDL Wrapper,注意zcu102_wrapper.v的内容是否正常,我是删除了原有的,然后重新生成的。编译并生成bitstream

完成后使用Export Block Design将bd的tcl生成文件输出。

拷贝并重命名刚生成的bit和tcl文件,并重命名为:

zcu102_led.bit和zcu102_led.tcl

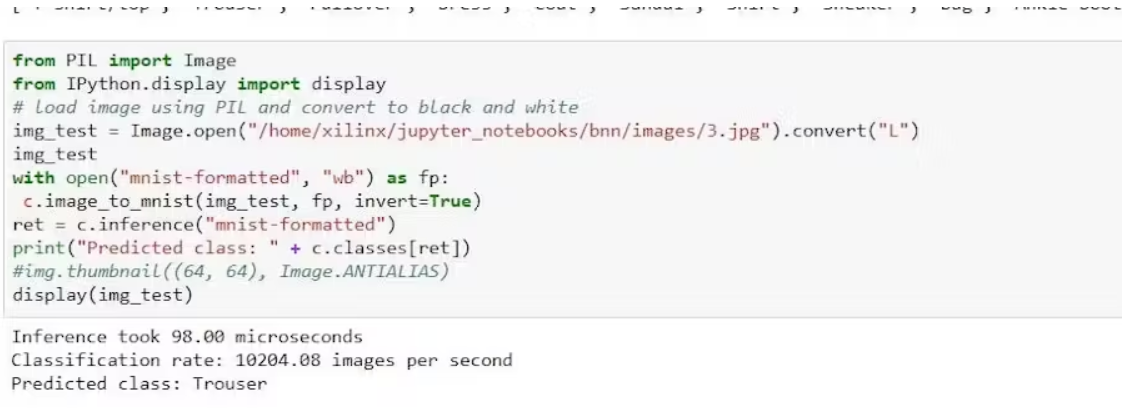

使用PYTHON测试LED和DIP

使用tftp将刚才的两个文件复制到板上的目录中:/home/xilinx/zcu102_test/

$ cd ~/zcu102_test/

$ sudo python3

Python 3.6.5 (default, Apr 1 2018, 05:46:30)

[GCC 7.3.0] on linux

Type "help", "copyright", "credits" or "license" for more information.

>>> from pynq import Overlay

>>> ol = Overlay('zcu102_led.bit')

>>> leds = ol.gpio_leds.channel1

>>> leds[0:8].on()

>>> leds[0:8].off()

>>> sws = ol.gpio_sws.channel1

>>> sws.read()

170

>>> sws.read()

85

如上即可使用python测试led和dip switch

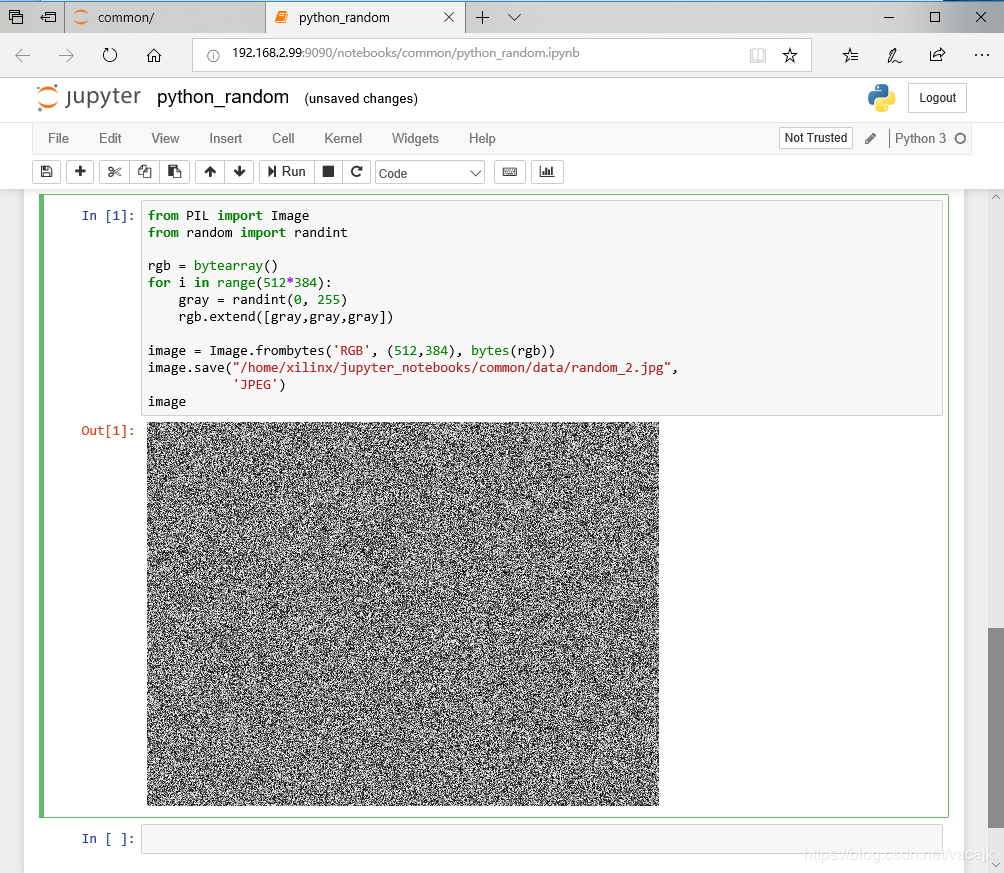

使用jupyter-notebook来进行测试:

import time

from pynq import Overlay

ol = Overlay("./bit/zcu102_led.bit")

leds = ol.gpio_leds.channel1

sws = ol.gpio_sws.channel1

for i in range(256):

leds.write(mask=255, val=i)

time.sleep(0.05)

print("led test finish!")

led test finish!

print("sws status: 0x%08x" % sws.read())

sws status: 0x00000028

4. 问题

问题1:发现在python中使用自动补全时程序崩溃

在python中使用ol = Overlay(‘zcu102_led.bit’)后,输入ol进行自动补全时会使python程序崩溃。

>>> ol.[ 1491.769317] Bad mode in Error handler detected on CPU0, code 0xbf000002 -- SError

[ 1491.776716] Internal error: Oops - bad mode: 0 [#3] SMP

[ 1491.781922] Modules linked in:

[ 1491.784963] CPU: 0 PID: 4501 Comm: python3 Tainted: G D 4.14.0-xilinx-v2018.2 #1

[ 1491.793466] Hardware name: ZynqMP ZCU102 Rev1.0 (DT)

[ 1491.798416] task: ffffffc877b4c000 task.stack: ffffff80092f8000

[ 1491.804319] PC is at 0x7f9d84b458

[ 1491.807616] LR is at 0x55cc3c

[ 1491.810568] pc : [] lr : [] pstate: 80000000

[ 1491.817946] sp : 0000007fc15c5060

[ 1491.821245] x29: 0000007fc15c5060 x28: 0000007f9945ae00

[ 1491.826540] x27: 0000007f99297e40 x26: 0000000000845578

[ 1491.831836] x25: 0000000000000000 x24: 0000000000860000

[ 1491.837131] x23: 0000007f9c5c0f60 x22: 0000007f9c645230

[ 1491.842426] x21: 000000003b4ccf90 x20: 0000007f9c645282

[ 1491.847721] x19: 0000007f9945ac48 x18: 0000007f9e0d3a70

[ 1491.853017] x17: 00000000005751e0 x16: 0000007f9d8ab650

[ 1491.858312] x15: 00000000000001ff x14: 0000000000000008

[ 1491.863608] x13: 0000007f9a2bc348 x12: 0000000000000000

[ 1491.868903] x11: 0000000000000000 x10: 000000003bb93498

[ 1491.874198] x9 : 000000003bb93490 x8 : 0000000000000001

[ 1491.879493] x7 : 00000000007b5750 x6 : 0000007f9db43008

[ 1491.884789] x5 : 0000007fc15c4a48 x4 : 0000007f9d8b5d58

[ 1491.890084] x3 : 0000007f994cb738 x2 : 5d43e4b8b60b9d00

[ 1491.895380] x1 : 0000007f9d84b458 x0 : 0000007f994cb738

[ 1491.900676] Process python3 (pid: 4501, stack limit = 0xffffff80092f8000)

[ 1491.907448] ---[ end trace fef7a706ca15de64 ]---

Segmentation fault

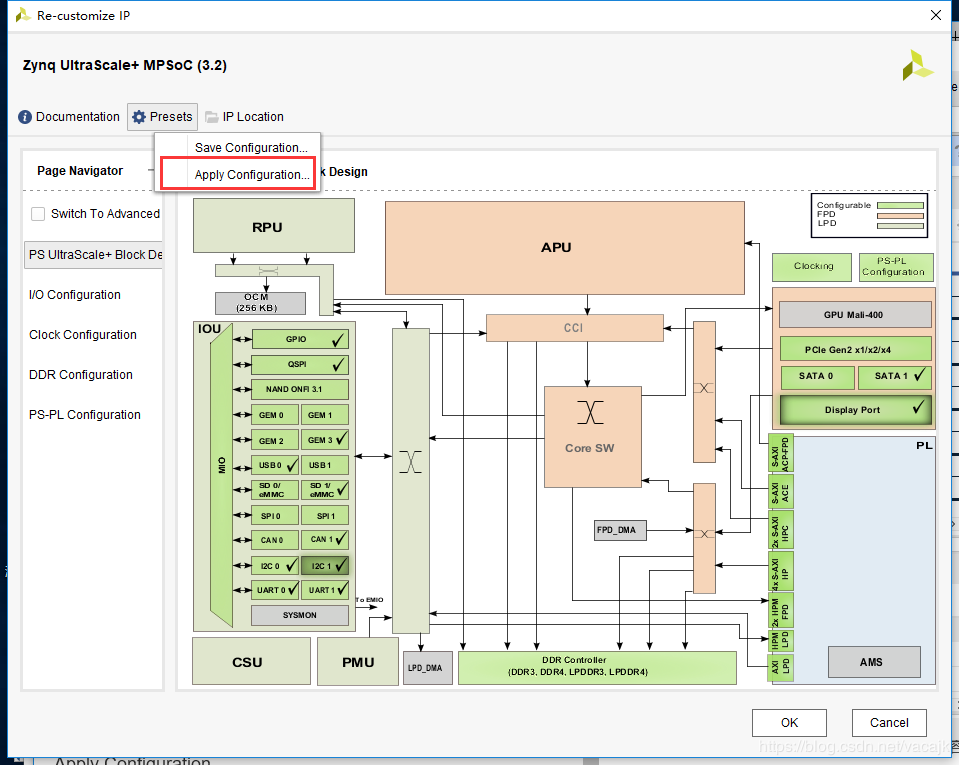

检查发现问题出在了Vivado中Zynq UltraScale+ MPSoC模块的配置有问题,但一直未定位到。。

模块配置文件:zcu102_ps_conf.tcl

可使用该配置在模块中进行Apply Configuration,就能解决崩溃问题

>>> ol.

ol.BS_FPGA_MAN ol.gpio_dict ol.load_ip_data(

ol.BS_FPGA_MAN_FLAGS ol.gpio_leds ol.parse_bit_header(

ol.axi_intc_0 ol.gpio_sws ol.parser

ol.bin_path ol.hierarchy_dict ol.partial

ol.bitfile_name ol.interrupt_controllers ol.reset(

ol.clock_dict ol.interrupt_pins ol.timestamp

ol.convert_bit_to_bin( ol.ip_dict

ol.download( ol.is_loaded(

问题2:发现网络不能正常连接

启动以后进入系统,发现没有eth0网口,感觉是下载的rootfs img没有加载执行STAGE4_PACKAGES_$(board)定义的ethernet包

查看/sdbuild/packages/ethernet内的文件内容,发现需要将eth0文件放在/etc/network/interfaces.d下

有三种方式:

1. 在格式化sd卡前,直接在linux内编辑镜像,并复制eth0到指定位置

2. 在串口控制台使用vim编辑文本,并复制到指定位置

3. 使用sudo ifconfig eth0 up && sudo ifconfig eth0 192.168.2.99 先使能网络然后用tftp将eth0文件复制到指定位置

eth0文件内容如下:

auto eth0

iface eth0 inet dhcp auto eth0:1

iface eth0:1 inet static

address 192.168.2.99

netmask 255.255.255.0

编辑完成后,重启板子,即可看到网卡信息

xilinx@pynq:~$ ifconfig

eth0: flags=4163 mtu 1500

inet 192.168.2.110 netmask 255.255.255.0 broadcast 192.168.2.255

inet6 fe80::f4e8:61ff:fe39:2f29 prefixlen 64 scopeid 0x20

ether f6:e8:61:39:2f:29 txqueuelen 1000 (Ethernet)

RX packets 1207 bytes 1082085 (1.0 MB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 1180 bytes 106838 (106.8 KB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

device interrupt 31

eth0:1: flags=4163 mtu 1500

inet 192.168.2.99 netmask 255.255.255.0 broadcast 192.168.2.255

ether f6:e8:61:39:2f:29 txqueuelen 1000 (Ethernet)

device interrupt 31

lo: flags=73 mtu 65536

inet 127.0.0.1 netmask 255.0.0.0

inet6 ::1 prefixlen 128 scopeid 0x10

loop txqueuelen 1000 (Local Loopback)

RX packets 191 bytes 22047 (22.0 KB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 191 bytes 22047 (22.0 KB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

eth0为dhcp得到的ip地址。

eth0:1为静态ip地址

编辑:hfy

-

FPGA

+关注

关注

1630文章

21791浏览量

605092 -

Vivado

+关注

关注

19文章

815浏览量

66784 -

zcu102

+关注

关注

0文章

24浏览量

7211

发布评论请先 登录

相关推荐

RE超标之整机定位详细流程

时源芯微——RE超标整机定位与解决详细流程

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

基于PYNQ和机器学习探索MPSOC笔记

PYNQ移植ZCU102详细流程分析

PYNQ移植ZCU102详细流程分析

评论