作者:材哥,玩儿转FPGA

前言

vivado和ISE的使用差别很大,Vivado是专门针对7系列和以后系列的FPGA/AP SOC进行高效设计的工具,特别是最近提出的UltraFast设计方法,能够极大地提高开发效率。ISE在支持老版本器件的基础上,目前也支持7系列/ZYNQ的设计,但是效率不能和Vivado相比。关于vivado的基本使用这里不多说,主要把一些问题点整理成“错题集”,把一些小技巧进行归纳。

清理/压缩工程

实际使用vivado的过程中,由于vivado会自动产生一系列文件,有些是不必要时刻保存的中间文件,有些是加快效率的文件(比如编译IP核后产生的文件)。但是在上传svn或者自己做备份的时候希望备份占用尽量少的空间。然而由于vivado不会自动清理,所以这时候就需要我们做手动清理了,很多人采用的方法是根据经验删除没用的文件和文件夹,这种对于不熟悉的人很容易犯下不可挽回的错误。也有人写好了批处理文件可以直接帮助删除的,但是这都不太适合初学者。其实vivado是有tcl命令可以帮助清理的。

reset_project

reset_project是vivado一个tcl命令,输入后会发现所有的IP全部清掉了编译后的文件,工程的综合和实现也被清理掉了,所以会减少空间,下面我们用一个简单的工程来对比下前后会少多少。

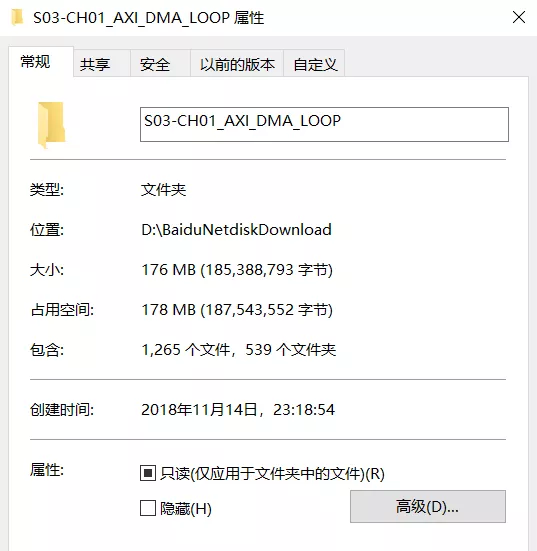

下图为某工程运行完成之后占用的资源,占用了176M。

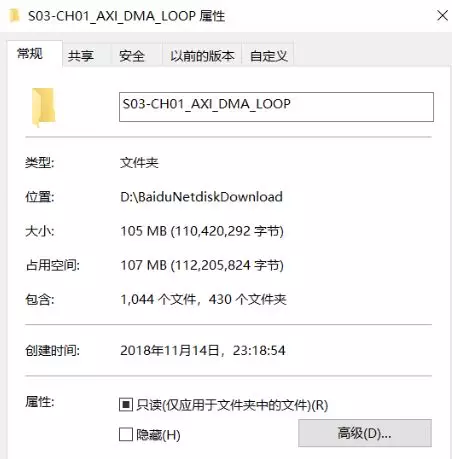

对工程运行reset_project命令后如下图所示,资源占用105M,直接减少72M,也就是减少了40%!这个压缩量还是比较可观的。

复位后的影响

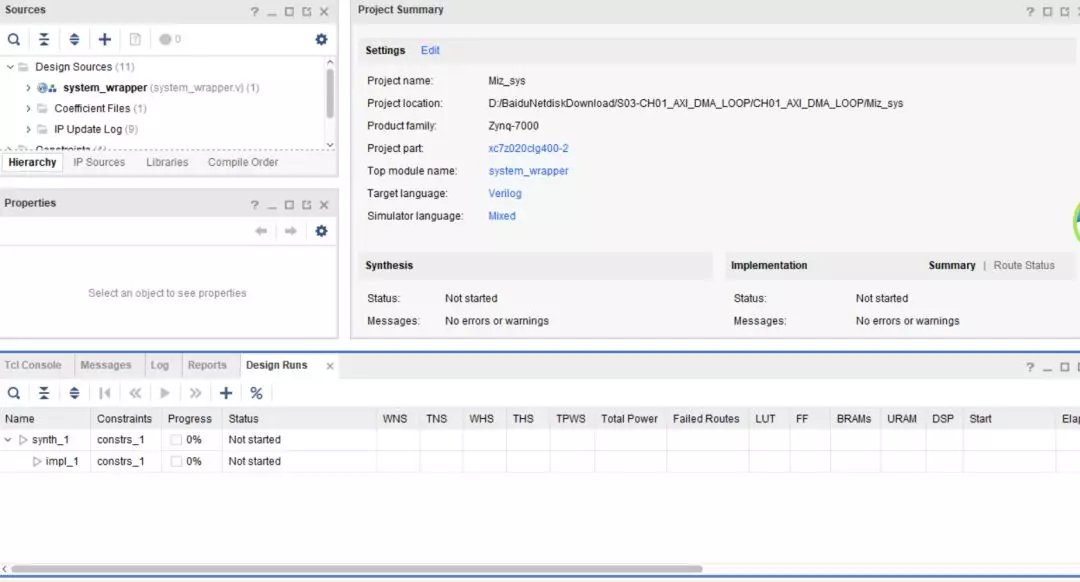

复位后是什么效果呢?可以看下图,其实复位就是把里面的综合和实现清空,包括ooc下面的IP核等都清掉,这样就只保留了最必要的文件,从而压缩了占用 空间。但是这样也带来一个问题,如果要重新产生一个可用的版本,需要的时间会更长,这个操作实际上也就是用空间换取了时间,所以大家使用前要衡量下,不要随便用,比较工程大了跑一次可能一天就没了。

编辑:hfy

-

FPGA

+关注

关注

1631文章

21806浏览量

606690 -

soc

+关注

关注

38文章

4218浏览量

219274 -

Vivado

+关注

关注

19文章

815浏览量

66960

发布评论请先 登录

相关推荐

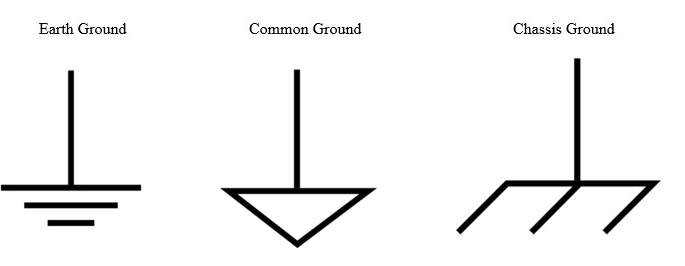

电路接地的重要性,减少不必要的地电流和相关噪声

隔离变压器可以去除不必要的噪声

设置Vivado压缩BIT文件的两种方法

如何避免PCB设计时出现不必要的错误

微软将在 GitHub 网站移除所有不必要的 cookie,不会弹出提示横幅

如何避免在iPhone上消耗不必要的电量

keil、IAR等程序工程建立批处理文件删除临时文件

使用Tcl命令保存Vivado工程

c盘怎么清理垃圾而不误删文件

越来越慢了,苹果笔记本清理内存怎么清理

使用vivado的过程如何清理/压缩不必要的文件

使用vivado的过程如何清理/压缩不必要的文件

评论