上一期的学习中,我们系统性地介绍了PYNQ与ZYNQ地区别与联系。PYNQ = Python + ZYNQ,即将ZYNQ部分功能的Python化,直接调用Python库和FPGA硬件库进行功能的开发。

Pynq降低了开发人员的门槛,但知其然也知其所以然,开发效率将会更高。因此,在进入PYNQ的python开发之前,我们先来学习ZYNQ的PL与PS开发,为接下来的学习提供良好的基础。

本部分的学习,我们依旧借助PYNQ_z2来完成。

1. ZYNQ功能块

ZYNQ中包含两大功能块:PS部分和PL部分。

PS部分指Processing System,一个基于双ARM Cortex A9内核的处理系统,其中集成了内存存储器和外部存储器接口,以及如GPIO、UART接口等大量的外设。

PL部分指Programmable Logic,基于Xilinx 7系列架构的可编程逻辑单元,通过PL部分可以为ARM定制很多外设,这也是ZYNQ的一大优点。

2. ZYNQ整体架构

ZYNQ中虽然包含PS端和PL端,但是整个设计是以ARM处理器为中心的,PS端的ARM内核可以独立于PL端运行;虽然PL端也可以独立于PS端运行,但是PL的配置是由PS端完成的,所以不能采用传统的固化FLASH的方式固化PL端程序。

PS端和PL端通信是通过AXI接口协议连接,这个协议是AMBA的一部分,是一种高性能、高带宽、低延迟的片内总线。

3. vivado与PL开发

下面我们通过一个LED灯的小项目进行本部分学习:

实验:轮流点亮LED灯

1. 打开vivado hls,点击Create New Project Project”,创建一个新工程。

选择板子的时候搜索xc7z020clg400-1,这是PYNQ的板子号,选择完成(PYNQ-Z2板采用ZYNQ XC7Z020-1CLG400C SoC)。

3. 新建一个 VerilogHDL 文件,可以通过右击 Design sourse 选择 AddSourse,选择第二个选项

选择 CreateFile…在弹出下面窗口填写新建源文件名称

创建完成点击 Finish

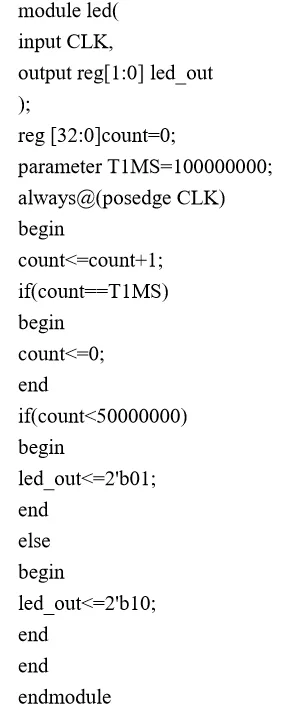

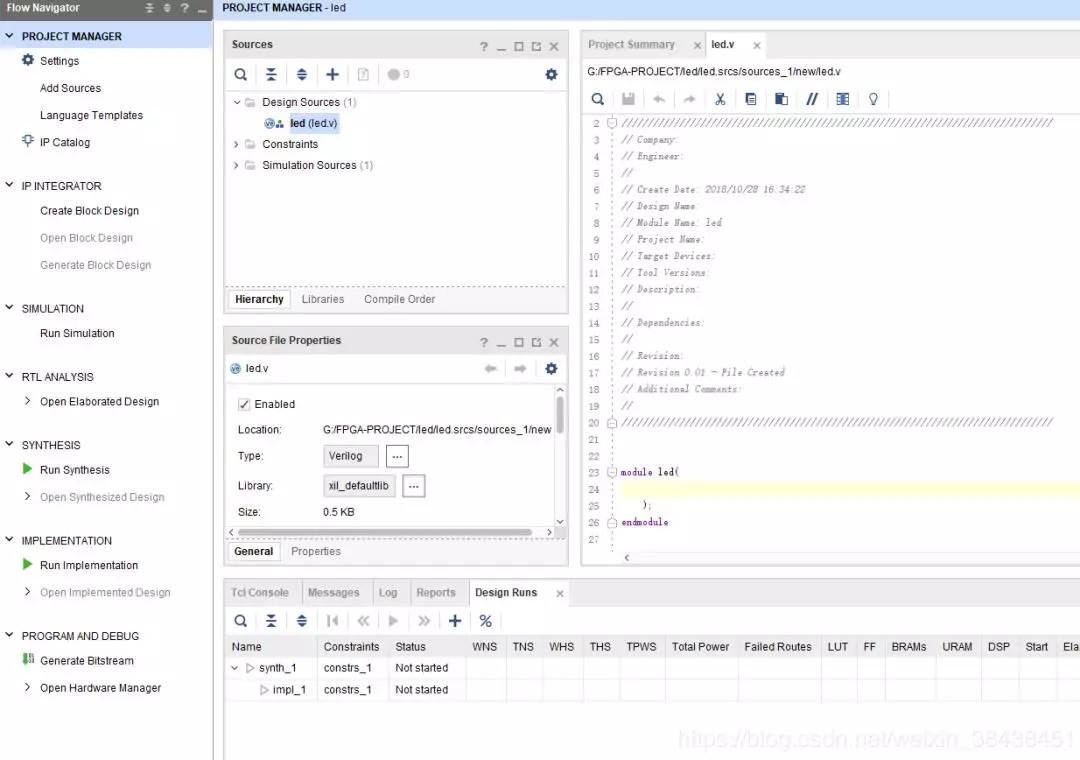

4. 在用户区 VerilogHDL 文件窗口中输入源程序,保存时文件名与实体名 保持一致,代码如下:

得到的最终界面:

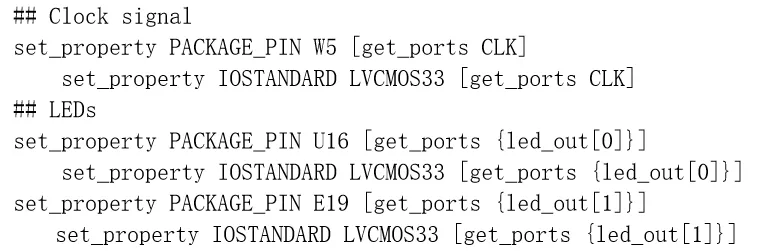

5. 新建约束文件,输入下面指令

在弹出的对话框中可以选择任务数量,这里和CPU核心数有关,一般数字越大,编译越快,单击”OK”

9. 这个时候开始编译,可以看到右上角有个状态信息,在编译过程中可能会被杀毒软件、电脑管家拦截运行,导致无法编译或很长时间没有编译成功。

编译中没有任何错误,编译完成,弹出一个对话框让我们选择后续操作,这里选项“open hardware manager” ,然后单击“OK”

10. 下载到板子

1)连接好开发板的 JTAG接口,给开发板上电

2)可以看到JTAG扫描到arm和 FPGA 内核

3)选择FPGA内核,右键选择“Program Device...” ,在弹出窗口中点击“Program”

4)等待下载,下载完成以后,我们可以看到4 颗LED开始每秒变化一次

-

FPGA

+关注

关注

1630文章

21796浏览量

605742 -

led

+关注

关注

242文章

23347浏览量

662917 -

python

+关注

关注

56文章

4807浏览量

85010

发布评论请先 登录

相关推荐

ZYNQ基础---AXI DMA使用

基于PYNQ和机器学习探索MPSOC笔记

正点原子ZYNQ7015开发板!ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2,性能强悍,资料丰富!

[XILINX] 正点原子ZYNQ7035/7045/7100开发板发布、ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2!

复旦微PS+PL异构多核开发案例分享,基于FMQL20SM国产处理器平台

FM20S用户手册-PS + PL异构多核案例开发手册

FM20S用户手册-PL端案例开发手册

有关PL端利用AXI总线控制PS端DDR进行读写(从机wready信号一直不拉高)

简谈Xilinx Zynq-7000嵌入式系统设计与实现

Xilinx ZYNQ 动手实操演练

AMD Versal AI Edge自适应计算加速平台之体验ARM,裸机输出(7)

PYNQ案例(一):ZYNQ的PL与PS开发

PYNQ案例(一):ZYNQ的PL与PS开发

评论