前言:

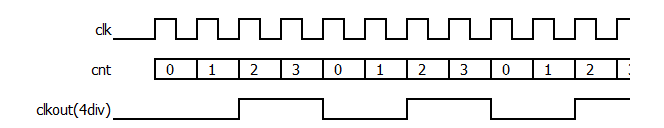

偶数分频容易得到:N倍偶数分频,可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。

奇数分频如何得到呢?

第一部分 奇数分频

奇数分频方法:

N倍奇数分频,首先进行上升沿触发进行模N计数,计数到(N-1)/2时输出时钟翻转,同时进行下降沿触发的模N计数,计数到(N-1)/2时输出时钟翻转时,进行输出时钟时钟翻转。两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数N分频时钟。

或者使用“相与”,方法与上相同,只是翻转的数值变为(N-2)/2。

三分频的Verilog实现:

module Divider_Multiple(

input clk_i,

input rst_n_i,

output div2_o,

output div3_o

);

reg div2_o_r;

always@(posedge clk_i or negedge rst_n_i) //二分频

begin

if(!rst_n_i)

div2_o_r else

div2_o_r end

reg [1:0] pos_cnt;

reg [1:0] neg_cnt;

always@(posedge div2_o_r or negedge rst_n_i) //上升沿计数

begin

if(!rst_n_i)

pos_cnt else if(pos_cnt==2'd2)

pos_cnt else

pos_cnt end

always@(negedge div2_o_r or negedge rst_n_i) //下降沿计数

begin

if(!rst_n_i)

neg_cnt else if(neg_cnt==2'd2)

neg_cnt else

neg_cnt end

reg div3_o_r0;

reg div3_o_r1;

always@(posedge div2_o_r or negedge rst_n_i)

begin

if(!rst_n_i)

div3_o_r0 else if(pos_cnt div3_o_r0 else

div3_o_r0 end

always@(negedge div2_o_r or negedge rst_n_i)

begin

if(!rst_n_i)

div3_o_r1 else if(neg_cnt div3_o_r1 else

div3_o_r1 end

assign div2_o=div2_o_r;

assign div3_o=div3_o_r0 | div3_o_r1; //相或

endmodule

仿真:

仿真文件:

module Divider_Multiple_tb;

// Inputs

reg clk_i;

reg rst_n_i;

// Outputs

wire div2_o;

wire div3_o;

// Instantiate the Unit Under Test (UUT)

Divider_Multiple uut (

.clk_i(clk_i),

.rst_n_i(rst_n_i),

.div2_o(div2_o),

.div3_o(div3_o)

);

initial

begin

// Initialize Inputs4

clk_i = 0;

rst_n_i = 0;

// Wait 100 ns for global reset to finish

#96;

rst_n_i=1;

end

always

begin

#5 clk_i=~clk_i;

end

endmodule

vivado仿真结果:

至此,第一部分结束。

第二部分 逻辑分析仪

增加逻辑分析仪:

首先为了配合手里的zc702板子,修改了一下输入时钟;为了观察分频信号,增加了一个2Hz的信号,将其连接在led上,可以看见led闪烁。

逻辑分析仪的使用分三步走:

1. 在设计文件中,在要抓取的信号定义前添加:

(*make_debug="true"*)

2. 导入ILA的IP核:

双击添加的IP,在General Options里设置探针数(信号组数)和采样深度(利用BRAM存储的),在Probe Ports里设置信号位宽:

OK之后,点击Generate。

在IP Source里双击模板,将例化模板复制到设计文件中,填好对应的待测信号:

3. 添加约束-->生成比特文件-->下载-->添加触发信号-->抓取。

为了阅读的连贯性,贴出修改后的代码:

module Divider_Multiple(

input clk_p,

input clk_n,

input rst_n_i,

output div2_o,

output div3_o,

output div2hz_o

);

IBUFGDS IBUFGDS_inst (

.O(clk_i), // Clock buffer output

.I(clk_p), // Diff_p clock buffer input (connect directly to top-level port)

.IB(clk_n) // Diff_n clock buffer input (connect directly to top-level port)

);

(*make_debug="true"*)wire div2_o;

(*make_debug="true"*)wire div3_o;

(*make_debug="true"*)wire div2hz_o;

reg div2_o_r;

always@(posedge clk_i or negedge rst_n_i) //二分频

begin

if(rst_n_i)

div2_o_r else

div2_o_r end

reg [1:0] pos_cnt;

reg [1:0] neg_cnt;

always@(posedge div2_o_r or negedge rst_n_i) //上升沿计数

begin

if(rst_n_i)

pos_cnt else if(pos_cnt==2'd2)

pos_cnt else

pos_cnt end

always@(negedge div2_o_r or negedge rst_n_i) //下降沿计数

begin

if(rst_n_i)

neg_cnt else if(neg_cnt==2'd2)

neg_cnt else

neg_cnt end

reg div3_o_r0;

reg div3_o_r1;

always@(posedge div2_o_r or negedge rst_n_i)

begin

if(rst_n_i)

div3_o_r0 else if(pos_cnt div3_o_r0 else

div3_o_r0 end

always@(negedge div2_o_r or negedge rst_n_i)

begin

if(rst_n_i)

div3_o_r1 else if(neg_cnt div3_o_r1 else

div3_o_r1 end

reg div2hz_o_r;

reg [25:0] div2hz_cnt;

always@(posedge clk_i or negedge rst_n_i)

begin

if(rst_n_i)

div2hz_cnt else if(div2hz_cnt div2hz_cnt else

div2hz_cnt end

always@(posedge clk_i or negedge rst_n_i)

begin

if(rst_n_i)

div2hz_o_r else if(div2hz_cnt==26'd24_999999 || div2hz_cnt==26'd49_999999)

div2hz_o_r else

div2hz_o_r end

assign div2_o=div2_o_r;

assign div3_o=div3_o_r0 | div3_o_r1; //相或

assign div2hz_o=div2hz_o_r;

ila_0 ila_0_0 ( //逻辑分析仪的例化

.clk(clk_i), // input wire clk

.probe0(div2hz_o), // input wire [0:0] probe0

.probe1({div2_o,div3_o}) // input wire [3:0] probe1

);

endmodule

约束文件如下:

set_property PACKAGE_PIN D18 [get_ports {clk_p}]

set_property IOSTANDARD LVDS_25 [get_ports {clk_p}]

set_property PACKAGE_PIN C19 [get_ports {clk_n}]

set_property IOSTANDARD LVDS_25 [get_ports {clk_n}]

set_property PACKAGE_PIN G19 [get_ports {rst_n_i}]

set_property IOSTANDARD LVCMOS18 [get_ports {rst_n_i}]

#GPIO PMOD1

set_property PACKAGE_PIN E15 [get_ports {div2_o}]

set_property IOSTANDARD LVCMOS18 [get_ports {div2_o}]

set_property PACKAGE_PIN D15 [get_ports {div3_o}]

set_property IOSTANDARD LVCMOS18 [get_ports {div3_o}]

set_property PACKAGE_PIN W17 [get_ports {div2hz_o}]

set_property IOSTANDARD LVCMOS18 [get_ports {div2hz_o}]

下载到fpga之后,逻辑分析仪的界面会自动打开,各个区域的功能如下,先添加触发信号,可以右键点击添加,也可以点击window-->debug probe将信号拖拽至“触发信号”区域:

总结:

信号运算得到新的信号。没有仿真就没有发言权。

编辑:hfy

-

计数器

+关注

关注

32文章

2278浏览量

95386 -

逻辑分析仪

+关注

关注

3文章

215浏览量

23358 -

BRAM

+关注

关注

0文章

41浏览量

11074 -

复位信号

+关注

关注

0文章

55浏览量

6407

发布评论请先 登录

相关推荐

需要讲解一个占空比50%的奇数分频器的原理

基于Verilog的FPGA分频设计

此通用电路可以实现任意奇数分频电路

分频器的作用是什么 半整数分频器原理图分析

基于复杂可编程逻辑器件和VHDL语言实现半整数分频器的设计

偶数分频/奇数分频/分数分频详解

奇数分频如何得到呢? 解读奇数分频和逻辑分析仪(ILA)的使用

奇数分频如何得到呢? 解读奇数分频和逻辑分析仪(ILA)的使用

评论