源代码级别调试

Vivado Simulator提供了在仿真过程中debug设计的特性,通过为源代码添加一些可控制的执行条件来检查出问题的地方。总的来说有三种调试方法:

1.使用Step逐行调试

Step命令一次只执行HDL代码中的一行,从而验证和调试设计。运行仿真后,点击Run->Step或工具栏中的Step可执行该命令。Restart可以将时间复位到TestBench的开始。当前执行的代码会高亮显示并且前方有箭头指示:

运行Step后会打开与顶层设计单元相关的HDL文件窗口,在窗口名称上右键->新建水平分组或新建垂直分组即可同时查看HDL和波形窗口。

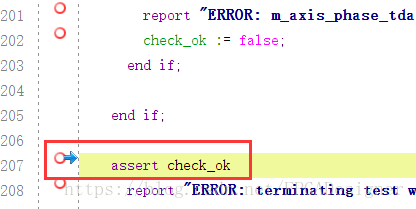

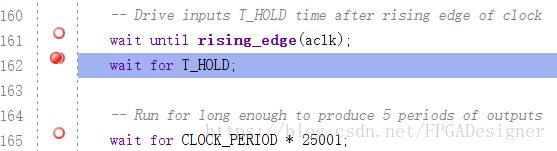

2.使用断点(breakpoint)调试

Step调试的缺点是在大型设计中很繁琐且花费大量时间。设计者可以在源代码中自行指定运行停止的点,称为断点。运行仿真时,仿真器遇到断点就会暂停。可设置断点的行前有一个空心圈,点击可设置断点,转变为实心圈。

对应的Tcl命令为“add_bp file_name line_number”。仿真调试过程中,断点和Step调试是可以一起使用的。在实心圈上右键,或Run菜单中点击Delete All Breakpoints可以删除所有断点。

3.条件调试

在设计中添加条件断点,仿真器检测到条件为真时就会暂停当前仿真。条件必须用Tcl命令添加,示例如下:

add_condition #命令模板

add_condition {reset == 1 && clk == 1} {puts “Reset went to high”; stop}

#当clk与reset同时为高暂停仿真,控制台打印消息输出

遇到条件断点并暂停后,只有等到下一个仿真命令才会继续运行仿真。

将对象强制到特定值

Vivado Simulator提供了Force功能将信号、wire或reg强制为某一值,该操作会重写信号定义在HDL设计中的行为。考虑如下应用情况:

- TestBench中没有对某一信号进行驱动,可以使用Force功能给予激励;

- Debug过程中使用Force纠正错误的值,以继续进行仿真分析。

使用Force Constant、Force Clock、Remove Clock相关命令配置Force功能,而且仿真restart后仍然会保留已经设置了的Force特性。

1.Force Constant功能

该命令会将信号固定为一个常数值,重写了其HDL代码中的赋值。在Objects窗口或波形窗口中选中某一对象,右键->Force Constant,打开如下窗口:

Force value按照value radix选择的基数设置常数值;设置的值开始于Starting after time offset设置的时间,如果不带单位则默认为ns;Cancel after time offset设置的时间后会取消应用Force功能。

2.Force Clock功能

该命令会使信号以一定速率在两个值之间来回转换,类似于时钟信号一样(但不局限于生成时钟信号,可以定义任意振荡的值)。在Objects窗口或波形窗口中选中某一对象,右键->Force Constant,打开如下窗口:

Leading edge value和Trailing edge value分别指定两个振荡状态的值;Duty cycle和Period设置占空比和周期。右键菜单中的Remove Force用来清除设置。灵活使用Force特性可以加快设计仿真的调试验证,而不需要修改HDL代码。

编辑:hfy

-

vhdl

+关注

关注

30文章

819浏览量

128724 -

DEBUG

+关注

关注

3文章

94浏览量

20086 -

Vivado

+关注

关注

19文章

819浏览量

67236

发布评论请先 登录

相关推荐

ARM的三种中断调试方法

【分享资料】ARM的三种中断调试方法简介

ARM的三种中断调试方法介绍

三种电路仿真软件比较及器件模型加入方法

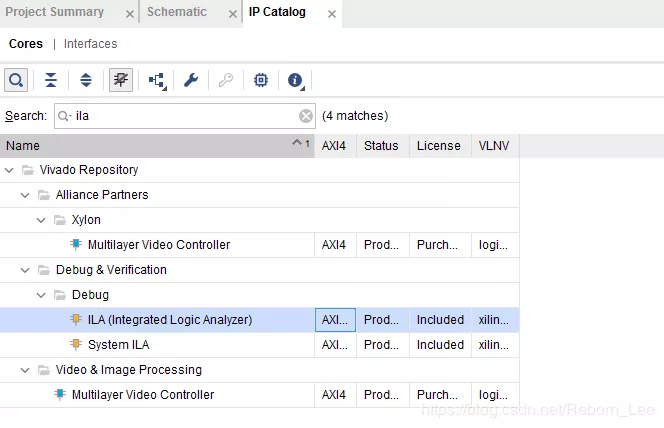

Vivado+FPGA:如何使用Debug Cores(ILA)在线调试

Vivado中使用debug工具步骤与调试技巧

如何使用Vivado Logic Analyzer与逻辑调试IP进行交互

Vivado调试ILA debug结果也许不对

关于Vivado中三种操作Debug的方式

一文解析Vivado的三种封装IP的方式

FPGA应用之vivado三种常用IP核的调用

MCUXpresso IDE下在线联合调试双核MCU工程的三种方法

Vivado使用技巧:debug仿真设计的三种调试方法

Vivado使用技巧:debug仿真设计的三种调试方法

评论