鉴于芯片设计的复杂度提升, 成功设计一个芯片所牵扯的步骤与过程也愈加复杂,所需花费的资金也成倍增加,一个典型的芯片开发项目的周期和花销如下所示

可以见到在芯片制造出来之前,很多精力会花费在RTL代码验证工作上,另外软件的相关开发工作,也会在得到芯片前开始,这2方面都需要借助FPGA原形来模拟芯片的行为,帮助硬件开发和软件开发者,共同提升工作效率。

FPGA原型在数字芯片设计中,基本是必不可少的,原因非常明显,相比用仿真器,或者加速器等来跑仿真,FPGA的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。当然FPGA原型作为芯片的替身,也是有诸多限制的,比如规模限制,速度限制,功耗限制,结构限制等,在使用FPGA原型作为芯片的替代时,需要进行相应的修改,才能完成相应功能,甚至有些功能最终无法覆盖。

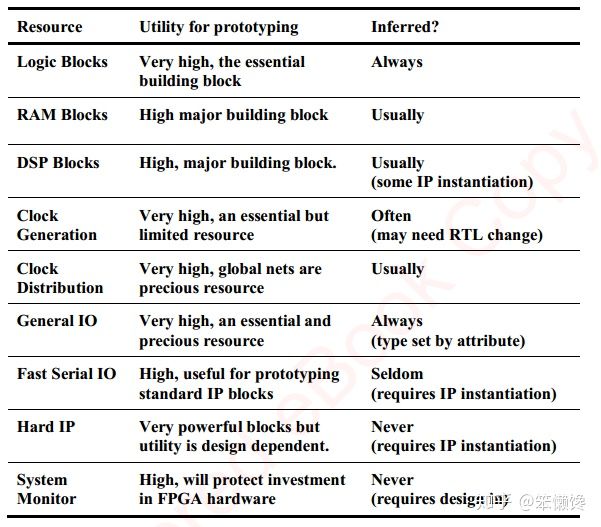

如果对FPGA中可以映射为ASIC的资源做逐一对比,我们可以得到这样的表格。

以上表格看出,除了普通的RTL逻辑以及基本端口,其他的类似存储时钟DSP等,最好都是做手动修改进行映射,把ASIC设计转换为FPGA比较靠谱。

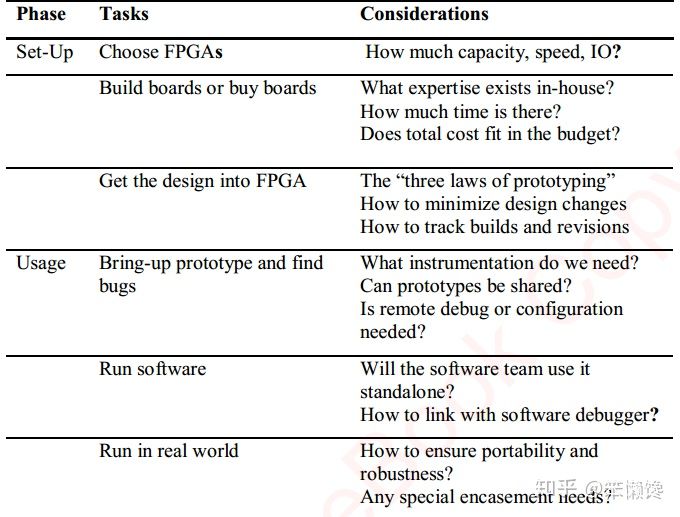

要把一块ASIC做出FPGA的原型,需要大致一下步骤,

1 FPGA选型

2 做板或者购买原型板。

3 将ASIC设计转换装入FPGA

4 调试启动FPGA原型

5 载入软件协同运行

6 软硬件系统验证

下文就按照这些步骤逐一讨论:

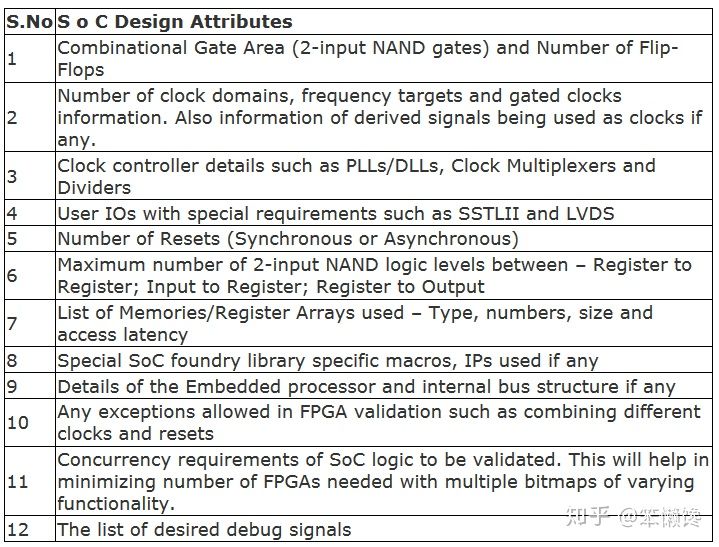

第一个就是FPGA的选型问题,在选型前,当然需要对ASIC的设计进行大致的了解,包括以下各方面:

选型问题最关心的几个维度:

1 容量 其中包括纯逻辑容量,存储容量,dsp单元容量这些

2 内置IP 包括时钟,存储控制,cpu等的硬核

3 接口 普通接口与专用高速接口

4 速度 资源占用率在50%左右时的速度,一般被用来评估原型

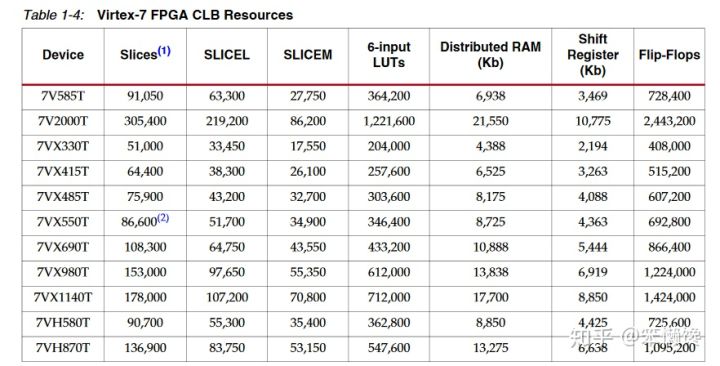

其中纯逻辑容量,也就是ASIC中组合电路与触发器的容量,是可以直接与FPGA中的资源换算的。

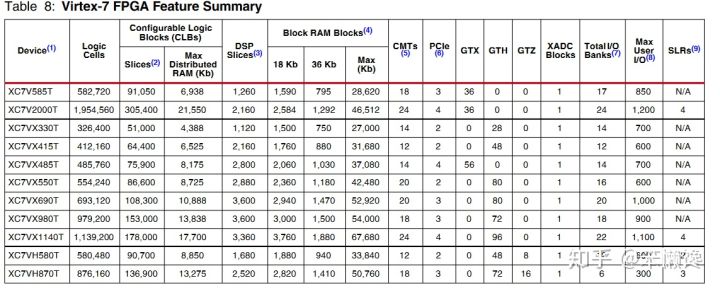

比如上图xilinx V7 2000T中有2.4M FF,大致对应ASIC的2输入与非门10M gates,如果使用率按照50%算,大概放置5M逻辑门没问题。

内置的存储器,可以实现21M的单双端口ram,rom,fifo等,如果ASIC中使用的存储稍微多一点,也可以用lut实现部分的存储,替代block ram。

如果使用较多乘加运算,也可以映射fpga中的dsp器件实现,具体各种型号的FPGA包含多少器件,可以参考xilinx文档。

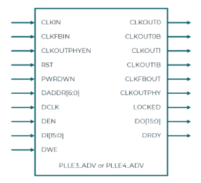

对于内置ip,最先要考虑的,就是时钟模块MMCM,一般FPGA会有几个到几十个时钟模块,例如下表2000T中包含24个CMTs,也就是24个PLL和MMCM,每组PLL和MMCM可以对一个时钟域的时钟进行分频倍频。一般ASIC会包含多个时钟域,每个时钟域至少需要一个CMTs对时钟进行操作,可以据此选择使用哪个FPGA器件。

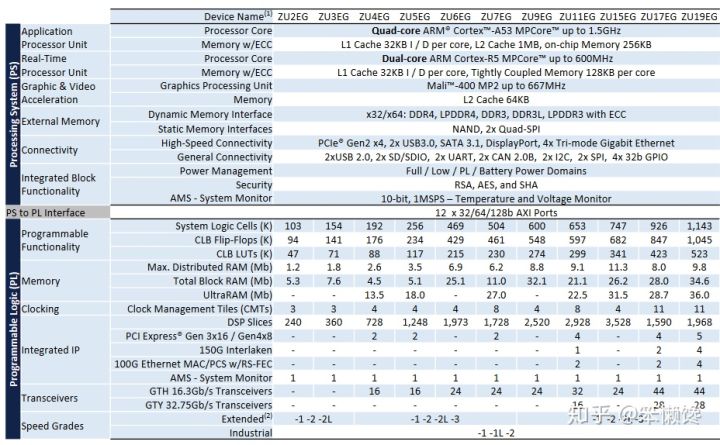

如要选择带有ARM硬核的FPGA来模拟ASIC中的ARM核,则需要选择zynq系列。系统中自研的逻辑,则通过AXI挂入总线中,当然这样未必能使FPGA与ASIC中的系统完全一致,但是作为一个圆形,也是足够的,以下是部分带有ARM核的FPGA的容量以及相应IP情况

对于接口的限制,一般FPGA的普通接口数量够大,不会成为瓶颈,主要在于ASIC所需的特定接口,在FPGA中是否能够满足,很多时候这些特定接口需要外接phy才能完成相应功能。

影响FPGA最终运行速度的因素很多,包括代码风格,具体设计,资源占用率,FPGA型号等,所以这需要在RTL代码基本框架完成后,通过工具综合才能得到一个大致数值,所以作为ASIC原型,尽量选择速度够快的FPGA。

通过以上限定条件,基本可以选出使用哪种FPGA型号,但是可能ASIC资源占用太多,任何一种都装不下,这就有2种解决方式了。一种是分块分别验证,当然这样风险极高,且没法直接验证最终系统。

另外就是使用多片FPGA得到原型,这就要涉及不同FPGA之中功能划分的问题,这个是比较麻烦且有难度的事情,对FPGA电路设计,以及ASIC到FPGA的代码转换,都有挺多新问题。

第2步就是制版,这需要考量的方面也是相当多,比如信号完整性,电源问题,时钟问题,可扩展性等,本人对此没有直接经验,也就无从展开。当然对于需要多个FPGA的验证板,一般实力的团队,未必能搞定,所以选择花钱买平安,直接选用类似HAPS这样的验证系统,可能更靠谱。

第3步就是ASIC的设计装入FPGA。这需要对原本面向ASIC的代码,进行修改。

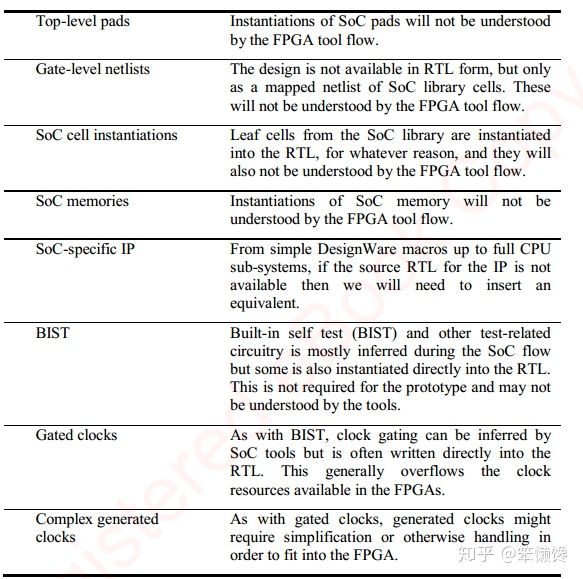

对于一般的纯RTL逻辑,在ASIC中与FPGA中都可以综合出可用结果,但是以下表中的器件,需要修改

芯片中的pad,一般是fab厂给出的硬核,具有输入输出,驱动上下拉控制等。在转换成FPGA时,一般会在例化中直接用assign替代,并.XDC或者.v中指定上下拉等

如果有ASIC门级网表,可以把底层ASIC实例器件用verilog行为描述替换,在FPGA综合中则可以对应实现。其他的简单cell例化,也可以这样转换一下。

对于存储器,一般可以在FPGA中找到与ASIC功能一致的SRAM,ROM ,可以直接把FPGA MEM 外包一层改变端口名字,替代ASIC MEM。小的嵌入flash,则可以把FPGA的SRAM包一层逻辑来模仿。

其他的硬核IP, 可能需要在FPGA中寻找功能一致的,并相应修改接口,与ASIC代码中其他部分有效连接。

对于BIST,最直接的办法是去除,一般不会影响实际功能。

对于各种门控时钟,倍频分频等,一般需要针对FPGA做手动修改,使用DCM完成与芯片中时钟一致的行为。

以下就一些修改中会出现的具体问题,详细说明。

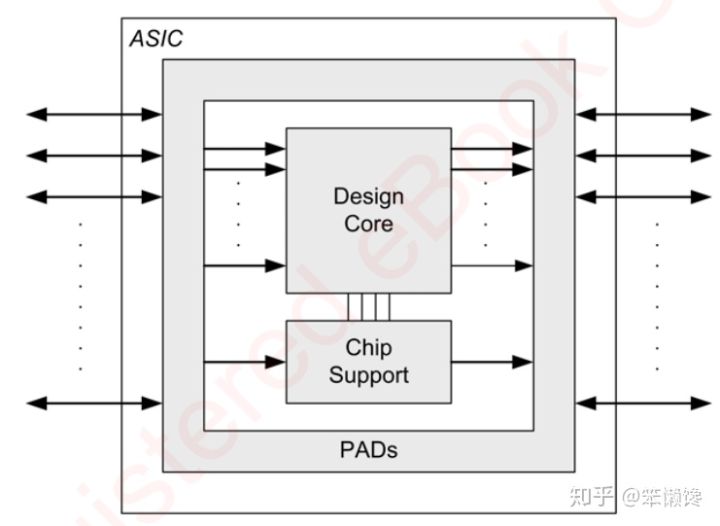

首先我们拿到的ASIC设计的结构,基本如下图所示,最外一圈是各种pad ring,里边先是芯片的各种辅助功能,包括 clk, rst, power, test,debug等。然后是与芯片实际功能相关的部分,可能包括部分模拟电路,数字电路包括cpu,mem 总线,各种逻辑控制等。我们需要明确用FPGA来原形验证的,主要是数字电路中的那些核心功能,芯片核心外部的那些辅助逻辑,很多是需要修改的,也是无法得到验证的。这里的pad一般直接在FPGA中直接去例化一个包含几个assign语句的 FPGA PAD 等效实例,clk rst 需要根据具体上电顺序,时钟资源做调整,一般会对rst功能进行简化,做成一个全局复位,clk中的分频与关断功能会放在CMT中实现。power控制,一般在FPGA中直接忽略,因为用FPGA几乎无法模拟各种UPF指定的行为。debug test可以根据实际情况保留或者去除,但是即使保持,一般也不会真的去用。核心功能中需要更改的,一般就是各种内部存储器了。

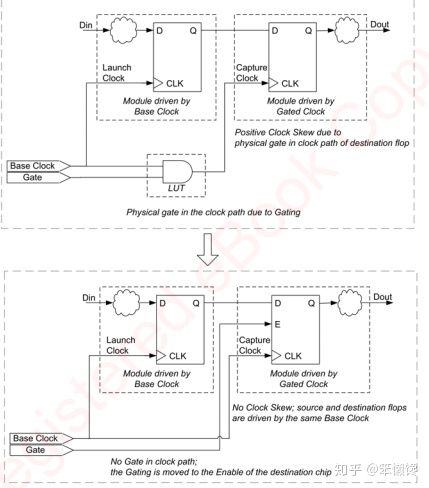

时钟门控 clock gating 一般在ASIC中广泛使用,一般会在clk模块中例化成由latch与门组成的门控单元,对某个模块进行时钟控制。这些门控单元,如果直接在FPGA中例化为相同逻辑的latch与门,逻辑功能是没有问题的。但是这时与门出来的受控时钟,则不能再FPGA的专用时钟网络中走线,而是走普通的信号网络,这样FPGA能达到的频率很差。为了纠正这样情况,可以把对寄存器的门控,放在寄存器端,也就是选用FPGA中行如FDCE这样带门控的寄存器。这个过程可以手动完成,但是比较麻烦,一般来说专门的FPGA综合工具能做这种自动转换。比如 vivado中使用 (* gated_clock = "true" *) input clk_a; 标定受控时钟,并在脚本加入 -gated_clock_conversion on 综合选项。

当然如果需要的可控时钟不太多,也就是少于FPGA中BUFGCE的数量,则可以直接把门控信号加在 BUFGCE的控制端,输出就是走时钟网络的门控信号了。如果FPGA器件中有 BUFHCE,则可以对更多层级的时钟进行门控,也就可以得到更多的受控时钟。

有关FPGA门控时钟的更详细解释,可以参照 https://forums.xilinx.com/t5/General-Technical-Discussion/Reg-Clock-gati...

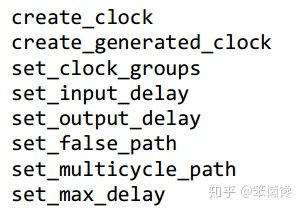

ASIC转变到FPGA使用的综合约束,在SDC与XDC基本相容,例如

这些都可以直接使用,当然很多情况下FPGA还是不可能跑到ASIC速度,必须降速运行。另外还需要添加FPGA中对管脚位置,类型,驱动强度等的约束,以及一些综合选项

以上即为对ASIC代码更改的主要部分,在下到FPGA板调试前,最好对更改的FPGA代码进行仿真,确认功能正常,减少上板调试的工作量。

第4步为启动调试FPGA原型。

在把修改后的FPGA代码装入调试前,先需要保证FPGA板本身是正常可用的,这时如果是外购的开发板或者类似haps的验证系统,则会省去一些麻烦。

如果是头次开发的FPGA板,则需要先装入一个最简单的FPGA镜像文件,测试一下FPGA的电源供电,下载连接是否可用,然后通过几个用于测试的FPGA文件,测试下板上与FPGA连接的其他器件是否正常工作。一般头次设计的板子,多少会有各种问题,比如电源供电问题,管脚连接的差分信号匹配问题,阻抗匹配,电流驱动,信号质量等问题 如果板子通过了以上测试,则可以认为电路硬件设计没有问题,可以装入FPGA原形文件进行测试了。

装入修改了的FPGA原型模拟ASIC,一般不会一次成功,一般出现的问题可以分为以下三类:

1 RTL逻辑错误,包括原本ASIC既有的和修改过程引入的错误。

2 接口错误 与外部器件的电信号连接错误,包括电压不匹配,驱动电流不一致等。

3 软件错误 MCU运行的软件没有正确配置相关功能导致,这种一般在仿真中难以发现,因为仿真很少运行真正的软件系统。

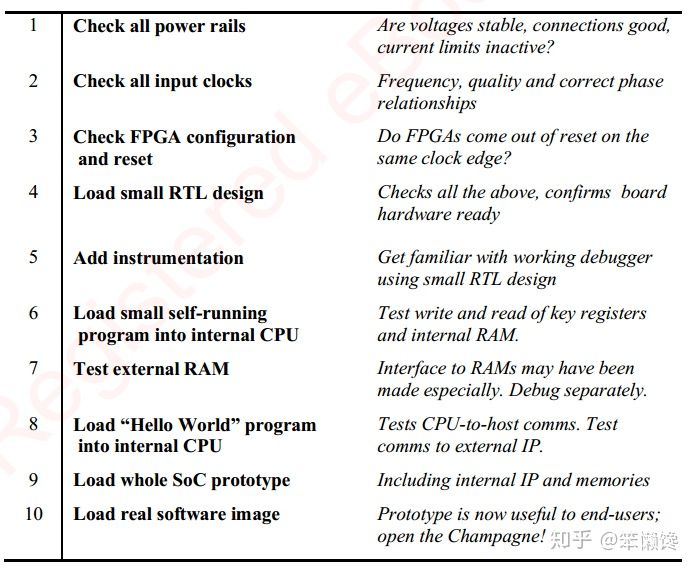

对fpga原型的板上调试,可以归纳为以下步骤。

当载入实际运行的软件后,通过FPGA原型,就可以如同在实际芯片中一样,对软件进行测试修改,同时完成系统级的验证工作了。也就进入了步骤5.6,这与普通的嵌入式软件开发大致相同。

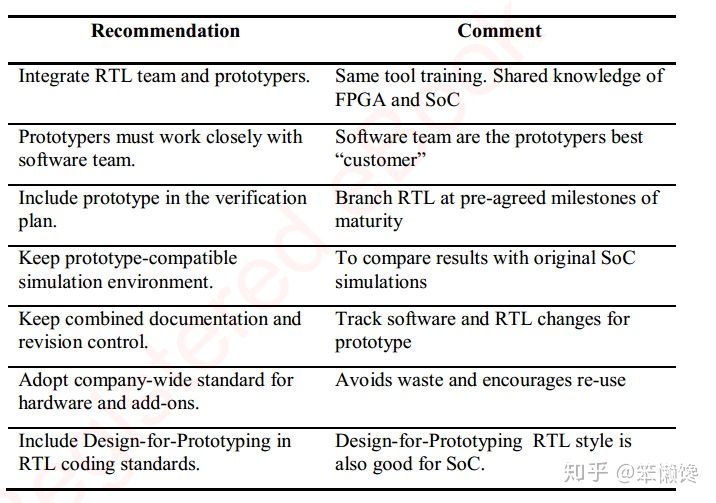

对于通过FPGA进行原型验证,有以下设计流程上的建议,值得参考

以上参考了xilinx网站内容,以及FPMM等书。

编辑:hfy

-

FPGA

+关注

关注

1635文章

21832浏览量

608137 -

asic

+关注

关注

34文章

1209浏览量

121128 -

Xilinx

+关注

关注

71文章

2173浏览量

122760 -

芯片设计

+关注

关注

15文章

1041浏览量

55176

发布评论请先 登录

相关推荐

AMD技术赋能西门子FPGA原型设计解决方案

新思科技推出基于AMD芯片的新一代原型验证系统

芯华章发布新一代FPGA原型验证系统HuaPro P3

FPGA与ASIC的区别 FPGA性能优化技巧

数字芯片设计验证经验分享文章 实际案例说明用基于FPGA的原型来测试、验证和确认IP——如何做到鱼与熊掌兼

FPGA与ASIC的优缺点比较

解锁SoC “调试”挑战,开启高效原型验证之路

FPGA算法工程师、逻辑工程师、原型验证工程师有什么区别?

将ASIC IP核移植到FPGA上——更新概念并推动改变以完成充满挑战的任务!

大规模 SoC 原型验证面临哪些技术挑战?

基于FPGA的ASIC协同原型验证设计方案

基于FPGA的ASIC协同原型验证设计方案

评论