正如在涉及PCB设计和制造过程的各种资料中指出的那样,在选择层压板时,产品开发人员需要熟悉多种材料属性。PCB频率越复杂且频率越高,这些属性就变得越关键。它们包括:

- 材料经过层压过程以及随后的冷却过程后如何收缩。

- 材料在层压循环中的行为。

- 物料如何钻孔。

- 怎样制版。

Dk或介电常数eᵣ在层压板的各种厚度上如何变化以及它如何随频率变化。影响因素包括:

- 将材料(真空除外)的介电常数与真空进行比较。

- 这种比较产生了一个eᵣ,它表示了这些材料与真空相比对速度和电容的影响。

- 材料的Df或损耗角正切如何影响PCB的操作。

- 这是衡量RF信号中有多少能量在PCB的电介质中损耗的度量。

- 当一种材料被称为高速时,这就是被参考的特性。

这些属性如何影响这些?

支持将低Dk层压板用于复杂PCB(如底板)的最初论点是,它可能更薄。希望使底板变薄的原因是,它更易于电镀孔,从而降低了长宽比,并且更适合用于连接诸如压配合连接器的结构。另一个论点是,如果通孔较小(由于电路板较薄),则它们的电容将较少,从而不会干扰高速信号。另一个考虑因素是,使用低Dk层压板将允许更宽的走线,从而降低铜损。

根据上述参数,对低Dk和低DF材料进行了比较研究。该研究中的信息及其结果将在本文的下一部分中介绍。

低介电材料的好处是什么?

低Dk层压板的优点及其在高速差分信号方面提供的优势包括:

如上所述,对于选择来产生给定阻抗的给定走线宽度,在走线及其相邻平面之间使用的层压板可以更薄,从而使PCB整体更薄。

如果选择F 或选择产生给定阻抗的给定厚度的层压板,走线宽度可以更宽。由于迹线中的趋肤效应损失,这导致较低的信号损失。

注意:在非常高的频率下,导体的电流将不再均匀地流过导体的整个横截面。相反,它在表面附近拥挤。这是皮肤效应丧失的现象。

前述好处似乎是基于以下理由使用低Dk材料的有力论据:

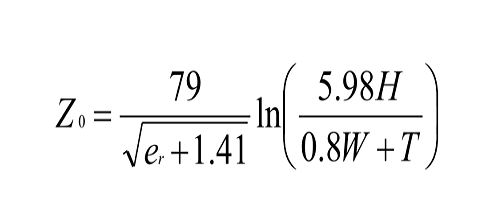

下面所示的等式1通常用于计算表面微带传输线的阻抗。已经证明它与现代PCB中使用的尺寸不正确,但是它说明了Dk或eᵣ如何影响阻抗。

等式中的变量为:H =平面上方的高度,W =迹线宽度,T =迹线厚度,eᵣ=相对介电常数或Dk,Zₒ=阻抗(以欧姆为单位)。

请注意,降低eᵣ会导致较高的阻抗,相反,提高eᵣ会导致较低的阻抗。

如果使用较低的e层压板,则对于给定的阻抗,走线宽度可以变宽,从而降低了铜损。

公式1.阻抗公式

导致低DK材料的大型,高层数背板的因素似乎很有吸引力

在当今高性能产品中使用的较大的,高层数的背板,其中存在大量的高速差分对,例如Internet核心路由器和交换机,其厚度可高达400密耳(10毫米)。这种厚度带来了两个不同的问题,包括:

通孔的钻孔和电镀可能很困难。

这些长而大的孔的寄生电容可能会在非常高的数据速率下对信号质量产生不利影响,因此需要进行“反向钻孔”以去除孔中的大部分多余铜。

注意:利用当今产品的高数据速率,无法将背板做得足够薄以避免执行背钻过程。

较低的Dk层压板将减少获得所需阻抗所需的层压板厚度,并降低PCB的整体厚度和空穴电容。

迹线宽度问题包括:

从上面的方程式1可以看出,对于平面上方的给定高度,较低的Dk层压板可以为给定的目标阻抗使用更宽的迹线。

如上所述,使用更宽的走线的动机是通过增加走线的表面积来减少由“集肤效应”现象引起的信号损失。

根据前述内容,对于那些包含以高速差分信号为特征的高速背板的产品,使用低Dk层压板似乎是“不费吹灰之力”的决定。当您考虑减少PCB的整体厚度并增加走线时,尤其如此。但是,就像生活中的大多数事物一样,一切都有很多优点的事物也都有缺点。在低Dk层压板的情况下,问题是成本(低Dk层压板更昂贵),供应来源有限且交货时间长。从最近对COVID-19的影响来看,

如果有另一种方法怎么办?

基于与低Dk层压板相关的优点和缺点的平衡,值得考虑一种替代方法。通过使用低损耗材料可以找到这种方法。损耗角正切或Tan(f)表示电磁场中通过电介质吸收的能量的数量。并且吸收的能量随频率增加。

为了确定低Dk和低Df层压板之间的性能特征,我们进行了以下分析。

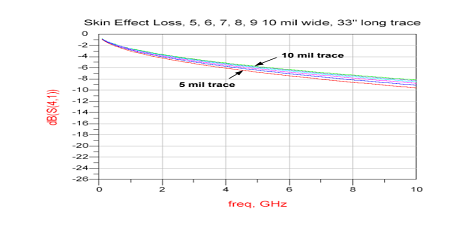

图1中的曲线显示了当走线宽度从5密耳(127微米)变化到10密耳(254微米)时,铜损耗的减少与33“(84 cm)带状线信号路径走线宽度变化的关系。可以看出,两个迹线宽度之间几乎没有差异。当然不足以带来实质性的改善。

图1.铜损与 33英寸带状线信号路径的走线宽度。迹线宽度变化,5密耳和10密耳

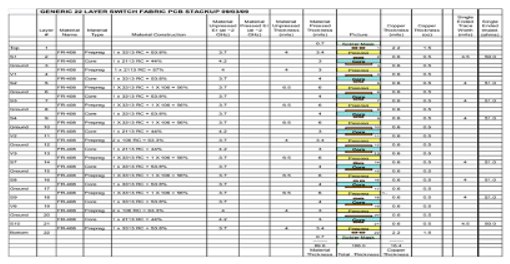

接下来,图3显示了22层板的堆叠,该板在106密耳(2.56毫米)厚的板上具有4密耳(101微米)宽的带状线迹线。

图3. 22层,106密耳(2.56毫米)厚的板和4密耳(106微米)宽的带状线迹线

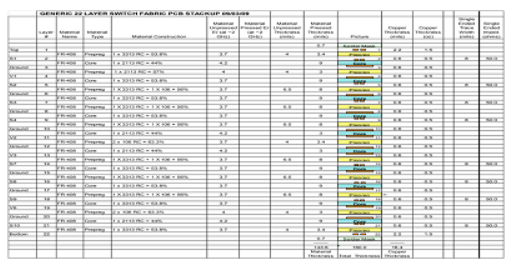

现在,我们将图3与图4进行比较,图22是一块22层板的堆叠,该板上在160密耳(4毫米)厚的PCB上具有8密耳宽的带状线迹线。根据图1、2、3和4中提供的信息,我们可以得出以下结论:

图4. 22层,160密耳(4.4毫米)厚的板和8密耳(203微米)宽的带状线迹线

如果人们通过将迹线宽度从5 mils更改为10 mils(仅通过将Dk减小一半以上)来检查2.5 GHz(大约5 Gb / S)时的损耗变化(仅通过将Dk减小一半以上),就可以将路径上的损耗仅提高1 dB。长33英寸(84厘米)。这不是实质性的收获。

如果通过使用损耗较低的叠层来检查相同频率下的损耗变化,则损耗降低为2 dB。

如果使用一种较新的超低损耗层压板,则2.5 GHz的改善幅度超过6 dB。

图3显示,将走线宽度从4密耳增加到8密耳,会使22层PCB的厚度增加60%。

使用低Dk层压板以允许使用更宽的迹线不会导致损耗的显着改善。

使用低损耗的层压板可以使板整体更薄,而不是通过使走线更宽并使用低DK层压板来减少损耗。它还可以显着提高性能。

选择低Df层压板与低Dk低层压板所反映出的两个最明显的因素非常简单:低Df层压板有很多货源,并且价格比低Dk层压板便宜得多。但是,更重要的是,它们提供了更好的性能。

利用当今复杂的高速电路板,产品开发人员一直在寻找改善产品整体性能的方法。通常,假设使用低Dk层压板并增加走线的宽度将显着改善整体性能。Dk层压板是单一来源的,价格昂贵,交货时间长。但是,详细的分析表明,提高性能的更好方法是使用更便宜,使用范围更广的低Df层压板,该层压板还可以显着提高性能。

编辑:hfy

-

pcb

+关注

关注

4319文章

23111浏览量

398307

发布评论请先 登录

相关推荐

高频PCB设计过程中的电源噪声的分析及对策

PCB设计和制造过程中多种材料属性的重要性

PCB设计和制造过程中多种材料属性的重要性

评论