实现一种基于Zynq-7000全可编程片上系统(AP SoC)的板级支持包(BSP)设计方法及应用流程。该BSP设计主要面向工业自动化监测领域,提供了一种行之有效的嵌入式系统BSP实现流程,有利于提高工业自动化监测系统的开发效率。针对使用串行通信方式的工业监测设备,设计面向小型自动化监测系统的FPGA工程,并使用专门针对基于FPGA的片上系统而设计的PetaLinx工具构建嵌入式Linux系统。最后通过自行研制的基于Zynq XC7Z010系列型号芯片的硬件平台验证了BSP设计的正确性及稳定性。

0 引言

物联网及嵌入式技术的发展推动了信息化与工业化的快速融合。作为一种新型产业模式,工业物联网(Industrial Internet of Things,IIoT)在过去几年的研究和实践中受到很大关注[1-2]。IIoT的迅速发展使得自动化监测系统的设计与研发成为新的科技热点。IIoT将传感器网络与自动化系统相结合,已被用于多个行业,以提高生产力和安全性[3-4]。自动化监测系统在IIoT感知层与应用层间起着重要作用,随着涉及的业务需求日益复杂,它的实现也变得越来越具挑战性。在工业应用场景中软件体系结构设计对于自动化系统的高效运行非常重要。先进的软件工程解决方案对自动化系统设计的效率影响很大[5]。Xilinx Zynq AP SoC通过集成处理器的软件可编程性与FPGA的硬件可编程性,实现了优异的设计灵活性,可提供面向嵌入式领域可重配置的软件工程解决方案,从而加速生产力。

BSP在嵌入式系统中扮演着关键角色,主要用来适配特定类型的硬件平台。它通常包含了用来配置可定制电路的硬件比特流、引导加载操作系统的基础支持代码以及主板上所有设备的驱动程序。BSP开发目的在于屏蔽底层硬件,提供操作系统与硬件驱动,使操作系统能稳定运行于主板环境[6-7]。由于传统BSP设计存在不可或不易修改、难以复用以及设计流程复杂等问题,本文面向工业监测领域中的自动化系统,采用Xilinx提供的Vivado集成开发套件及用于构建和部署嵌入式系统到Xilinx全可编程处理器平台的PetaLinux工具,完成了基于Zynq-7000 AP SoC的BSP设计与实现。

1 BSP总体结构

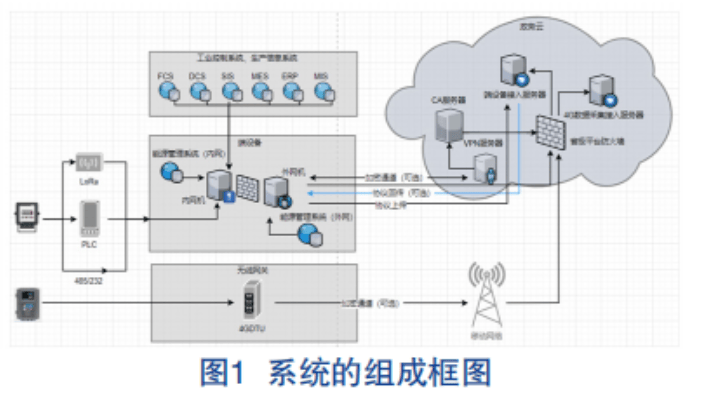

BSP设计最终生成对应用层提供支撑的镜像文件为BOOT.BIN和image.ub。BSP的总体架构如图1所示。BOOT.BIN启动镜像主要负责系统硬件部分配置,用于上电后配置Zynq芯片的处理器系统(Processing System,PS)及可编程逻辑(Programmable Logic,PL),并为Linux操作系统准备运行环境。image.ub支持内核升级,功能可裁剪,由PeteLinux工具编译打包生成。

第一阶段引导加载器(First Stage Boot Loader,FSBL)在启动存储区之后运行,启动存储区在ARM核上电启动时自动执行,负责加载FSBL至片上存储器(On Chip Memory,OCM)或在线性Flash存储介质上直接运行。对于运行在Zynq平台的Linux系统而言,第二阶段引导加载器(Second Stage Boot Loader,SSBL)即为通用引导加载器(Universal Boot Loader,U-Boot)。Xilinx提供了用于适配不同系列Zynq主板的U-Boot。基于Zynq-7000 AP SoC的BSP各个组成部分对应的功能说明如下:

(1)FSBL。FSBL负责初始化Zynq AP SoC PS端资源并使用硬件比特流文件配置PL端资源。

(2)硬件比特流。硬件比特流由Vivado集成开发工具构建的FPGA系统生成,包含FPGA编程信息,用于配置FPGA器件。

(3)SSBL。SSBL负责初始化内存和必要的外设资源,设置Linux内核的启动参数以及加载Linux系统到内存中运行。

(4)Linux内核镜像。Linux内核镜像是Linux操作系统的核心,提供硬件抽象层、进程及内存管理、磁盘与文件系统控制等功能。

(5)根文件系统。根文件系统基于BusyBox源码构建,负责管理Linux系统启动及运行时所必需的目录和关键性文件。

(6)设备树。设备树文件用于描述部分硬件信息并在Linux系统加载设备驱动时传递配置参数。

2 FPGA工程设计

传统工业监测设备中很多是符合RS232、RS422或RS485等串行数据通信标准的设备。对于自动化监测系统而言,如何面向这些监测设备提供可重配置的接口,成为一个需要解决的关键问题。许多传统工业设备所提供的功能在出厂时便已在固件中完成烧录定义,无法面向新的业务需求进行修改或扩展。然而,对于许多应用场景,固定功能的硬件会因为难以进行资源复用而导致成本提升。FPGA器件因为具有动态可重构的特性,被认为是数字可演化硬件系统一个很好的平台[8]。Xilinx使用硅片堆叠技术设计出了高容量的FPGA,用于满足低功耗、低延时及高带宽的应用需求。

2.1 工程构建

在进行FPGA系统设计时往往需要重用已有的功能模块,于是类似于软件开发库文件的IP核应运而生。IP核通常是预先设计好的电路功能模块,主要被用于ASIC或FPGA系统。Xilinx提供了可连接到高级可扩展接口(Advanced eXtensible Interface,AXI)的通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)Lite。每一个AXI UART Lite IP核都可以实际对应一个串行通信接口,为工业监测设备接入自动化监测系统提供支持。AXI UART Lite IP核可以为异步串行数据传输提供控制器接口。它的设计目的在于和 AXI4-Lite协议实现连接。AXI UART Lite的主要性能和优势[9]如下:

(1)基于AXI4-Lite 规格的AXI 接口;

(2)一个发送通道和一个接收通道(全双工);

(3)16个字符的发送和接收先进先出队列(First Input First Output,FIFO);

(4)单个字符的数据比特位(5~8)数量可配置;

(5)校验位(奇偶或无)可配置;

(6)波特率可配置。

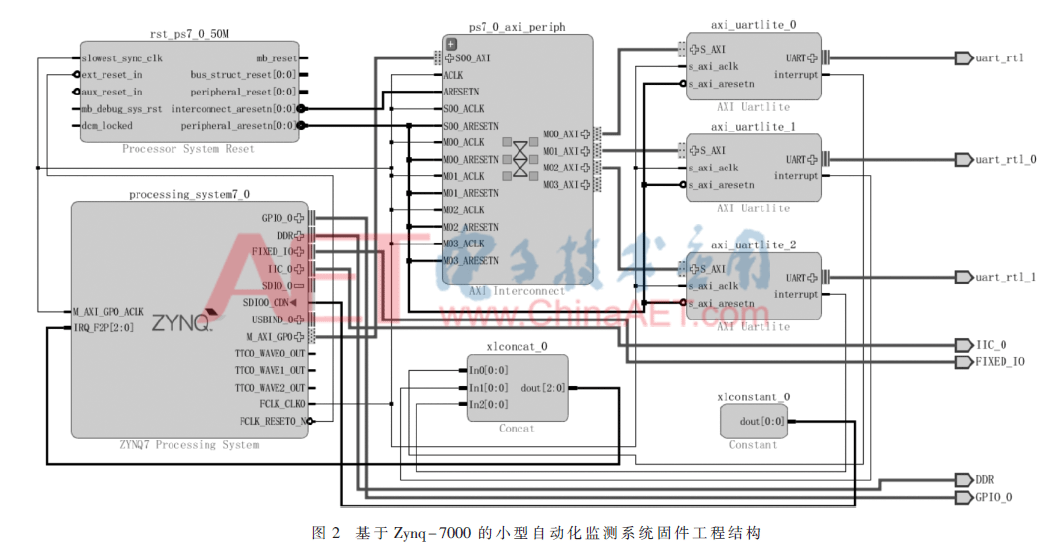

Xilinx提供了Zynq7处理器系统IP封装,用于加速嵌入式系统的设计与配置。在Vivado集成开发环境中搭建基于Zynq-7000的小型自动化监测系统FPGA工程,工程结构如图2所示。工程中添加了ZYNQ7处理器系统模块、3个AXI UART Lite模块以及AXI互联模块等IP核,AXI Interconnect IP负责将一个或多个AXI存储器映射的主器件连接到一个或多个存储器映射的从器件。在进行FPGA系统设计时还预留了部分GPIO接口资源,方便对系统功能进行扩展。

2.2 资源配置

2.2.1 PS端资源配置

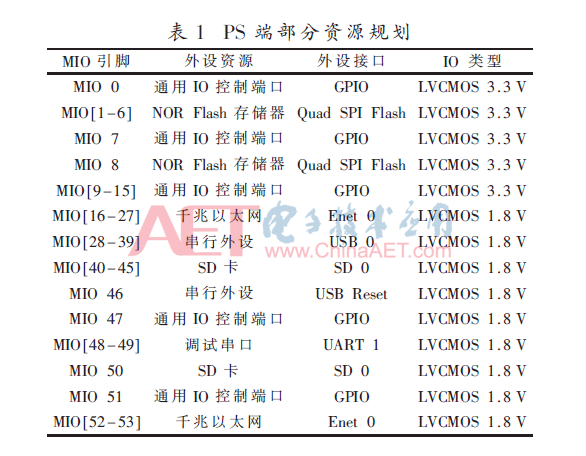

根据实际应用需求配置Zynq XC7Z010处理器系统,并规划XC7Z010的PS端MIO资源。MIO是I/O外设连接的基础。XC7Z010芯片通过MIO最多可以引出54个三态通用输入输出(General Purpose Input Output,GPIO)引脚。这些GPIO引脚都是在程序上可控的,并且支持动态修改配置。它们可以单独配置为输入、输出或中断的功能。PS端部分资源规划结果如表1所示。

2.2.2 PL端资源配置

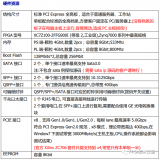

Zynq中的PL主要用于扩展功能。通过使用多个特殊引脚和信号,可以将Zynq-7000内的PS和PL紧密或松散地耦合在一起[10]。XC7Z010主芯片包含用于连接外设和某些特殊功能引脚的IO接口资源。 特殊引脚最主要用于实现复位、状态指示、系统配置、模式配置等功能,通过特定引脚和功能复用引脚来实现。XC7Z010的主要特殊引脚的配置说明如表2所示。

3 PetaLinux工程设计

使用PetaLinux工具构建基于Zynq AP SoC的嵌入式Linux操作系统。PetaLinux工具包括定制的BSP生成工具、Linux配置工具以及软件开发工具。使用这些工具可以实现引导加载程序、Linux内核以及Linux应用程序的灵活配置,有利于开发者在Xilinx处理系统上定制、构建和调配嵌入式Linux解决方案。

3.1 系统顶层配置

基于Zynq工程模板创建PetaLinux工程,导入固件工程生成的硬件描述文件并进行系统顶层配置,系统顶层配置项包括Linux组件选择、自动配置项设置、子系统硬件自动配置项设置、内核引导参数设置、U-Boot设置、镜像文件打包配置等。其中子系统硬件自动配置项设置为必选项,允许自定义系统范围的硬件设置,如:以太网卡设置、Flash设置、串口设置、实时时钟(Real-Time Clock,RTC)芯片设置、SD卡设置等。Petalinux工具将根据系统顶层配置解析硬件描述文件,以便更新设备树所需的硬件信息。

3.2 Linux内核配置

Linux内核主要提供五大功能,分别为虚拟文件系统、网络服务、内存管理、进程管理和设备管理。Xilinx 提供了免费的PetaLinux开发工具,使开发人员可以轻松在Zynq AP SoC上配置、构建和部署Linux系统及应用,提高软硬件设计开发效率。Linux内核配置基于Linux 4.6.0内核进行,主要包括USB串口驱动配置、以太网驱动配置、GSM和CDMA调制解调器的USB驱动配置、Xilinx-uartlite串口驱动配置、DS18B20温度传感器驱动配置、GPIO支持等。PetaLinux工程基于开源的协作软件Yocto创建。Yocto致力于创建可定制的嵌入式产品和统一嵌入式Linux系统的开发标准,它提供了许多模板、工具和方法,使得开发者无需关心硬件体系,避免许多重复工作,从而提高开发效率和产品质量。Linux内核的更新以打补丁的方式实现,内核源码的更新不影响已修改的系统配置项。

3.3 设备树配置

Linux内核通过设备树文件获取板级硬件的细节信息从而加载设备驱动。设备树可以对硬件进行规范化描述,支持多平台内核镜像,具备简化的板卡端口,使用更少的平台描述代码以及更精简的设备驱动代码[11]。PetaLinux设备树配置关联文件主要有pcw.dtsi、plnx_aarch64-system.dts、system.dts、system-conf.dtsi、system-top.dts。这些文件统一由PetaLinux工程自动生成,开发者通过修改system-top.dts文件来满足特定的系统需求。基于Zynq-7000的小型自动化监测系统具备网口调试、RTC时钟支持、温湿度监测、网络数据传输等功能。需要在system-top.dts文件中进行相应节点信息的修改或添加新的硬件描述节点。例如在设备树配置文件system-top.dts中添加RTC时钟硬件描述信息及修改后的网卡芯片节点信息如下:

&i2c0 {

status = "okay";

rtc@51 {

compatible = "nxp,pcf8563";

reg = <0x51>;

};

};

&gem0 {

compatible = "cdns,zynq-gem", "cdns,gem";

status = "okay";

phy-mode = "rgmii-id";

xlnx,ptp-enet-clock = <0x69f6bcb>;

local-mac-address = [00 0a 35 00 1e 53];

};

4 BSP总体测试

在基于XC7Z010的硬件平台中对BSP进行总体测试,设备上电后,处理器自动执行片内BootROM中的代码,初始化CPU和一些外围设备,以便读取烧录在NOR Flash中的BOOT.BIN引导镜像,BOOT.BIN引导镜像加载存储在eMMC上image.ub到DDR3中运行。然后,文件系统中的mystartup.sh脚本启动存储在eMMC中的系统初始化脚本文件,执行系统初始化配置。PetaLinux系统部分启动信息如图3所示。

图3(a)为PL部分扩展的AXI UART Lite模块注册加载信息,在Linux下作为标准串口分别对应设备文件描述符ttyUL1、ttyUL2及ttyUL3。图3(b)为内存技术设备(Memory Technology Device,MTD)驱动加载信息,MTD是用于访问存储介质的Linux的子系统,此处表示NOR Flash存储器,共创建了boot、bootenv、kernel以及spare 4个MTD子分区,其中spare分区为空闲分区,可用于烧录设备唯一序列号。图3(c)为GSM模块USB接口连接检测信息及网口芯片启动状态信息,其中GSM模块对应Linux系统下的设备文件描述符ttyUSB0、ttyUSB1、ttyUSB2、ttyUSB3及ttyUSB4。

5 结论

本文实现一种面向自动化监测系统的BSP设计方法,并完成了面向小型微型自动化监测系统的BSP设计与实践。用于评测BSP功能及性能的硬件平台选用Xilinx Zynq XC7Z010芯片作为硬件系统主控制器,BSP部分针对自动化监测系统应具备的基本功能在嵌入式Linux系统中添加了相应的设备驱动,可充分满足工业监测领域的业务需求。实际测试结果表明,该BSP具有开发便捷、通用性强、便于进行功能扩展和Linux内核升级、运行稳定等特点,验证了基于Zynq-7000的自动化监测系统BSP设计的可行性与正确性,对于工业自动化系统的BSP设计与实现有一定的参考价值和实际指导意义。由于自动化监测系统的功能日益复杂,该BSP设计仍需在实践中不断进行完善。

编辑:hfy

-

Linux

+关注

关注

87文章

11216浏览量

208783 -

监测系统

+关注

关注

8文章

2664浏览量

81225 -

Zynq

+关注

关注

9文章

607浏览量

47109

发布评论请先 登录

相关推荐

当ADC3663的LVDS输出给到ZYNQ-7000的LVDS接收这两者之间可以直连吗?

小型气象自动监测站

zynq7000 BSP无法在u-boot加载运行怎么解决?

zynq7000 BSP无法在u-boot加载运行,为什么?

隧道安全监测自动化系统解决方案

简谈Xilinx Zynq-7000嵌入式系统设计与实现

Xilinx ZYNQ 动手实操演练

Zynq-7000为何不是FPGA?

自动化水质监测系统解决方案

简谈Xilinx Zynq-7000嵌入式系统设计与实现

沙特stc和华为商用核心网自动化实践荣获“年度最佳自动化项目奖”

基于IMX214+ZYNQ XC7Z100的1080P双目视觉智能平台

基于Zynq-7000面向小型微型自动化监测系统的BSP设计与实践

基于Zynq-7000面向小型微型自动化监测系统的BSP设计与实践

评论