今天我们讲述一下如何使用模型添加法去添加相对传输延迟的等长规则,具体的操作步骤如下所示:

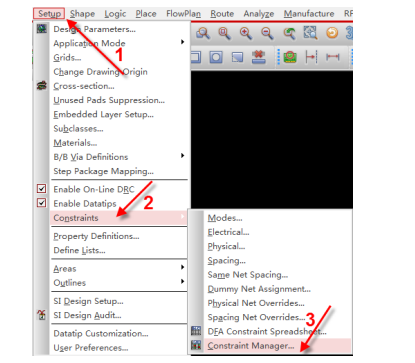

第一步,打开规则管理器,执行菜单命令Setup-Constraints,在下拉菜单中选择Constraint Manager,如图5-99所示,进入到规则管理器中;

图5-99 规则管理器示意图

第二步,进入到规则管理器之后,在CM左侧的目标栏中选择Net,在Net中选择相对传输延迟选项Relative Propagation Delay,如图5-100所示;

图5-100 相对传输延迟设置示意图

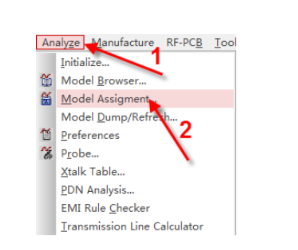

第三步,选中一根需要做等长其中一根信号线,点击鼠标右键,选择SigXplorer进行模型分析,如图5-101所示;

图5-101 模型分析设置示意图

第四步,弹出的如图5-102所示的界面,显示了该网络的链接拓扑结构以及网络的连接关系,如图5-102所示,U7与U15表示是的是元器件,下方的A2与193是器件的管脚标号;

图5-102 信号走线拓扑结构示意图

第五步,执行菜单命令Set-Constraints,设置规则即可,点击之后弹出如图5-103所示的界面,在这个界面进行规则的设定;

图5-103 规则设定窗口示意图

第六步,进入规则设定以后,我们需要选择相对传输延迟,选择Rel Prop Delay选项卡,在规则名称一栏中输入“MG_DDR_D”,From与To的选择框不用手动去填写,在左侧的拓扑结构中直接选择即可,其它设置参数如图5-104所示;

图5-104 规则参数设置示意图

第七步,设置好规则以后,点击Add按钮,在规则窗口Existing Rules中就新添加了一个相对延迟的规则;

第八步,添加好规则以后,需要更新规则管理器,这样规则才会更新到规则管理器中,执行菜单命令File-Update Constraints Manager或者是单击Update CM的按钮,效果也是一致的,更新以后,回到规则管理器,就会出现我们刚才添加的规则,如图5-105所示;

图5-105 约束模板示意图

第九步,上述的操作,就成功添加了一个模型,我们还需要将这个模型应用到其它相同拓扑结构中去,如图5-106所示;

图5-106 应用模板示意图

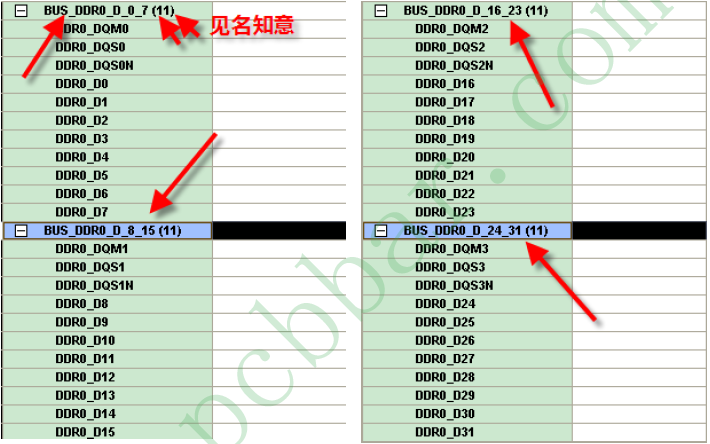

第十步,应用模板以后,所有相同拓扑结构的网络都会自动添加到等长的集合当中,如图5-107所示,这样所有的等长规则就已经全部设定好了;

图5-107 模型添加法完成示意图

第十一步,应用好所有的模型之后,所有的需要等长的信号全部出现在等长列表中,按照直接添加法中的设置一样,设置好目标线,回到PCB界面进行等长即可。

上述,就是在allegro软件中如何通过模型添加的方法,去添加相对传输延迟的等长规则的方法解析

编辑:hfy

-

pcb

+关注

关注

4316文章

22988浏览量

396115 -

拓扑结构

+关注

关注

6文章

323浏览量

39159 -

allegro

+关注

关注

42文章

650浏览量

144945 -

管理器

+关注

关注

0文章

242浏览量

18487

发布评论请先 登录

相关推荐

PCB SI/PI中添加IBIS模型后,sigxplorer中元件模型显示unknown

在Allegro软件中添加xnet的具体步骤

allegro pcb editor规则设置类别优先顺序

Allegro PCB设计时等长设置的一些方法与技巧解析

PCB设计中绕等长线的方法和技巧

allegro软件的绝对传输延迟是什么,绝对传输延迟应该怎么设置呢?

PCB技术:allegro软件中添加xnet的步骤解析

PCB设计中如何实现等长走线

Allegro小技巧 | 如何使用Allegro直接添加相对传输延迟的等长规则

PCB技术:allegro软件中如何通过模型添加相对传输延迟的等长规则

PCB技术:allegro软件中如何通过模型添加相对传输延迟的等长规则

评论