信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。函数信号发生器的实现方法通常是采用分立元件或单片专用集成芯片,但其频率不高,稳定性较差,且不易调试,开发和使用上都受到较大限制。随着可编程逻辑器件(FPGA)的不断发展,直接频率合成(DDS)技术应用的愈加成熟,利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,成本更低,操作更加灵活,而且还能根据要求在线更新配置,系统开发趋于软件化、自定义化。本文研究了基于 FPGA的DDS信号发生器设计,实现了满足预定指标的多波形输出。

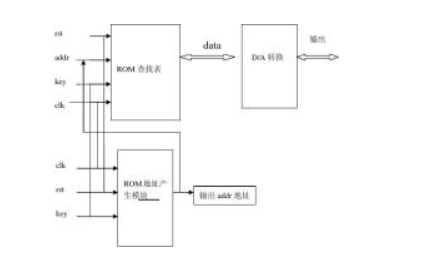

DDS建立在采样定理基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后通过查表读取数据,再经D/A转换器转换为模拟量,将保存的波形重新合成出来。DDS基本原理框图如图1所示。

除了滤波器(LPF)之外,DDS系统都是通过数字集成电路实现的,易于集成和小型化。系统的参考时钟源通常是一个具有高稳定性的晶体振荡器,为各组成部分提供同步时钟。频率控制字(FSW)实际上是相位增量值(二进制编码)作为相位累加器的累加值。相位累加器在每一个参考时钟脉冲输入时,累加一次频率字,其输出相应增加一个步长的相位增量。由于相位累加器的输出连接在波形存储器(ROM)的地址线上,因此其输出的改变就相当于查表。这样就可以通过查表把存储在波形存储器内的波形抽样值(二进制编码)查找出来。ROM的输出送到D/A转换器,经D/A转换器转换成模拟量输出。

设计功能及端口

1.设计实现的功能

用一个8×128的ROM完成对所要显示正弦波形数据的存储,即生成正弦波的波形数据查找表,通过VerilogHDL编写DDS直接数字频率合成代码,在Quartus II与modelsim工具软件的环境中进行设计和仿真,要求能根据相位累加产生的地址并按照不同的频率控制信号(freq)读取ROM波形查找表中的数值做为输出,并正确显示波形。同时还可通过改变相移变量(pha)控制程序从不同的位置开始读取ROM波形查找表中的数据。

2.输入输出端口

input wire clk; //时钟

input wire rst;//复位信号(低电平有效)

input wire [6 : 0] freq;//频率控制信号

input wire [6 : 0] pha;//相移变量信号

input wire key; //使能开关信号(高电平有效)

output wire [7 : 0] data; //ROM查找表数据

功能介绍

1.设计功能模块介绍:

本次设计总体实现的是一个能产生正弦波形的DDS信号发生器,该

DDS信号发生器的程序代码模块主要有以下内容:

(1)ROM地址产生:

当时钟的上升沿到来时,如果复位信号有效,则把地址变量addr清零;否则当使能开关信号key有效时,则将频率控制字写到内部寄存器里,再将频率控制字和上一时刻的地址变量进行相加,将加的结果作为地址输出。另外,还可通过频率控制信号freq控制读取频率,通过相移变量信号pha控制初始读取位置。

(2)ROM查找表:

当时钟的上升沿到来时,如果复位信号有效,则把输出置为零;否则根据ROM地址产生模块产生的地址读取ROM中存储的数值。

另外需通过C语言生成ROM正弦波查找表数据,C语言程序代码如下: #include “stdio.h”

#include “conio.h”

#include “math.h”

main()

{

int i;

float j;

int y;

FILE *fp;

if((fp = fopen(“rom.mif”, “wa”)) == NULL)

exit(1);

for(i = 0; i 《 128; i++)

{

y = 128 * sin(j) + 128;

fprintf(fp, “%d:%d;\n”, i, y);

j += 2 * 3.1416 / 128;

}

fclose(fp);

printf(“Hello, world\n”);

getch();

}

2.系统结构框图:

设计源代码

1.设计源代码:

module DDS(clk,rst,freq,pha,key,data);

input wire clk; //时钟 input wire rst; //复位信号(低电平有效) input wire [6 : 0] freq; //频率控制信号 input wire [6 : 0] pha; //相移变量信号 input wire key; //使能开关信号(高电平有效) output wire [7 : 0] data; //ROM查找表数据

reg [6 : 0] addr; reg [6 : 0] phase; reg [6 : 0] frequency;

always @(posedge clk) begin if(key == 1) begin phase 《= pha; //将相移变量值赋给寄存器phase frequency 《= freq; //将频率控制变量值赋给frequency end end always @(posedge clk or negedge rst) begin if(!rst) begin addr 《= 0; //复位 end else begin if(key == 1) addr 《= phase; //将寄存器phase存储的相值赋给addr else addr 《= addr + frequency; //ROM地址产生 end end rom1 rom_1( .address(addr), .clock(clk), .q(data) ); //实例化调用rom1波形查找表endmodule

验证方案和仿真激励:

`timescale 1 ns/ 100 ps //设置仿真的时间单位和时间精度

module stimulus;

reg clk,rst;

reg[6:0]freq,pha;

reg key;

wire [7:0] data;

initial

begin

freq=7‘d2;

pha=7’d0;

key=1‘b0;

#20 key=1’b1;

#100 key=1‘b0;

end

initial

begin

clk=1’b0;

rst=1‘b1;

#40 rst=1’b0;

#40 rst=1‘b1;

end

always #10 clk=~clk; //时钟翻转

DDS

LXC(.clk(clk),.rst(rst),.freq(freq),.pha(pha),.key(key),.data(data));

endmodule

功能仿真

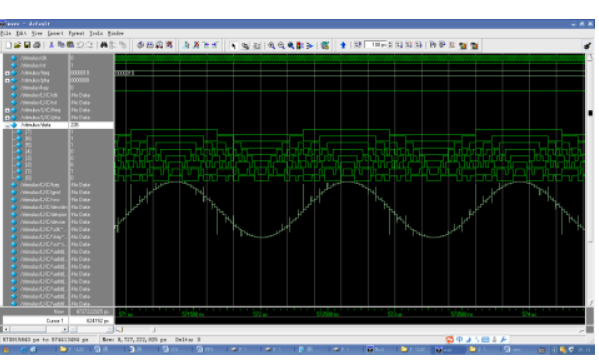

(1)在ModelSim 中对电路设计进行功能仿真

仿真波形如下:

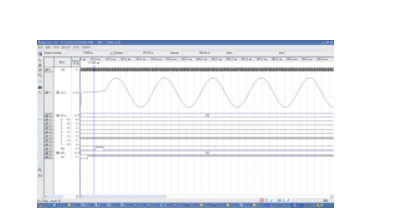

(2)在Quartus II 中对电路设计进行功能和时序仿真 仿真波形如下:

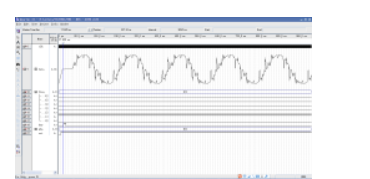

时序仿真波形如下:

仿真分析:通过观察在ModelSim和Quartus II中的仿真波形,分析其完成的功能与设计预期一致,说明本设计能较好的完成设计所需达到的目标。

综合布线与电路图

综合与布局布线:

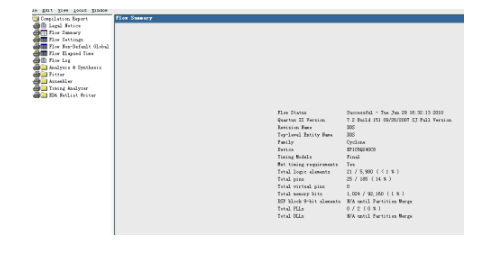

1、下图为综合完并且成功后小窗口上生成的报告,报告中显示出了综合的工程名、引脚及所用的芯片的类型和型号。

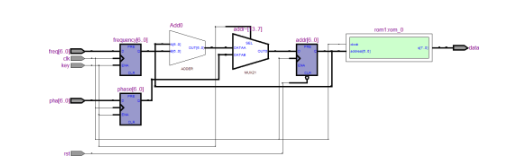

综合完后生成的电路图如下:

综合布局布线报告

综合完后在Quartus生成了一个名为“DDS.map.rpt”的文件,即为综合布局布线报告。

下载代码和引脚分布报告

下载代码

后仿完后在仿真目录下的\simulation\modelsim路径下生成了一个“ DDS_v.sdo”其即为下载代码文件。

引脚分布

综合完后在工程目录下生成了一个“top.pin”文件,其即为引脚分布。

编辑:hfy

-

滤波器

+关注

关注

161文章

7811浏览量

178075 -

存储器

+关注

关注

38文章

7490浏览量

163816 -

DDS

+关注

关注

21文章

634浏览量

152649 -

信号发生器

+关注

关注

28文章

1474浏览量

108755 -

晶体振荡器

+关注

关注

9文章

620浏览量

29122

发布评论请先 登录

相关推荐

基于DDS原理设计信号发生器的方案

基于DDS原理设计信号发生器的方案

评论