无论是为新IC设计电路,还是为具有分立组件的PCB布局设计电路,设计中的导体组之间都将存在耦合电容。您永远无法真正消除直流电阻,铜粗糙度,互感和互电容等寄生现象。但是,通过正确的设计选择,您可以将这些影响减小到不会引起过多串扰或信号失真的程度。

耦合电感很容易发现,因为它以两种主要方式出现:

两个不垂直延伸且参考接地平面的网络可能具有彼此面对的环路(互感)。

提供返回电流路径的每个平面在其参考网络中将具有一些耦合电感(自感)。

由于耦合电容无处不在,因此很难确定。每当将导体放置在PCB或IC布局中时,它们都会具有一定的电容。这两个导体之间的电势差使它们像典型的电容器一样进行充电和放电。这会导致位移电流从负载分量转移出去,并导致信号在高频下在网之间交叉(即串扰)。

使用正确的电路模拟器工具集,您可以对LTI电路中的耦合电容如何影响时域和频域中的信号行为进行建模。一旦设计好布局,就可以从阻抗和传播延迟测量中提取耦合电容。通过比较结果,可以确定是否需要更改布局,以防止网络之间发生不必要的信号耦合。

电路图未明确考虑电路中导体之间的任何耦合电容。这是因为耦合电容取决于以下方面:

几何。导体之间的距离,其横截面积以及布局中彼此面对的区域的大小将决定电路的电容。

介电常数。分隔导体的电介质具有较高的介电常数,并且耦合电容与介电常数成正比。

寄生之间的耦合。单个导体可以具有多个网络的耦合电容。这些电容与其他寄生电容和电感结合在一起以产生复杂的耦合,这可能是频率的复杂函数。

由于耦合可能是频率的复杂函数,因此返回路径和串扰信号可能会产生结果,其频率也与源信号不同。这是由于设计电路,耦合电容和任何其他寄生效应(直流电阻和寄生电感)形成的等效网络的传递函数。

要检查寄生效应如何影响您的电路板,需要使用布局前和布局后仿真工具。布局前模拟要灵活得多,但是由于尚未创建布局,因此它们不能考虑布局中的几何形状。相比之下,正确的数字化布局后仿真工具集将几乎精确地说明寄生现象,但要查明布局中能产生最强耦合的确切部分却很困难。此外,如果不更改布局,就无法浏览不同的耦合电容或电感值来找到可接受的寄生耦合电平。

耦合电容建模工具

因为直到布局完成,布局中的耦合电容才是未知的,因此开始对耦合电容进行建模的位置在原理图中。这可以通过在关键位置添加一个电容器来建模组件中特定的耦合效应来完成。这允许根据电容器的放置位置对耦合电容进行现象学建模:

输入/输出电容。实际电路(IC)中的输入和输出引脚会由于引脚和接地层之间的隔离而具有一定的电容。对于小型SMD组件,这些电容值通常约为10 pF。这是在布局前仿真中要检查的主要点之一。

网之间的电容。在两个承载输入信号的网络之间放置一个电容器将对网络之间的串扰建模。通过可视化受害者和攻击者网络,您可以看到打开攻击者的方式如何在受害者上引发信号。由于这些电容非常小,并且串扰还取决于互感,因此通常仅在布局后执行串扰仿真才能获得最高的精度。

将电容走线回到接地层。即使走线很短,它相对于接地层仍将具有寄生电容,这会导致短传输线上的谐振。

示例:BJT输入引脚处的耦合电容

例如,让我们看一下使用PSpice中的瞬态分析的BJT晶体管的输入引脚与其参考平面之间的耦合。下图显示了一个示例电路,其中包括对短传输线上的寄生进行建模的电路。短线上的电感器和电容器(分别为L1和C1)以及电阻器模拟输出端带有一定电阻的短传输线行为。该系统中的源是范围为0至5 V的脉冲源,其上升/下降时间为2 ns,重复频率为100 ns(10 MHz)。晶体管Q1是40237 NPN晶体管。

放置电容器C2以模拟Q1输入端的pi电容。一个更准确的模型将包括连接到基极的引脚封装电感,但目前我们将重点放在将电容耦合回接地平面上。

耦合电容仿真示意图

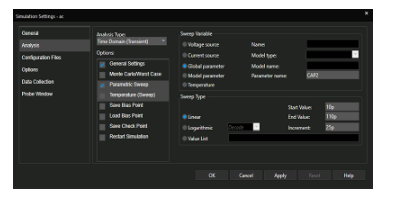

为了检查输入耦合电容如何影响信号行为并可能导致失真,将电容器的值定义为全局参数CAP2。这是通过打开组件属性对话框并将组件值设置为{CAP2}来定义的。需要使用PSpice中“放置零件”菜单中的“ PARAMS”零件将全局参数放置在原理图上。在下图中,我为C2 定义了从10到110 pF 的参数扫描范围(增量为20 pF)。总共给出6条曲线,每个C2值一条。

在PSpice中定义参数扫描范围

现在已经定义了耦合电容范围,是时候运行仿真并检查耦合电容如何影响信号行为了。

时域和频域结果

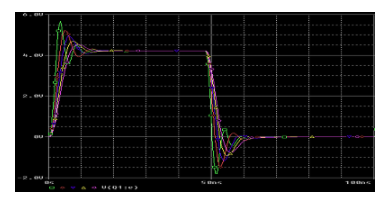

下图显示了10 MHz脉冲流中第一个脉冲的发射极电压的放大图。由于这条短传输线上的共振,我们可以看到明显的振铃。当耦合电容较小(绿色曲线,C2 = 10 pF)时,振铃最大,但随着耦合电容增加(紫色曲线,C2 = 110 pF),振铃变小。

参数扫描产生时域

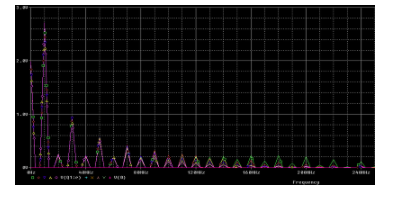

耦合电容的作用是将信号带宽中的高频分量作为位移电流分流到地平面。这可以在频域结果中很好地看到,该结果是通过傅立叶变换计算的。

参数扫描产生频域

在信号带宽的高频端(〜120 MHz或更高),当耦合电容较大时,这些频率的峰值电平会降低。实际上,Q1和C2就像具有高截止频率的低通滤波器一样。请注意,这些信号的拐点频率约为175 MHz,约占总信号功率的75%。我们可以看到,耦合电容开始引起低于该频率的滤波,从而导致信号失真。

添加源阻抗匹配

尽管随着耦合电容的增加,振铃会略有减少,但新型IC往往具有较小的功能,从而具有较小的耦合电容。在这种情况下,这是有问题的,因为瞬态响应导致振幅更大的无阻尼振荡。这凸显了该电路设计中源极终端的需求。如果我们将源的输出阻抗匹配到〜50 Ohms,则可以预期瞬态响应具有较低的幅度,并且可能会出现临界阻尼或过阻尼的振荡。

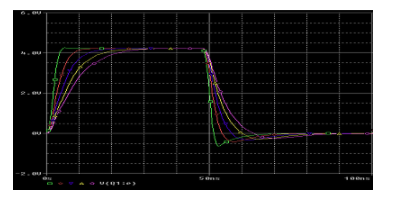

下图显示了一个50欧姆电阻与脉冲电压源(V1)串联以提供源端接的瞬态分析结果。这显着抑制了上升沿的振荡,并使瞬态响应受到严重抑制。在下降沿,仍然存在一些下冲。

参数扫描导致时域带有源终止

根据传输线的电路原理,将产生临界阻尼的源端接电阻是(线路+负载电路)网络的输入阻抗的两倍。端接所需的确切电阻将取决于耦合电容的值。从设计的角度来看,您应该尝试在布局中找到一个可以容纳一定范围内耦合电容值的源电阻,以帮助抑制由于该电路中的瞬态响应而引起的过冲/下冲。

此设计中耦合电容可能突出的其他地方包括:

脉冲驱动器的输出(接地)。

晶体管的输出(接地)。

在晶体管输出和电源引脚之间。

上面的前两点结合起来可以增加互连的电容,从而稍微降低其阻抗。根据电路理论,这与增加晶体管的输入电容时一样,使瞬态响应更接近临界阻尼或更深,成为过度阻尼。在长传输线上,需要将负载阻抗与线路阻抗分开考虑,并且我们需要查看电路反射以确定耦合电容引起的信号行为。

编辑:hfy

-

电容器

+关注

关注

64文章

6971浏览量

108653 -

电感器

+关注

关注

20文章

2651浏览量

73979 -

IC设计

+关注

关注

38文章

1406浏览量

108447 -

耦合电容

+关注

关注

2文章

157浏览量

20848 -

电路模拟器

+关注

关注

3文章

13浏览量

11829

发布评论请先 登录

薄膜射频/微波定向耦合器CP0805:特性、布局与测试全解析

电容在电源电路、音频电路、射频电路中的作用

PCB布局布线的相关基本原理和设计技巧

【「高速数字设计(基础篇)」阅读体验】+第五章去耦电容阅读体验

技术资讯 I 在 Allegro PCB 中如何快速布局

深度解读PCB设计布局准则

PCB布局设计电路中的耦合电容解析

PCB布局设计电路中的耦合电容解析

评论