2021年,代工厂正在加紧各自5nm甚至3nm先进工艺的进程。与此同时,下游芯片商又必须在基于哪种工艺设计下一代芯片做出决定。这就可能影响到在3nm是延续现有的FinFET发展,还是在3nm或2nm采用最新的环栅晶体管技术。未来,随着FinFET能力的耗尽,芯片制造商还必须转移到纳米片FET等更先进的环栅技术…

从2007年高通首款采用65nm工艺的骁龙S1面世,到2021年即将问世的5nm工艺的骁龙875,处理器工艺节点实现了数代演进,性能、功耗、面积和成本都取得巨大发展。

有消息指出,在经过两代7nm节点产品(骁龙855和865)由台积电(TSMC)生产后,2021年,高通首款搭载5nm工艺的骁龙875将转交三星生产。与此同时,苹果的iPhone 12系列和iPad Air 2020中的A14 Bionic,以及华为Mate 40系列中所采用的麒麟9000芯片组,则都采用TSMC最新的5nm工艺生产。

一方面,代工厂正在加紧各自5nm工艺的市场进程,另一方面,下游芯片商又必须在基于5nm工艺设计下一代芯片,还是转向3nm或更先进节点之间做出决定。

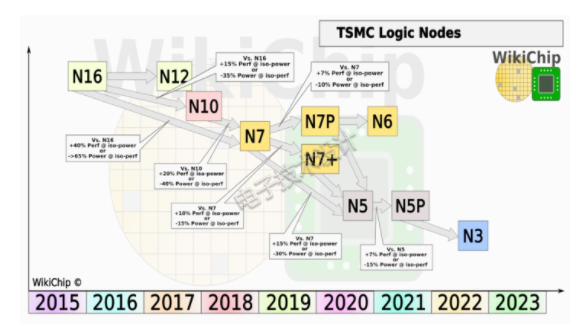

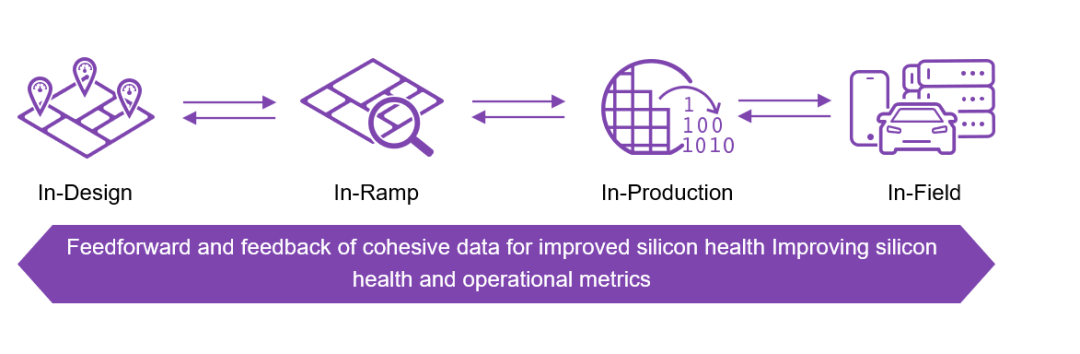

图1:台积电工艺节点路线图。(图片来源:WikiChip)

这就可能影响到在3nm节点是延续现有的FinFET技术发展,还是在3nm或2nm节点采用最新的环栅晶体管(GAAFET)技术。GAAFET是从FinFET演变而来,这种新晶体管可提供更好的性能,但是难以制造、价格昂贵,因此迁移起来就可能很痛苦。从好的方面来说,业界正在开发新的蚀刻、图案化等技术,以帮助向这些节点发展铺平道路。

GAAFET推出的时间表可能因代工厂而异。三星和台积电都采用FinFET生产7nm,也都采用FinFET过渡到5nm。这些工艺节点可同时实现速度和功耗的改进。但是到未来的3nm,三星计划转移到纳米片FET之类的GAAFET技术。同时,台积电则计划首先在3nm推出FinFET,然后在3nm的后期或2nm推出GAAFET。台积电将FinFET延续到3nm的举动合乎逻辑——转向新晶体管可能给客户带来潜在的干扰。但是最终FinFET就行不通了,所以台积电后续只能迁移到环栅。

其他公司也都在开发高级工艺。英特尔目前正在交付10nm产品并在研发7nm(英特尔的10nm与代工厂的7nm类似。同时,中芯国际正在加强16nm/12nm FinFET布局,其10nm/7nm则处于研发中。

所有高级工艺都很烧钱,而且并非所有芯片都需要3nm等高级工艺。实际上,由于成本不断上升,许多人都在探索其他方案。获得扩展优势的另一种方法是将高级芯片集成到同一个封装中。多家公司都在开发新的高级封装类型。

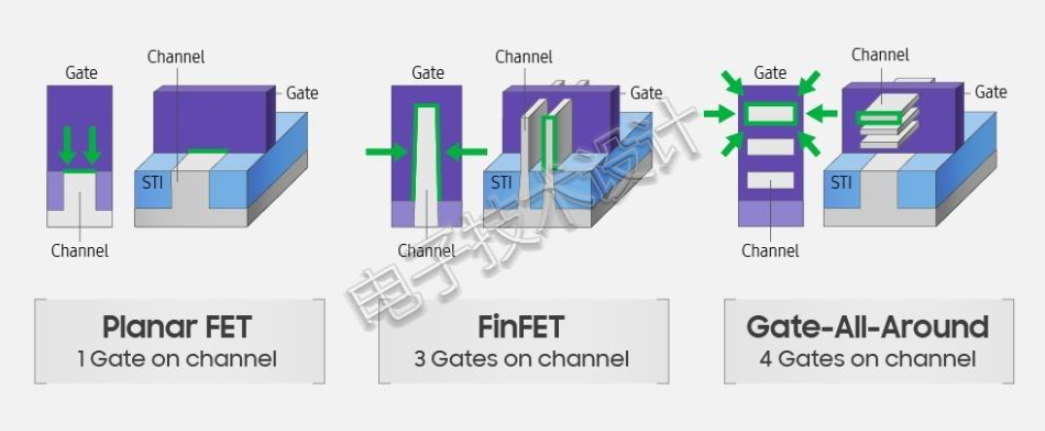

图2:平面晶体管、FinFET与纳米片FET三者对比。(图片来源:三星)

微型化是否走到了尽头?

芯片由三部分组成:晶体管、触点和互连。晶体管用作器件中的开关。高级芯片拥有多达350亿个晶体管。

互连位于晶体管的顶部,由微小的铜布线方案组成,用于将电信号从一个晶体管传输到另一个晶体管。晶体管和互连之间通过中间工序(MOL)连接,MOL由微小的接触结构组成。

IC微型化是推进设计的传统方法,它是将每个工艺节点的晶体管规格缩小,然后将其集成到单个裸片上。

因此,芯片制造商每18到24个月就会通过晶体管密度的提高而推出一种新工艺技术。每种工艺都会取一个数字节点名称。最初,节点名称与晶体管栅极长度尺寸相关。

在每个节点上,芯片的晶体管规格都是微缩0.7倍,这样,在相同的功率下性能就提高40%,面积就减少50%。芯片微型化技术让新的电子产品实现了更多功能。

芯片制造商在迈向各个工艺节点的过程中都遵循这个趋势。但是,到20nm时,传统的平面晶体管就行不通了,这时就发生了很大的改变。从2011年开始,芯片制造商开始向FinFET迁移,从而延续摩尔定律的发展。

然而,FinFET制造起来更烧钱。结果,工艺研发成本猛增。因此,现在完全微缩节点的节奏从18个月延长到了30个月,甚至更长。

在高级节点上,英特尔继续遵循0.7倍的微缩趋势。但是从16nm/14nm开始,其他厂商偏离了这个趋势,这就在市场上造成了一定混乱。

图3:全球高级工艺密度对比。

那时,节点名称变得模糊,不再与任何晶体管规格相关。今天,节点名称只不过是市场术语,这个指标变得越来越没有意义和具有误导性。例如,在5nm或3nm节点,几何图形不再是5nm或3nm。此外,供应商之间的工艺通用性大大降低。对于同一节点,从台积电到三星,还有英特尔,性能不再相同。

高级节点的微型化速度也在放缓。通常,7nm工艺的接触式多晶间距(CPP),其范围从56nm至57nm,金属间距为40nm。到5nm,CPP约为45nm-50nm,金属间距为26nm。CPP是一个关键的晶体管指标,用于度量源极和漏极触点之间的距离。

另外,价格/性能优势不再遵循相同的曲线,因此许多人都认为摩尔定律已走到了尽头。

随着多重图案和EUV成本的增加,摩尔定律的经济方面开始下降。未来,计算能力的提高可能来自新的设计和体系结构而不是微型化。也即未来芯片的计算能力将会继续提高,但其成本的下降速度不一定再与过去相同。

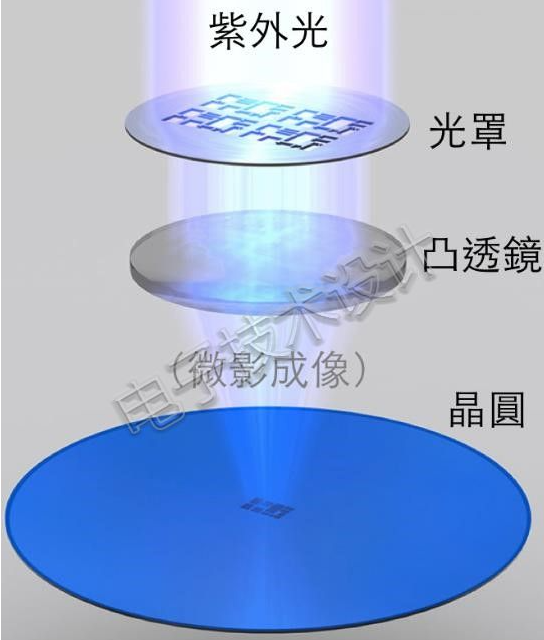

图4:光刻原理。

芯片微型化并没有完全消失。人工智能、服务器和智能手机等对更快芯片的追求推动了高级节点的发展。但是,并不是所有人都需要高级节点。成熟工艺芯片的需求仍然旺盛,例如5G智能手机中所使用的RF IC和OLED驱动器IC,以及面向计算和固态驱动器应用设计的电源管理IC。

FinFET微型化

同时,在芯片微型化方面,多年来芯片制造商都遵循相同的工艺路线图,并且晶体管类型相同。2011年,英特尔在22nm转向FinFET,其他代工厂则是从16nm/14nm开始。

在FinFET中,电流的控制是通过在鳍片的三个侧面分别制造栅极而实现的。每个FinFET具有两到四个鳍。每个鳍片都有不同的宽度、高度和形状。

英特尔第一代22nm FinFET的鳍片间距为60nm,鳍片高度为34nm。然后,在14nm,英特尔FinFET的鳍片间距和高度都变成42nm。

因此,英特尔是通过将鳍片做高做薄来实现FinFET的微型化。

在10nm/7nm上,芯片制造商遵循相同的方法来实现FinFET微型化。台积电在2018年推出了首个7nm FinFET工艺,随后是三星。同时,英特尔在经历了几次延误后于2019年实现10nm出货。

未来,代工行业的竞争将更加激烈。三星和台积电正在加大5nm和各种半节点产品的生产和3nm的研发。

与7nm相比,三星的5nm FinFET技术可将逻辑面积最多增加25%,功耗降低20%,性能提高10%。

相比之下,TSMC的5nm FinFET工艺在相同的功耗下速度提高15%,或者在相同速度下功耗降低30%,逻辑密度为7nm节点的1.84倍。

芯片制造商在7nm和5nm节点进行了一些重大改变。为了对芯片中的关键特征实现图案化,两家公司从传统的193nm光刻技术过渡到了极紫外(EUV)光刻技术。使用13.5nm波长的EUV可以对此进行简化。

但EUV不能解决芯片微缩方面的所有挑战。解决这些挑战需要使用多种技术,除了微型化外,还包括新材料的使用、新型嵌入式非易失性存储器和高级逻辑架构、沉积和蚀刻新方法,以及封装和小芯片设计的创新。

同时,三星和台积电也在默默准备3nm工艺。过去,芯片制造商遵循相同的路线,但是今天却出现了分歧。

3nm可能有几种不同的方案,例如FinFET和环栅。这样客户就可以根据自己的需求在成本、密度、功耗和性能方面做出权衡。

如前所述,三星将推出3nm的纳米片FET。台积电也在对此进行研究,但其计划将FinFET延续到下一代。该公司将在2021年第三季度推出3nm FinFET,环栅则是在2022或2023年左右。对此,下游芯片商必须在成本和技术之间做出折衷。延续FinFET是一条更安全的途径,因此许多芯片商认为台积电是一家低风险供应商。

不过,在某种程度上,环栅技术可提供更高的性能。据悉,与3nm FinFET相比,3nm环栅具有较低的阈值电压,并且有可能将功耗降低15%至20%。但是,由于MOL和后道工序(BEOL)相同,因此性能差异可能会低于8%。BEOL和MOL是高级芯片的瓶颈,接触电阻是MOL中的一个问题。

BEOL用于实现芯片内的铜互连。在每个节点,由于互连尺寸变得越来越小,芯片中的阻容(RC)延迟问题变得严重。虽然FinFET和环栅晶体管类型不同,但它们在3nm可能具有类似的铜互连方案。RC延迟对于两种晶体管都是一个问题。

还有其他挑战。当鳍片宽度达到5nm时,FinFET就行不通了。5nm/3nm FinFET遇到了这个极限。

另外,与其他节点有两个或更多鳍片相比,3nm FinFET可能只有一个鳍片。这就对鳍片的驱动功率提出更高的要求。

将FinFET扩展到3nm的一种方法是使用锗材料作为p沟道。具有高迁移率沟道的3nm FinFET可提高性能,但存在一些集成挑战。

转向纳米片FET

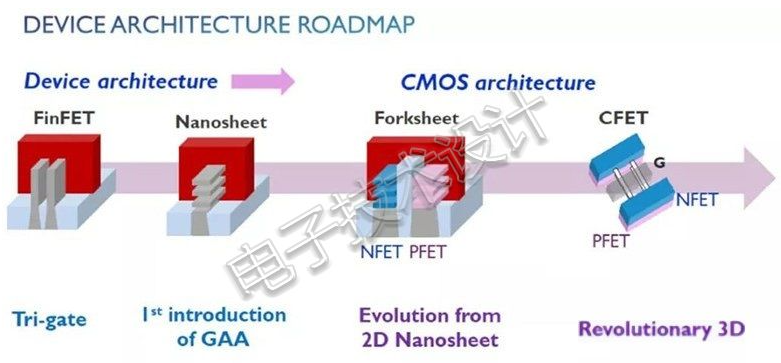

最终,FinFET微型化将会停止,因此芯片制造商必须转移到新的晶体管,即纳米片FET或相关类型。

纳米片FET的势头始于2017年,当时三星推出了3nm的多桥沟道FET(MBCFET)——MBCFET是一种纳米片FET(纳米片FET又是一种环栅晶体管)。其量产定于2022年开始。

台积电也在研究纳米片。与5nm FinFET相比,纳米片提供了适当的微缩,而且具有一些优势。

纳米片FET的侧面基本上是个FinFET,然后将栅极包裹在其周围。纳米片由几个分开的、垂直堆叠的水平薄片组成。每个薄片形成一个沟道。

栅极围绕在每个薄片周围,从而形成环栅晶体管。从理论上讲,由于电流的控制是在这种结构的四个侧面完成的,因此纳米片FET可以提供更高的性能,并且漏电更少。

最初,纳米片会有四个左右的薄片。典型的纳米片宽度为12nm至16nm,厚度为5nm。这就是纳米片不同于FinFET的地方。FinFET用有限数量的鳍片进行量化,这对设计人员提出了一些限制。纳米片的优势在于它可以具有不同的纳米片宽度。根据设计人员的需求,每个器件可以具有不同的宽度。这为设计人员提供了一些自由,并能在性能和功耗方面实现更好的平衡。

例如,具有较宽薄片的晶体管可以实现更大的驱动电流。具有较窄的薄片可以实现较小的器件,但是驱动电流较小。

纳米片与纳米线有关。纳米线是用电线而非薄片形成沟道,沟道宽度有限,因此驱动电流较小。

这就是纳米片FET蒸蒸日上的原因。但是,在3nm左右,这项技术和FinFET面临一些挑战。FinFET面临的挑战是在微缩栅极长度的情况下对鳍片宽度和鳍片轮廓进行量子控制。纳米片面临的挑战是n/p失衡、底片效率、间隔层、栅极长度控制和器件覆盖率。

考虑到这些挑战,纳米片FET将需要时间来加速。

在简单的工艺流程中,纳米片FET开始于在衬底上形成超晶格结构。外延工具在衬底上交替沉积多层硅锗(SiGe)和硅——至少包含三层SiGe和三层硅。然后使用图案化和蚀刻在超晶格结构中形成垂直鳍,超晶格结构和鳍片形成需要精确的CD控制。

随后的工序就比较麻烦了:内间隔层的形成。首先要使超晶格结构中的SiGe层的外部凹陷。这样就能产生小空间而充满电介质材料。内间隔层用于减少栅极到源极/漏极的电容,其制程控制非常关键。

作为解决方案,IBM和东电电子(TEL)最近面向内间隔层和沟道释放过程发表了一种新蚀刻技术。涉及比率为150:1的各向同性SiGe干法蚀刻技术。这项技术可实现精确的内间隔层。

然后就可以形成源极/漏极。再然后,使用蚀刻工艺去除超晶格结构中的SiGe层,所剩下的是构成沟道的硅基层或者片。

高k/金属栅材料沉积在这一结构中。最后,形成MOL和铜互连,从而形成纳米片。

上述即为这个复杂过程的简单描述。但是,与任何新技术一样,纳米片也容易出现缺陷,这需要在晶圆厂进行更多的检查和度量。

更多方案

Imec正在研发更先进的环栅形式,例如CFET和forksheet FET,它们的目标是2nm及以后。

图5:晶体管结构进化路线图。

届时,对于大多数人来说,IC微型化可能就太烧钱了,特别是存在功耗和性能优势的降低。这就是高级封装技术变得越来越有吸引力的原因。不是将所有芯片功能都塞在同一个裸片上,而是将器件分解成更小的裸片,然后将它们集成到高级封装中。

当然,这取决于应用。即使在深亚微米节点,也会出现更多这类活动。有许多公司正在研究它,在决定有哪些内容不能或不希望在5nm上集成,也即研究如何对系统进行分割。

这不是那么容易。此外,还有几种封装方案可以选择,例如2.5D、3D IC,小芯片和扇出,它们各有各的折衷。

图6:TSMC先进封装技术一览。

总结

可以肯定地说,并不是所有人都需要高级节点。但是无疑,苹果、海思、英特尔、三星和高通都需要各种先进技术。

消费者希望拥有性能更高、最新最好的系统。最大的问题是,下一代技术是否能以合适的成本提供任何真正的优势。

编辑:hfy

-

处理器

+关注

关注

68文章

19404浏览量

231013 -

台积电

+关注

关注

44文章

5685浏览量

166959 -

晶体管

+关注

关注

77文章

9744浏览量

138805 -

7nm

+关注

关注

0文章

267浏览量

35363 -

骁龙875

+关注

关注

1文章

32浏览量

9319

发布评论请先 登录

相关推荐

三星3nm工艺投产延迟,新技术让芯片功耗下降约50%

中国晶圆代工巨头台积电,2022年量产3nm芯片

台积电或将在2022年下半年为英特尔代工采用3nm技术的CPU制造芯片

消息称:AMD不太可能将5nm及3nm芯片代工订单转交三星

AMD或将5nm及3nm芯片代工订单交给三星电子

报道称芯片代工商台积电将从2022年开始量产3nm芯片

三星在3nm率先使用GAA 是否更具竞争力

iPhone15系列或采用3nm苹果A17芯片 台积电代工

台积电3nm和5nm同期良率相当,3nm将大量生产

iPhone 16 Pro机型或将搭载3nm工艺的A18仿生芯片

3nm制程代工价格再破新高,高质芯片如何保障?

代工行业竞争愈加激烈 5/3nm芯片战争将开启

代工行业竞争愈加激烈 5/3nm芯片战争将开启

评论