跨越当今市场的许多领域,交织的模拟-数字转换器( ADC的)有几个优点在许多应用。在通信基础设施中,除了数字预失真( DPD )等线性化技术对带宽的要求更高之外,一直在不断寻求更高采样率的ADC以支持多频带,多载波无线电。在军事和航空航天中,较高采样率的ADC允许用于通信,电子监视和雷达的多功能系统,仅举几例。在工业仪器中 对更高采样率ADC的需求不断增长,因此可以更充分,更 准确地测量更高速度的信号。

它‘小号 第一 重要的 ,以 了解 究竟 是什么 交错 的ADC 是 什么。为了更好地理解,最好查看实际发生的情况及其实现方式。然后,我们可以探讨交织的好处。当然,正如许多人所知,没有免费的午餐之类的东西,所以需要评估和评估交错的挑战。

关于交错

当ADC被交错,两个或更多的ADC,以及一个限定的计时关系 被 用于 以 同时 取样 的 输入 信号 和 产生 一个组合的输出信号的结果在采样带宽在一些多个单个ADC的。利用m 个ADC可以将有效采样率提高m倍。

为了简单和易于理解,我们将重点介绍两个ADC的情况。如果两个ADC的采样率分别为fS交错,则最终的采样率仅为2×f s。这两个ADC必须具有时钟相位关系,以使交织正常工作。时钟相位关系由公式1决定,其中n 是特定的ADC,m 是ADC 的总数:

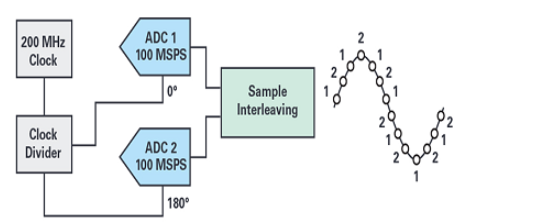

作为一个例子, 2级的ADC,每个具有一个采样率 100的MSPS,被交织 到 达到 一个 样品 率 的 200 MSPS。 在 此 情况下, 等式 1可被用于导出两个ADC,其中时钟的相位关系是由公式2和公式3给出:

现在 认为 的 时钟-相 关系 是 已知的, 该 构造 的 样品可以被检查。图1提供时钟的相位关系的视觉表示 和 所述 样本 结构 的 2 100 MSPS 交错 的ADC。请注意180° 的时钟的相位关系和如何样品被交错。输入波形也可以由两个ADC采样。在这种情况下,交织被执行通过使用一个200MHz的时钟输入端,” š 划分通过 一个 因子 的 2 和 的 所需 相位 的 所述 时钟 到 每个 ADC。

1.两个交错的100 MSPS ADC —基本图。

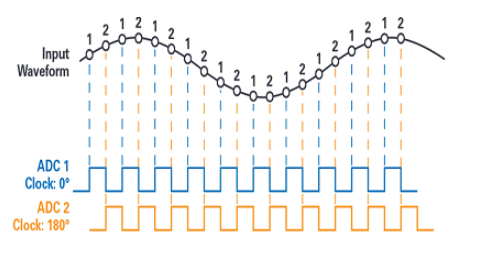

的另一种表示这种概念被示出在图 2。通过交错这些 2级100- MSPS的ADC,该采样率被增加至200 MSPS。这 将 每个 奈奎斯 特区 从 50 MHz 扩展 到 100 MHz,从而使工作带宽 增加 了一倍 。增加的工作带宽带来了 许多 优势 ,以 应用 跨越 多个市场 段。 无线电系统可以增加支持频带的数量,雷达系统可以提高 空间 分辨率, 并且 测量 设备 可以 实现 更大的模拟输入 带宽。

2.两个交错的100 MSPS ADC —时钟和采样

交错的好处

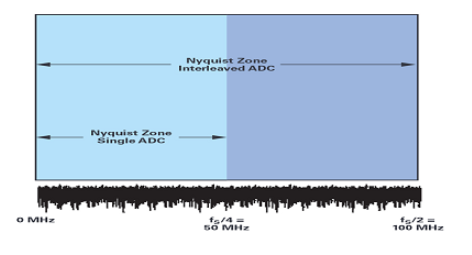

在 利益 的 交织 跨度 跨越 了一系列的市场 细分。 的最期望的有益效果是增加的带宽成为可能由交织ADC的更宽的奈奎斯特区。再一次,使用示例 2级的100- MSPS的ADC交织到创建一个采样率的 200 MSPS,图3给出了一个表示的所述多更宽通过交错两个ADC允许带宽。这为许多不同的应用创造了优势。

3.两个交错的ADC-奈奎斯特区。

随着蜂窝标准增加信道带宽和工作频带数量,对ADC中的可用带宽提出了更高的要求。此外,对于军事应用而言,对更好的空间识别的要求以及后端通信中通道带宽的增加要求ADC拥有更高的带宽。

由于在这些区域需要更多的带宽,因此精确测量这些信号变得更加关键。因此,测量设备需要更高的带宽才能正确获取和测量这些更高带宽的信号。许多设计中的系统要求本质上都领先于商用ADC技术。交织使得弥合这一差距成为可能。

增加的采样率提供了这些应用程序的更多的带宽,但 也 允许 对于 更容易 频率 规划 和 减少 的 的是通常在ADC输入中使用的抗混叠滤波器的复杂性和成本。随着 所有的这些 好处, 一个 具有 以 奇迹“什么 的 价格 我要付钱?” 虽然交错的ADC提供更高的 带宽 和 其他 不错的 收益, 一些 挑战也在这种实现进入图片。

交错的挑战

交错ADC时要注意的一件事是,在输出频谱中出现的杂散是由与交错ADC相关的缺陷引起的。这些缺陷基本上是两个交错的ADC之间的不匹配。四个基本不匹配导致输出频谱中的杂散:偏移不匹配,增益不匹配,时序不匹配和带宽不匹配。

偏移失配

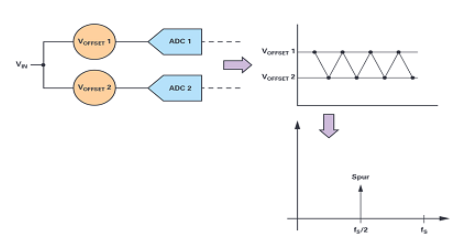

在 最简单 的 这些 来 了解 是 可能 的 偏移 不匹配 的两个ADC之间。每个ADC都有一个相关的直流偏移值。当所述两个ADC被交错和样品采集替代地,回到来回之间的2级的ADC,所述直流偏移的每个连续样品的变化。

图4给出了一个示例,说明每个ADC如何具有自己的直流偏移,以及交错输出如何在这两个直流偏移值之间有效地来回切换。输出以f s / 2 的速率在这些偏移值之间切换,这将导致位于fS / 2的输出频谱中出现毛刺。因为不匹配本身不具有的频率分量和仅在直流,正的频率出现在输出频谱只取决于上的采样频率和将总是出现在一个频率的˚F 小号 / 2。

4.失调失配:当两个ADC交错并在它们之间来回交替采样时,它会改变每个连续采样的dc失调

该 幅度 的 的 骨刺 取决于 该 幅度 的 的ADC之间的偏移不匹配。不匹配越大,杂散越大。为了最大限度地减少了引起骨刺由偏移不匹配,这不是必要的,以完全空直流偏移在每个ADC。这样做会滤除信号中的任何直流成分。此外,它不会对工作 系统 使用 一个 零 IF ( ZIF )架构,其中 的 信号 的内容 是 真实的和 复杂的 ,并 包括 数据 的 直流。

相反, 一种 更 合适的 技术是使一个ADC的偏移与另一个ADC的偏移匹配。选择一个ADC的失调作为基准,另一个ADC的失调设置为尽可能接近该值。偏移值匹配得越好, f s / 2 处的杂散越小。

失配

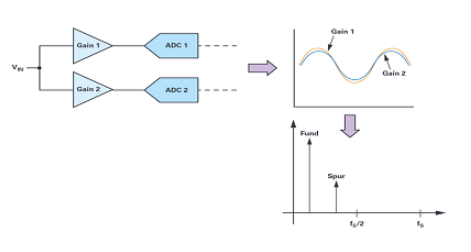

交织时要考虑的第二个失配是ADC之间的增益失配。图5表示两个交错转换器之间的增益失配。在这种情况下,不匹配有一个频率成分。为了观察这种失配,必须有一个信号施加到ADC。

5.交错ADC中的增益失配涉及频率分量。

与偏移失配,没有信号要看到的固有直流两个ADC的偏移量。对于增益失配,除非存在信号并且可以测量增益失配,否则无法看到增益失配。的增益失配将导致在的有关的输出谱的正 的输入频率,如良好的采样率,以及将出现在 ˚F 小号 / 2±˚F IN。

为了最小化由增益失配引起的杂散,采用与偏移失配相似的策略。的增益的中的一个的模数转换器被选择作为参考,和增益的所述其他ADC被设定为增益值尽可能接近地匹配。更好的每个ADC的增益值被匹配到每个其它,较少所得正将在输出光谱。

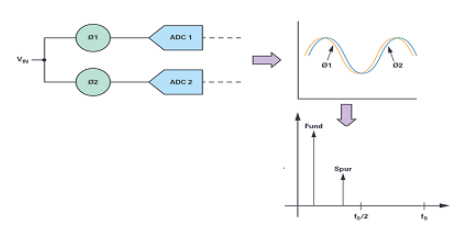

时序不匹配

两个ADC之间的时序失配有两个组成部分:ADC模拟部分的群延迟和时钟偏斜。ADC中的模拟电路具有相关的组延迟,并且两个ADC之间的值可能不同。此外,时钟偏移在每个ADC的孔径不确定性分量,以及与该时钟的精度的分量相即是输入到每个转换器。图 6 显示了ADC中时序不匹配的机制和影响。类似于增益失配骨刺,所述时序不匹配正也是一个功能的输入频率和采样率,并以f s / 2±f IN出现。

6.两个ADC之间的时序不匹配包括两个部分:ADC模拟部分的群延迟和时钟偏斜

为了最大程度地减少杂散,每个转换器模拟部分的群时延都需要使用良好的电路设计技术进行适当匹配。另外,时钟路径设计需要紧密匹配以最小化孔径不确定性差异。最后,必须精确控制时钟相位关系,以使两个输入时钟之间的距离尽可能接近180°。与其他不匹配一样,目标是尝试最小化导致时序不匹配的机制。

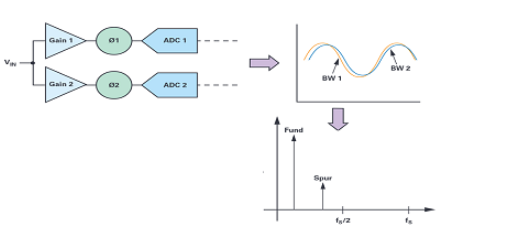

带宽不匹配

在过去的这些不匹配的,带宽错配是可能的最困难,以理解和处理。如所示在图7,带宽失配具有增益和相位/频率分量。这使带宽失配更加困难,因为它包含来自其他两个失配参数的分量。然而,在带宽失配中,我们看到了在不同频率下的不同增益值。另外,带宽具有定时分量,该定时分量使不同频率的信号通过每个转换器具有不同的延迟。

7.带宽不匹配具有增益和相位,频率分量,这使得这种不匹配更难以解决

最小化带宽失配的最佳方法是拥有良好的电路设计和布局实践,以最小化ADC之间的带宽失配。每个ADC匹配得越好,将进一步减少产生的杂散。正如所引起的增益和定时失配骨刺在输出频谱在f 小号 / 2±˚F IN中,带宽不匹配也导致正以相同的 频率。

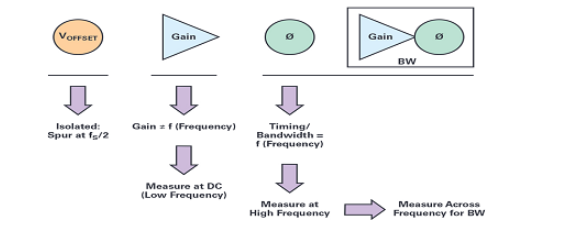

在讨论了导致ADC交织时出现问题的四种不同失配之后,它们之间出现了共同点。四个失配中的三个会在输出频谱中以f s / 2±f IN产生杂散。偏移失配正可以容易地识别,因为它独自居住 在 ˚F 小号 / 2 和 可以 被 补偿 相当容易。的增益,定时,和带宽不匹配所有产生一个正在˚F 小号 / 2±˚F IN中的输出 频谱,所以问题就变成了如何识别每个频谱的贡献。图8给出了一个快速 的视觉 引导 到 所述 过程 的 标识 的 源 的 所述 杂散 从交织ADC的不同错配。

8.交错不匹配的相关性质

如果仅看增益不匹配,则是低频或直流不匹配类型。通过在接近dc的低频下执行增益测量,然后在更高的频率下执行增益测量,可以将带宽不匹配的增益分量与增益不匹配分开。增益不匹配不像带宽不匹配的增益分量那样是频率的函数。类似的方法用于时序失配。在接近dc的低频下执行测量,然后在更高的频率下执行后续测量,以将带宽不匹配的时序分量与时序不匹配分开。

编辑:hfy

-

adc

+关注

关注

99文章

6565浏览量

546606 -

数字转换器

+关注

关注

0文章

238浏览量

27730

发布评论请先 登录

相关推荐

如何用单片ADC和DAC去匹配改善电路呢?

模数转换电路的四个过程

四种常见ADC的特性和应用

DAC或者ADC和基准电压源的位数匹配问题怎么解决

使用ADC12D800RF在fs-2fin处有很强的杂散,为什么?

想使用2片ADS54Jxx系列ADC实现2G采用,照交错采样原理,ADS54JXX系列可以实现吗?

PR735,使用UCC28060的600W交错式PFC转换器

ADC3663的SPI配置管脚连接至FPGA时遇到IO电平不匹配怎么解决?

开发用于将四个ADC通道连接到MCU/MPU的自定义多通道SPI

新品 | 双通道交错PFC级和三相逆变桥Easy模块

交错的ADC是什么 交错ADC时的四个不匹配

交错的ADC是什么 交错ADC时的四个不匹配

评论