简介

版图与电路图比较 (LVS) 验证是片上系统 (SOC) 设计周期中集成电路 (IC) 验证必不可少的组 成部分,但鉴于当今高密度且层次化的版图、不断提高的电路复杂性以及错综复杂的晶圆 代工厂规则,运行 LVS 可能是一项耗时且资源密集的工作。全芯片 LVS 运行不仅会将设计版 图与电路图网表进行比较,而且通常还包含会增加 LVS 运行时间的其他验证,例如电气规则 检查 (ERC) 和短路隔离。

根据设计的复杂性,调试这些设计的 LVS 结果可能同样具挑战性且耗时,进而影响总周转时 间 (TAT) 和计划的流片日程。解决电源接地网络之间的短路问题既困难又耗时,不仅是因为 在这些大型网络中电源接地网格扩展到整个设计规模,还因为造成短路的原因可能有很多。 同样,要确定版图和电路图之间的比较差异可能很困难,因为造成差异的原因可能有很多, 而且跟踪高密度设计中的对应元素可能非常费时费力。如果设计人员想要在尽可能短的收敛 时间内为其高性能设计获得无 LVS 错误的结果,实现有效且高效的 LVS 调试方法至关重要。

LVS 调试的挑战

传统上,LVS 流程主要包含两个步骤:提取和电路比较。首先,使用器件提取和网络连接提 取功能从版图中提取版图网表。然后,将此提取的版图网表与电路图网表进行比较。任一 步骤中发现错误,都可能导致调试时间延长。

由于同一网络被分配多个文本名称,因此可能会出现文本短路 (texted short),导致连接提取 期间提取错误的网络名称。带文本网络之间的短路是提取阶段设计人员面临的主要调试问 题之一。调试这些短路可能很棘手,因为造成短路的原因多种多样,并且短路可能跨越多 个设计层次结构。大型网络(例如电源和接地网络)常常在整个版图区域中扩展,包含许 多多边形并跨越多个层次结构,从而使得短路的电源接地网络难以调试。

将提取的版图网表与源网表进行比较时,也可能出现问题。当今的设计非常复杂,涉及众 多器件和多个层次结构,设计人员常常需要花费相当多的时间来匹配版图和源网表中的等 效元素,最终跟踪并解决差异来源。

无论设计人员是要解决一个很长的电源网络上的短路问题,还是调试比较不匹配问题,都 需要更有效和更高效的调试技术。幸运的是,设计人员可以利用高级调试技术来大大缩短 用于调试 LVS 错误的周转时间。我们来看一些利用 Calibre™ 工具套件更高效地解决复杂 LVS 调试问题的调试技术。

交互式短路隔离

如上所述,由于短路可能有许多不同的原因并且跨越多个设计层次结构,调试当今设计中 的短路可能非常耗时。

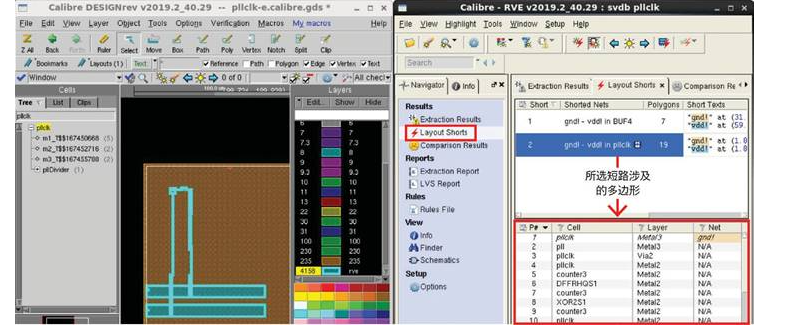

通过启动 Calibre nmLVS™ 运行并启用短路隔离,设计人员可以生成一个短路隔离数据库, 其中包含版图中所有短路的一个全面列表。然后,设计人员可以使用 Calibre RVE™ 交互式 短路隔离 (ISI) 调试流程来显示短路网络中提取的独立多边形,并从关键短路开始,以渐进 顺序系统地调试短路(图 1)。

图 1:设计人员可以选择 并高亮显示一个短路, 然后查看构成该短路的 多边形。

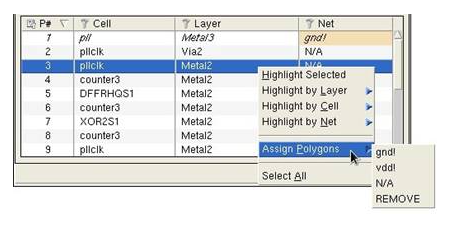

为了演示 Calibre RVE ISI 功能如何让设计人员能 够更快地分析和纠正版图中的短路,下面我们 来详细说明电源接地短路的调试过程。设计人 员选择 “Layout Shorts”(版图短路)结果列表, 然后选择并高亮显示其中一个短路,以在版图 编辑器(例如 Calibre DESIGNrev™ 界面)中查 看涉及的所有多边形。接下来,设计人员根据 其对版图和设计的了解,为每个多边形分配一 个网络标签(vdd! 或 gnd!)。可以在 Calibre RVE 列表中分配标签,或在 Calibre DESIGNrev 显示中标记多边形。当设计人员认为他们已经 确定有问题的多边形时,便为该多边形分配一 个 REMOVE(移除)标签(图 2)。

图 2:设计人员基于其对设计的了解将适当的标签 分配给多边形。

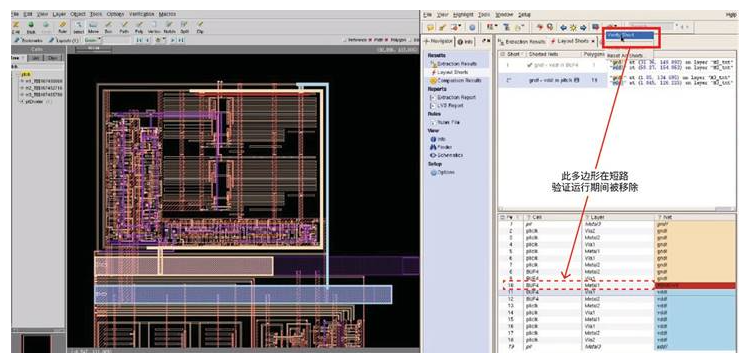

一旦标记完短路中的所有多边形,设计人员便可使用 ISI Verfiy Short(验证短路)选项以虚 拟方式判断,删除标有 “REMOVE” 的多边形是否修复了该短路问题(图 3)。验证短路功能 使用短路数据库中已经存在的提取信息来启动短路验证运行(不是完整的 LVS 运行),以判 断如果短路数据库中去掉标记了 REMOVE 的多边形之后,该短路是否会被去除。这个 “验证 短路” 过程并未真正从版图中删除该多边形,它只是在验证运行期间从短路数据库中移除该 多边形。

图 3:适当分配后,设计 人员可以启动“验证短 路”功能。

如果验证运行表明短路路径不再存在,并且两个网络之间没有其他短路,则该短路将显示 为已虚拟修复。如果验证结果显示,两个网络之间的其他位置仍然存在一个或多个短路, 则会显示一组新的构成短路路径的多边形。设计人员可以继续处理这组新的短路多边形, 直到锁定有问题的短路多边形。在分析的任何阶段,设计人员如果认为自己删除的多边形 不对,可以选择回到原始的短路数据库,然后重新开始分析。

一旦确定了所有有问题的多边形,并且以虚拟方式去除了短路,设计人员就必须使用版图 编辑器从版图中实际移除这些形状,并启动完整 LVS 运行以确认所有短路都已得到纠正。 通过使用 Calibre RVE ISI 流程,设计人员可以更快速且系统性地调试和修复短路问题,而无 需多次运行完整的 LVS。

比较差异

在提取阶段中隔离并移除短路之后,设计人员在比较阶段经常会遇到差异问题。LVS 差异 的例子包括:交叉连接错误、不良实例连接错误、开路错误、短路错误和管脚交换错误。 调试版图和电路图之间的比较差异时,设计人员在分析每个差异的根本原因的同时,通常 还要手动跟踪和管理相应的元素。在高密度设计中,这可能很快变成一种耗时且令人沮丧 的操作。

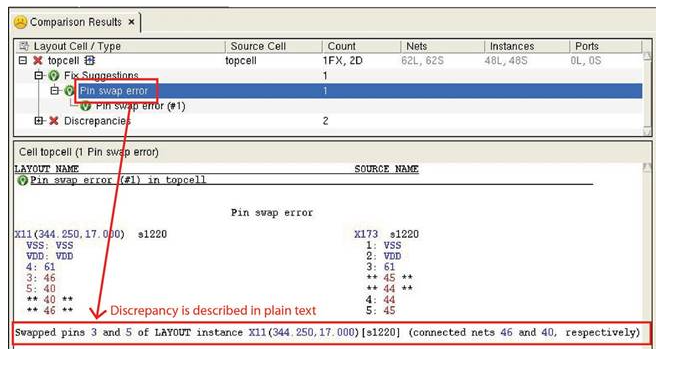

为了加快和改善差异调试,设计人员可以使用 Calibre RVE 修复建议来查看每个差异的可能 来源。这些修复建议会指出差异的可能原因,从而帮助设计人员更快地执行详细的错误分 析。下面通过一个简单的管脚交换错误来说明设计人员如何使用这些修复建议来实现更快 速且更高效的差异调试。

当一个实例的两个版图引脚交叉连接时,即发生管脚交换错误。版图/电路图比较完成 后,设计人员可以查看 Calibre RVE 修复建议以获得调试帮助。每个差异都有清晰的文字说 明(图 4)。

图 4:显示了有关差异可 能原因的简单描述。

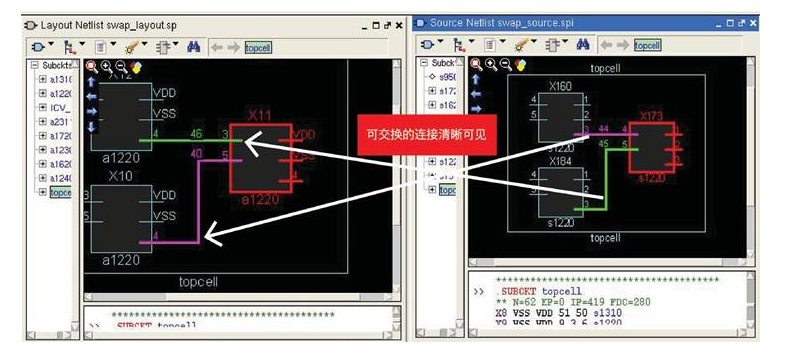

在这种情况下,设计人员可以在版图设计环境和 Calibre RVE 内部电路图查看器(版图和来 源)中高亮显示差异所涉及的实例 (X11) 和两个网络(46 和 40)。通过比较内部电路图视 图,设计人员可以快速直观地看到交换的连接(图 5)。

图 5:内部 RVE 电路图查 看器中的高亮显示有助 于直观地显示差异。

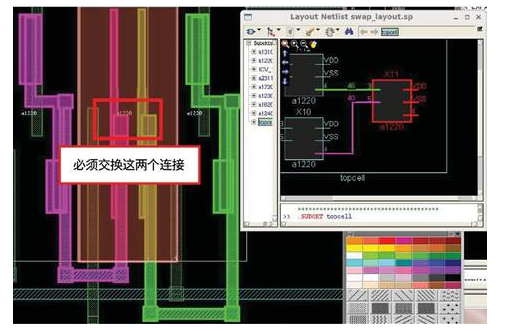

将版图高亮部分与版图电路图查看器 中的高亮部分对照,设计人员可以快 速看到必须纠正的连接(图 6)。

修复建议功能使用简单的语言清楚地 说明差异的根本原因,有助于加快并 简化调试过程。有了这些信息,设计 人员便可使用 Calibre RVE 版图和电路 图查看器更快速、更高效地纠正比较 差异。

图 6:版图与版图电路图查看器中的高亮显示比较显示了 必须交换的连接。

编辑:hfy

-

LVS

+关注

关注

1文章

36浏览量

9943 -

电源接地

+关注

关注

0文章

17浏览量

5987

发布评论请先 登录

相关推荐

更改wifi信号频率实现有且只有2个设备相互通信,避免干扰

如何实现有效的MCU设计

请问如何初始化逐次逼近型ADC以实现有效转换?

非规则矩形电阻在Calibre LVS中阻值提取

稳定高效节能且邻近相关的网络拓扑协议

基于LVS的动态反馈调度算法研究

超详细!使用 LVS 实现负载均衡原理及安装配置详解

安讯士周界防护解决方案实现有效的周界监控和保护

基于Cadence软件DRACULA工具的LVS检查

DS75LVS+ DS75LVS+ - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

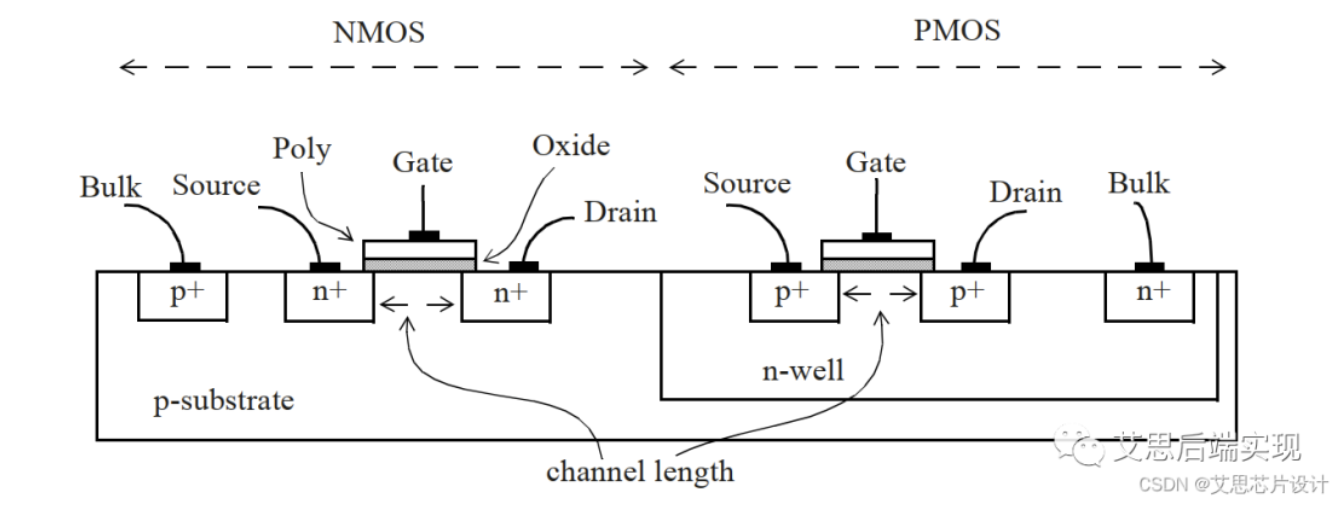

物理验证LVS对bulk(体)的理解和处理技巧

搭建Keepalived+Lvs+Nginx高可用集群负载均衡

实现有效且高效的LVS调试案例解析

实现有效且高效的LVS调试案例解析

评论