本文用的芯片型号为xcku115-flvd1924-1L-i,时钟频率为400MHz。

两个有符号数相加

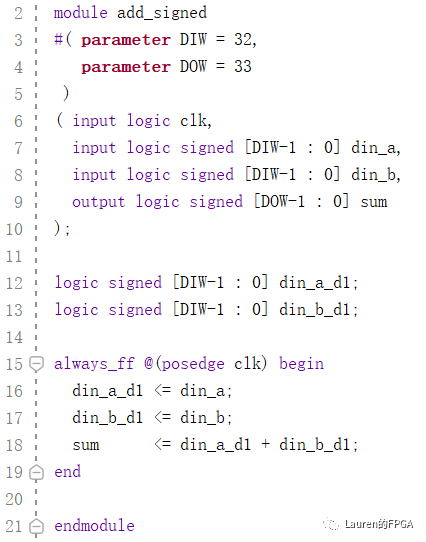

采用RTL代码描述位宽相同的两个数相加或相减,无论是有符号数还是无符号数,Vivado综合后的结果是一致的。以32bit数据为例,相应的代码如下图所示。这里考虑到两个32bit数据相加其结果可能为33bit,同时对于高速设计(时钟频率至少400MHz)为了满足性能,对输入和输出分别添加了流水寄存器。

最终的资源利用率如下图所示。

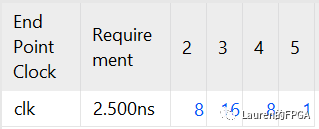

从逻辑级数的角度看,逻辑级数最大为5(有一条),大多数路径为3,如下图所示。

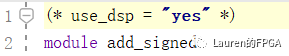

从综合属性角度看,可以通过use_dsp属性使得该加法操作映射到DSP48中,该属性的使用方法如下图所示。

采用DSP48实现时,上述代码可达到完全映射,不会消耗SLICE中的任何资源。假定时钟频率为400MHz,对比使用LUT+FF和DSP48两种实现方式,不难看出后者在时序(逻辑级数降低至1)和功耗方面均有优势。

-

寄存器

+关注

关注

31文章

5386浏览量

121519 -

RTL

+关注

关注

1文章

386浏览量

60061 -

代码

+关注

关注

30文章

4846浏览量

69283

原文标题:两个数相加,三个数相加有什么不同

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ADS4149 datasheet里面描述的register map有两个地方与实际测试出来的结果有出入,求解答

如何把两个数据返回给调用函数

ADS125H01测量结果在两个数值之间跳变,如何规避此类问题?

逻辑异或和逻辑或的比较分析

实现两个单一频率正弦波相加的加法器的芯片选取有什么特殊要求吗?opa2320可以吗?

如何使用SPI或UART连接两个ESP模块?

同相加法器和反相加法器的区别是什么

相同的代码,不同的工程出现定时器抢占的现象怎么解决?

用STM32F1xxx来同时对TIMR4的两个输入脉冲进行脉宽测量,脉冲要如何计算?

传感器之外—两个数据库之间的“连接”查询

采用RTL代码描述位宽相同的两个数相加或相减

采用RTL代码描述位宽相同的两个数相加或相减

评论