PCB占用空间显示了组件在PCB布局中需要放置的位置,并且它们成为生产文件的一部分,一旦您开始生产,这些文件就会发送给制造商。由于您的脚印的一部分成为用于抗蚀剂曝光和蚀刻的模板的一部分,因此它们必须非常精确,直到焊料掩膜的曝光和焊盘间距。

PCB尺寸核对表中包含的内容比组件上焊盘的位置还重要。庭院区域,组件指示符以及更多其他内容都编码在您的组件模型中,一旦您放置了脚印,它们就会直接显示在PCB布局上。如果占位空间不正确,您可能会部分经历制造过程,然后才有人注意到您的电路板存在问题。不要因脚印不正确而措手不及,请使用我们的PCB脚印清单来帮助您避免问题并创建流畅的设计工作流程。

PCB封装问题

出现在电路板布局上的每个组件都将具有PCB足迹。每当您开始一个新项目并跳入一个布局时,在创建单个设计文档之前,原理图符号和PCB封装都必须正确。以我的经验,PCB占位面积比原理图符号更容易出现某种问题。这就是为什么您应该制定PCB足迹清单和验证组件PCB足迹的过程的原因。

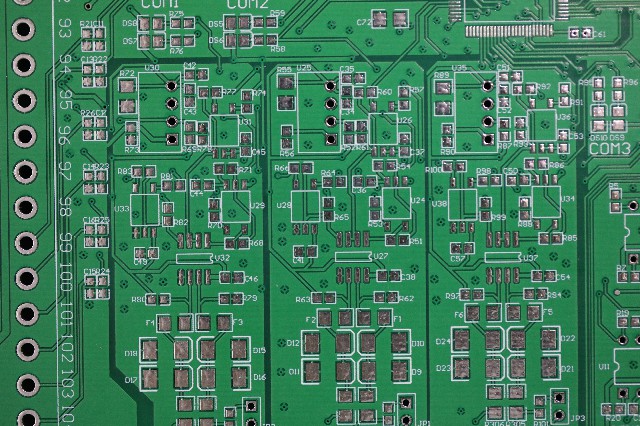

每个PCB的占位面积将包含以下元素:

l垫或孔的位置。这显示了安装垫(用于SMD组件)或安装孔(通孔组件)的位置。这些位置用于焊接,必须准确设计。

l庭院和轮廓。这就像您PCB足迹中的保留区域,即,其他组件不能放置在PCB足迹庭院中。

l参考代号。此字母数字代码在原理图和PCB布局中提供组件的唯一标识符。

lPin-1代号。某些组件可能具有任意方向(例如QFP和DIP组件)。1号插针指示装配者正确的方向。

l机械。一些组件可能具有一些机械元素或悬垂物,这些机械元素或悬垂物可能会延伸到组件上方并与其他组件产生碰撞。一个示例是散热器,该散热器没有与PCB的电气连接。这些可以在PCB布局的机械层中定义。

l链接到3D模型和符号。每个PCB的占位面积都有一个对应的原理图符号,并且可能需要3D模型(通常是STEP文件)。这使您能够以3D形式可视化电路板,并启用组件之间的3D间隙检查。

许多设计师都有一套经过验证的PCB库,用于创建布局,或者使用可处理封装创建的服务。在很多情况下,客户会向图书馆发送带有一些预制PCB足迹的库,以存放专有组件或COTS零件。有时您可能正在使用参考设计中的库。即使这些设计来自一家主要制造商,它们的脚印也不正确,这很常见。无论如何,重要的是要遍历基本的PCB占位核对表,以确保您的占位与在PCB组装期间将要放置在板上的实际组件相匹配。

我的PCB足迹清单

当我们从客户那里收到新的库时,我们会遍历各个组件以确保封装正确无误。我在下面显示的PCB占位清单是一个开始验证占位的好地方。提出一些数据表后,这里是我一直希望在开始PCB布局之前检入组件数据的一些事项。

lMPN /足迹匹配。一些组件以多个包装出售,MPN的末尾将有一个特定的代码来指定特定的包装。您应该检查封装中的包装是否与零件编号中指定的制造商的包装相匹配。

l基本的足迹匹配。这用于快速捕获组件上的不正确足迹。例如,铁氧体,连接器和许多其他组件没有标准化的封装,因此很容易快速发现封装不匹配。

l尺寸在此检查中,您无需发疯,只需使用CAD工具检查基本的焊盘尺寸,焊盘间距和轮廓。如果尺寸不匹配,通常可以发现零部件是否不正确。对于标准化的SMD无源器件,这将帮助您确定在封装中是否设置了错误的封装(例如0603与0402)。

l参考和1针代号。在这里,您可以目视检查这些元素是否在PCB占位面积中。

l生命周期和修订状态。大多数设计人员不检查这些要点。它们仅包括从分销商处找到的组件。为了重复生产,请完全避免使用NRND,陈旧或报废(EOL)组件。另外,请确保组件占用空间与制造商提供的最新版本相匹配。

一旦完成了PCB布局并准备好签核,就应该遍历DFM检查表,以解决任何未解决的可制造性问题。通过这些清单需要在前端花费额外的时间,但是这笔小小的投入可以帮助您防止在后端制造失败(以及客户不满意)。

-

印制电路板

+关注

关注

14文章

957浏览量

40872 -

PCB设计

+关注

关注

394文章

4697浏览量

86095 -

PCB打样

+关注

关注

17文章

2968浏览量

21787 -

华秋DFM

+关注

关注

20文章

3494浏览量

4683

发布评论请先 登录

相关推荐

手机和锂电池纳入第一批工业产品碳足迹核算规则团体标准推荐清单

天合跟踪开拓者1P支架获得必维集团碳足迹认证

美国将中微公司移出制裁清单

北美FCC认证中包含哪些测试项目?

espidf自定义组件明明已经包含了应该包含的内容,为什么编译一直提示未包含?

仿真测试包含哪些内容

PCB设计表面到底应不应该敷铜?

pcb元件布局调整时应注意哪些问题

PCB足迹清单中应包含哪些内容

PCB足迹清单中应包含哪些内容

评论