由域构成的包有四种类型,分别是令牌包、数据包、握手包和特殊包,前面三种是重要的包,不同包的域结构不同,介绍如下:

1、令牌包

分为输入包、输出包、设置包和帧起始包(注意这里的输入包是用于设置输入命令的,输出包是用来设置输出命令的,而不是放数据的)其中输入包、输出包和设置包的格式都是一样的:

SYNC + PID + ADDR + ENDP + CRC5(五位的校验码)

帧起始包的格式:

SYNC + PID + 11位FRAM + CRC5(五位的校验码)

2、数据包

分为DATA0包和DATA1包,当USB发送数据的时候,如果一次发送的数据长度大于相应端点的容量时,就需要把数据包分为好几个包,分批发送,DATA0包和DATA1包交替发送,即如果第一个数据包是DATA0,那第二个数据包就是DATA1。但也有例外情况,在同步传输中(四类传输类型中之一),所有的数据包都是为DATA0,格式如下:

SYNC + PID + 0~1023字节 + CRC16

3、握手包

结构最为简单的包,格式如下:

SYNC + PID

握手包包括 ACK、NAK、STALL以及NYET 四种,其中 ACK 表示肯定的应答,成功的数据传输。NAK 表示否定的应答,失败的数据传输,要求重新传输。STALL表示功能错误或端点被设置了STALL属性。NYET表示尚未准备好,要求等待。

原文标题:USB数据包解析

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

usb

+关注

关注

60文章

7961浏览量

265104 -

数据包

+关注

关注

0文章

265浏览量

24414

原文标题:USB数据包解析

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

mtu配置步骤详解 mtu与数据包丢失的关系

USB协议分析仪的技术原理和应用场景

esp8266怎么做才能每秒发送更多的数据包呢?

使用AT SAVETRANSLINK时UDP数据包丢失怎么解决?

能否在ESP结束之前通过串行端口停止传入的UDP数据包的传输以解析下一个UDP数据包?

请问如何使用AT CIPSEND或AT CIPSENDBUF发送多个数据包?

NONOS如何检查是否实际发送了UDP数据包?

在Fx3控制器中,USB数据包中的数据有效载荷无法正常发送的原因?

如何在AIROC GUI上获取良好数据包和总数据包?

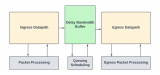

请问高端网络芯片如何处理数据包呢?

STM32H7接收数据包异常,一包接收的数据出现两包发送的内容怎么解决?

DPDK在AI驱动的高效数据包处理应用

USB数据包的解析

USB数据包的解析

评论