常量:

整数:<位宽 num'><进制 b|o|d|h><数字>,例如 4'b1010

x值(不定值)和z值(高阻值,也可用?代替)

x和z可以标识某一位或者某一个数字

4'b10x0,4'bx,4'b101z,4'bz,4'b?

负数:整数最前面加-

下划线:分割数字部分,更加易读(8'b1000_1000)

参数:parameter

parameter 参数名=表达式;

表达式只能是数字或者定义过的参数

变量:

wire型:wire [n-1:0] 数据名;

wire表示信号,常用来表示assign关键字指定的组合逻辑信号

wire型信号可以用作输入,输出

reg型:reg [n-1:0] 数据名;

对存储单元的抽象

常用来表示always模块内的指定信号,常代表触发器

always块内被赋值的每一个信号都必须定义为reg型

memory型:reg [n-1:0] 存储器名[m-1:0];

reg [n-1:0]表示基本存储单元的大小

存储器名[m-1:0]表示基本存储单元的个数,存储空间的容量

对存储器进行地址索引的表达式必须是常数表达式

一个n位寄存器可以在一条赋值语句里进行赋值,而一个完整的存储器不行

运算符及表达式:

基本运算符:+ - * / %

位运算符:~ & | ^ ^~

逻辑运算符:&& || !

关系运算符:< > <= >=

等式运算符:== != (不管x、z,结果可能是不定值)

=== !==(对参数的x、z都进行比较)

移位运算符:<< >>

位拼接运算符:{ },将几个信号拼接起来,例如{a,b[3:0],w,3'b100}

缩减运算符:C =&B;C =|B;C =^B;

优先级别:和c语言差不多,加括号

赋值语句:

1)非阻塞赋值方式(b <= a)

a.块结束才完成赋值

b.b的值不是立刻就改变的

c.在可综合的模块中常用

2)阻塞赋值方式(b = a)

a.赋值语句执行完成后,块才结束

b.b的值在赋值语句执行后立刻改变

c.可能会产生意想不到的结果

简单理解:

非阻塞赋值用了多个触发器,每次时钟到达,所有触发器都触发一次

阻塞赋值连到同一个触发器上,时钟到达,导致所有寄存器被赋值

原文标题: 常量 变量

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

Verilog

+关注

关注

28文章

1351浏览量

110129

原文标题:verilog数据类型 常量 变量

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Verilog与VHDL的比较 Verilog HDL编程技巧

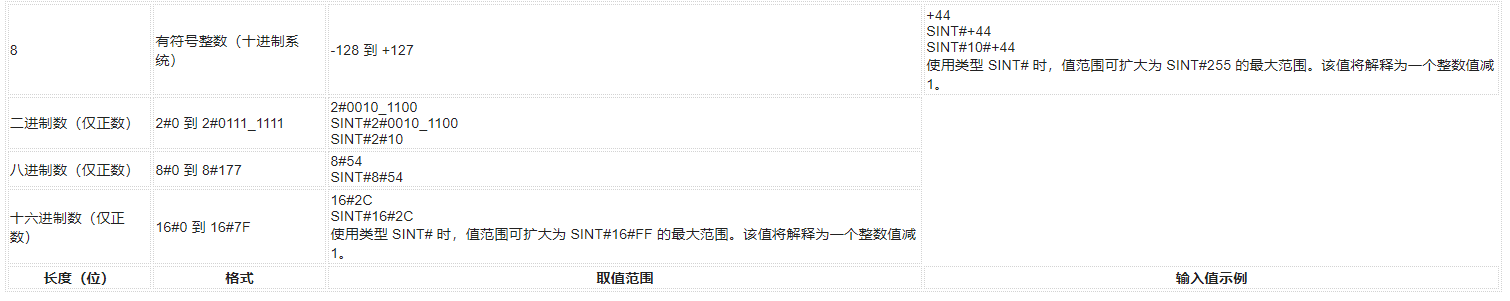

西门子博途新数据类型之:SINT(8位整数)

FPGA编程语言的入门教程

AIC23采集到的数据是应该用什么数据类型来接收?int还是unsigned int?

labview数据类型的取值范围是多少

常见的遥感数据类型有哪些

人体红外传感器的数据类型及工作原理

技术干货驿站 ▏深入理解C语言:基本数据类型和变量

ESP32-S3是否支持修改控制端点数据类型?

C语言数据类型有哪些

verilog的数据类型

verilog的数据类型

评论